Fターム[5F083PR54]の内容

半導体メモリ (164,393) | プロセス (23,970) | メモリセルと周辺回路の同時形成 (5,561) | 周辺回路 (2,703) | ゲート絶縁膜 (656)

Fターム[5F083PR54]に分類される特許

81 - 100 / 656

半導体装置の製造方法

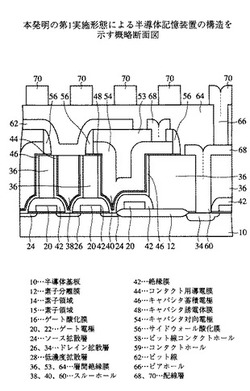

【課題】 半導体記憶装置に係り、特に、高集積化されたDRAMを、少ない工程数で、且つ微細なセル面積で実現できる半導体記憶装置及びその製造方法を提供する。

【解決手段】 半導体基板10に形成されたメモリセルトランジスタと、メモリセルトランジスタのゲート電極20の上面及び側面を覆う絶縁膜42と、ソース拡散層24上に開口したスルーホール40と、ドレイン拡散層26上に開口したスルーホール38とが形成された層間絶縁膜36と、スルーホール40内壁及び底部に形成され、ソース拡散24層に接続されたキャパシタ蓄積電極46と、キャパシタ蓄積電極46を覆うキャパシタ誘電体膜48と、キャパシタ誘電体膜48を覆うキャパシタ対向電極54とを有するキャパシタと、スルーホール38の内壁及び底部に形成され、ドレイン拡散層と接続されたコンタクト用導電膜44とにより構成する。

(もっと読む)

半導体装置の製造方法

【課題】本発明は半導体装置に関する。

【解決手段】本発明は、半導体基板上のセル領域のセルトランジスタ上の層間膜を貫通してコンタクトプラグが形成され、周辺回路領域のトランジスタ上の層間膜を貫通してコンタクトプラグが形成されてなる半導体装置の製造方法であり、セルトランジスタ上の層間膜にコンタクトホールを形成し、その底部側にシリコン膜の下部導電プラグを形成する工程と、その上に金属膜を積層して積層構造のセルコンタクトプラグを形成する工程と、周辺回路用トランジスタ上の層間膜にコンタクトホールを形成し、その内部に金属膜を形成してコンタクトプラグを形成する工程とを具備し、前記セル領域のコンタクトホール内のシリコン膜上に金属膜を形成する工程と前記周辺回路領域のコンタクトホール内に金属膜を形成する工程を同時に行うことを特徴とする。

(もっと読む)

シリコン酸化膜の形成方法、シリコン窒化膜の形成方法、シリコン酸窒化膜の形成方法

【課題】ポリシリコン上において高品質な絶縁膜を形成できる絶縁膜の形成方法を提供する

【解決手段】シリコン酸化膜の形成方法は、基板上にポリシリコン膜を堆積する工程と、

前記ポリシリコン膜の表面を、酸素を含むガスとKrガスを主体とする不活性ガスとよりなる混合ガスにマイクロ波によりプラズマを励起することで形成される原子状酸素O*に曝すことにより、前記ポリシリコン膜の表面にシリコン酸化膜を形成する工程とよりなる。

(もっと読む)

ナンドフラッシュメモリ素子及びその製造方法

【課題】セレクトラインの抵抗を改善すると同時にナンドフラッシュメモリ素子の製造工程を単純化することができるナンドフラッシュメモリ素子及びその製造方法を提供する。

【解決手段】半導体基板上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成された選択トランジスタ及びメモリセル用第1導電膜パターンと、前記第1導電膜パターン上に形成された誘電体膜と、前記メモリセル用第1導電膜パターン上の前記誘電体膜上に形成された第2導電膜パターンと、前記選択トランジスタ用第1導電膜パターンと繋がれて前記第2導電膜パターンより抵抗の低い物質で形成されたセレクトラインと、を含む。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、半導体装置の歩留まりを向上させること。

【解決手段】シリコン基板20に溝20aを形成する工程と、溝20aに充填材30を充填する工程と、溝20aに充填材30が充填された状態で、シリコン基板20に対してウエット処理を行う工程と、ウエット処理の後、充填材30を除去する工程と、充填材30を除去した後、溝20a内に、キャパシタ誘電体膜45aを介してキャパシタの対向電極50pを形成する工程とを有する半導体装置の製造方法による。

(もっと読む)

半導体装置及びその製造方法

【課題】立体構造キャパシタを備えた半導体装置であって、上下部電極に金属若しくは金属化合物を用いるMIM構造で、容量絶縁膜に高誘電体膜を用いるキャパシタにおいて、高誘電率でリーク電流が抑制された信頼性の高いキャパシタを備える半導体装置を提供する。

【解決手段】TiN下部電極102上に酸化ジルコニウム誘電体膜113を形成し、誘電体膜上にTiNを含む上部電極117を形成する際、誘電体膜をALD法で形成し、上部電極を形成する前に誘電体膜形成時のALD法の成膜温度を70℃以上超える温度を付加することなく、第一の保護膜116を成膜する。

(もっと読む)

半導体装置

【課題】小型化が可能な不揮発性メモリを備えた半導体装置を提供する。

【解決手段】基板901上に画素と不揮発性メモリとを備え、不揮発性メモリは、基板901上に形成される半導体活性層と、半導体活性層上に形成される絶縁膜923と、絶縁膜923上に形成されるフローティングゲイト電極907と、フローティングゲイト電極907を酸化して得られる酸化膜908,915,922と、酸化膜908,915,922に接して形成されるコントロールゲイト電極929と、を備え、画素と不揮発性メモリとは、基板901上に一体形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリを有する半導体装置の性能を向上させる。

【解決手段】スプリットゲート型の不揮発性メモリのメモリゲート電極MGとp型ウエルPW1との間および制御ゲート電極CGとメモリゲート電極MGとの間には、絶縁膜5が形成されている。この絶縁膜5のうち、メモリゲート電極MGの下面と半導体基板1の上面との間の部分は、酸化シリコン膜6a,6cと酸化シリコン膜6a,6cに挟まれた窒化シリコン膜6bとを有している。絶縁膜5のうち、制御ゲート電極CGの側面とメモリゲート電極MGの側面との間の部分は、酸化シリコン膜6a,6cと酸化シリコン膜6a,6cに挟まれた空洞CAVとを有し、窒化シリコン膜6bを有していない。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリを有する半導体装置の性能を向上させる。

【解決手段】スプリットゲート型の不揮発性メモリのメモリゲート電極MGとp型ウエルPW1との間および制御ゲート電極CGとメモリゲート電極MGとの間には、絶縁膜5が形成されている。この絶縁膜5のうち、メモリゲート電極MGの下面と半導体基板1の上面との間の部分は、酸化シリコン膜9a,9bと酸化シリコン膜9a,9bに挟まれた窒化シリコン膜10aとを有している。絶縁膜5のうち、制御ゲート電極CGの側面とメモリゲート電極MGの側面との間の部分は、酸化シリコン膜6aからなり、窒化シリコン膜10aを有していない。

(もっと読む)

半導体装置の製造方法

【課題】メモリセル領域と周辺回路領域の双方におけるMOSトランジスタの最適化が可能な半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、サイドウォールを側壁に有するゲート電極を含むMOSトランジスタを、半導体基板1上のメモリセル領域及び周辺回路領域に備えた半導体装置の製造方法であって、前記サイドウォールを形成した後に、選択エピタキシャル成長法により、前記半導体基板1上面にシリコン層10を形成する工程を備え、前記シリコン層10を形成した後に、少なくとも前記周辺回路領域をマスク20bで覆い、エッチングにより、前記メモリセル領域内のMOSトランジスタTr1のサイドウォール9cを薄化する工程を採用する。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】容量絶縁膜である強誘電体のアニール工程を経ても、PchMOS型トランジスタのVth変動を抑制することができる半導体記憶装置およびその製造方法を提供すること。

【解決手段】半導体基板1上に形成され、P型不純物が導入されたゲート電極を有するPchMOS型トランジスタ4と、前記PchMOS型トランジスタ4の上方を覆うように、前記半導体基板1上に形成された第1の水素バリア膜8と、前記第1の水素バリア膜8上に形成され、容量絶縁膜として強誘電体を用いた強誘電体キャパシタ7と、前記強誘電体キャパシタ7の上方および側方を覆い、前記強誘電体キャパシタ7の周縁部において前記第1の水素バリア膜8と接続する第2の水素バリア膜14とを備え、前記第1の水素バリア膜8は、シリコン元素、水素元素、およびシリコン元素よりも水素元素を脱離しにくい第3の元素を含む。

(もっと読む)

半導体記憶装置および半導体記憶装置の製造方法

【課題】周辺回路領域の素子の寿命が劣化するのを抑制しつつ、浮遊ゲート電極と制御ゲート電極とのカップリング性を確保する。

【解決手段】シリコン基板11は、セル領域および周辺回路領域が設けられている。トンネル絶縁膜12は、セル領域および周辺回路領域のシリコン基板11上に形成されている。浮遊ゲート電極膜13は、セル領域および周辺回路領域のトンネル絶縁膜12上に形成されている。電極間絶縁膜16は、セル領域の浮遊ゲート電極膜13上に形成されている。シリコン酸化膜14および電極間絶縁膜16は、周辺回路領域の浮遊ゲート電極膜13上に形成されている。制御ゲート電極膜17は、セル領域および周辺回路領域の電極間絶縁膜16上に形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】周辺回路の抵抗素子の抵抗部の厚さに依らずにメモリセルトランジスタの浮遊ゲートの厚さを自由に設定することのできる半導体装置、およびその製造方法を提供すること。

【解決手段】基板上の抵抗素子およびスタックド・ゲート型のメモリセルトランジスタを含む半導体装置を提供する。前記抵抗素子は、抵抗として機能しない非導通層、および前記非導通層上に第1の絶縁膜を介して形成された抵抗として機能する導通層を含む。前記メモリセルトランジスタは、第1の浮遊ゲートを含む浮遊ゲートを有する。前記非導通層と前記第1の浮遊ゲートは、同じ材料からなる。

(もっと読む)

半導体素子用パターン構造物の形成方法

【課題】ラインパターン構造物の形成方法を提供すること。

【解決手段】ラインパターン構造物及びその形成方法において、ラインパターン構造物は切断部位を含むライン形状を有する少なくとも1つの第1ラインパターンを含む。最外郭に位置する前記第1ラインパターンと隣り合って前記第1ラインパターンと平行した延在ラインと、前記第1ラインパターンの切断部位と隣接する領域で前記第1ラインパターン方向へ向かうように前記延在ラインから突出された少なくとも1つの突出パターンを含む2つの第2ラインパターンを含む。前記ラインパターン構造物は不良が減少し、簡単な工程を通じて形成されてもよい。

(もっと読む)

半導体集積回路

【課題】 不揮発記憶保持用途の電界効果トランジスタと、論理演算用途の電界効果トランジスタの製造工程を別々に設けることなく前記2用途の電界効果トランジスタを同一半導体基板上に同一構造に作製できるようにする。

【解決手段】 ゲート絶縁構造体12に記憶保持材料を含むnおよびpチャネル型電界効果トランジスタで半導体集積回路のメモリ回路とロジック回路の両方を構成し、ゲート絶縁構造体に記憶保持材料を含むnおよびpチャネル型電界効果トランジスタのゲート-基板領域間に印加する電圧の大きさと印加タイミングを制御することによって、論理演算状態と記憶書込み状態と不揮発記憶保持状態を電気的に切り替える。

(もっと読む)

半導体装置、その製造方法

【課題】高集積化が可能な半導体装置、その製造方法を提供する。

【解決手段】半導体素子は、素子領域内の半導体基板11に離間して設けられた1対の第2拡散層215と、1対の第2拡散層215間の素子領域表面上に設けられた第1絶縁膜111bと、第1絶縁膜111b上に設けられた第1ゲート電極112bとを備える。また、第1ゲート電極112bのゲート幅方向に関して素子領域上から溝型素子分離絶縁膜12上に延在するように第1ゲート電極112bの一部上に設けられた第2絶縁膜113bと、第1ゲート電極112b上および第2絶縁膜113b上に設けられた第2のゲート電極114bとを備える。第2のゲート電極114bは、ゲート幅方向の少なくとも一方側の端部が溝型素子分離絶縁膜12上の第2絶縁膜113bに対して素子領域側に後退している。

(もっと読む)

不揮発性半導体記憶装置とその製造方法

【課題】シリサイド層をゲート電極の一部に含む不揮発性半導体記憶装置において、シリサイド層の膜厚を制御することができる不揮発性半導体記憶装を提供する。

【解決手段】不揮発性半導体記憶装置は、チャネル半導体層上に、ゲート絶縁膜12、浮遊ゲート電極膜13、電極間絶縁膜14および制御ゲート電極15が順に積層されるメモリセルトランジスタMTを有する。制御ゲート電極15は、電極間絶縁膜14上に、半導体膜151、シリサイド相変化抑制膜152およびシリサイド膜154を順に積層した構造を有する。また、シリサイド相変化抑制膜152は、C,F,Nのうちの少なくともいずれか1つの元素が、1×1020〜5×1021[atom/cm3]の濃度範囲で添加された多結晶シリコン膜によって構成される。

(もっと読む)

不揮発性記憶装置およびその製造方法

【課題】選択ゲート電極の側壁にメモリゲート電極を有する不揮発性記憶装置を微細化することができる技術を提供する。

【解決手段】選択ゲート電極CGをダミーパターンの側壁にサイドウォール形状で形成することで、メモリゲート電極MGが選択ゲート電極CGの両壁に形成されなくなり、フォトマスクの位置ずれを考慮する必要がなくなる。また、選択ゲート電極CGをサイドウォール状に形成することで、選択ゲート電極CGのゲート長が縮小しても、選択ゲート電極CGを構成する導電膜の膜厚により精度よく制御することを可能とする。

(もっと読む)

半導体装置の製造方法

【課題】簡便な方法でキャパシタ容量の増大を図り、また、キャパシタと同層に形成されるコンタクトプラグの製造を容易とする。

【解決手段】メモリセル部の層間絶縁膜(10,20)にバリア膜とメタル膜の二層構造のコンタクトプラグをいったん形成し、その上に層間絶縁膜(21,22)を積層し、コンタクトプラグ上面を露出する開口を形成し、メタル膜を選択的に除去した後、残存するバリア膜と一体となったキャパシタの下部電極を形成する。周辺回路部では、上層配線31と下層配線6Bとを接続するコンタクトプラグを2段(41、42)とする。

(もっと読む)

半導体装置およびその製造方法

【課題】トレンチ内に埋め込まれたシリコン層と複数のトレンチ間の半導体基板上に形成されたシリコン層とを同じイオン注入を行ない導電層とすること。

【解決手段】半導体基板10に複数のトレンチ30と、前記複数のトレンチ間の前記半導体基板上に第1キャパシタ絶縁膜22を介し第1シリコン層24と、を形成する工程と、前記複数のトレンチ内に埋め込み絶縁膜36を埋め込む工程と、前記埋め込み絶縁膜を前記複数のトレンチの側面に第2キャパシタ絶縁膜33が残存するように除去し、前記埋め込み酸化膜内に凹部を形成する工程と、前記凹部内の前記第2キャパシタ絶縁膜上と前記複数のトレンチ間の前記第1シリコン層上とに第2シリコン層40を直接形成する工程と、前記凹部内および前記第1キャパシタ絶縁膜上に形成された前記第2シリコン層内に不純物を同時にイオン注入する工程と、を含むことを特徴とする半導体装置の製造方法。

(もっと読む)

81 - 100 / 656

[ Back to top ]