Fターム[5F092AA07]の内容

Fターム[5F092AA07]の下位に属するFターム

耐熱性向上、温度特性向上 (183)

機械的強度向上 (6)

耐圧向上 (13)

Fターム[5F092AA07]に分類される特許

1 - 20 / 28

半導体装置の製造方法

半導体記憶装置およびその製造方法

【課題】MTJ素子内における層間の短絡を抑制し、かつ、MTJ素子を構成する磁性層の劣化を抑制した半導体記憶装置およびその製造方法を提供する。

【解決手段】本実施形態による半導体記憶装置は半導体基板を備える。磁気トンネル接合素子は、2つの磁性層と該2つの磁性層間に設けられたトンネル絶縁膜とを含み、半導体基板の上方に設けられている。側壁膜は、磁気トンネル接合素子の側面の上部に設けられている。フェンス層は、導電性材料を含み、側壁膜の側面および磁気トンネル接合素子の側面の下部に設けられている。保護膜は、絶縁体からなりフェンス層の側面に設けられている。フェンス層の上面および保護膜の上面は、側壁膜の上面よりも低く、かつ、トンネル絶縁膜よりも高い位置にある。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】MTJ素子内における層間の短絡を抑制し、かつ、MTJ素子を構成する磁性層の劣化を抑制した半導体記憶装置およびその製造方法を提供する。

【解決手段】本実施形態による半導体記憶装置は、半導体基板を備える。磁気トンネル接合素子は、2つの磁性層と該2つの磁性層間に設けられたトンネル絶縁膜とを含み、半導体基板の上方に設けられている。側壁膜は、磁気トンネル接合素子の側面の上部に設けられている。フェンス層は、導電性材料を含み、側壁膜の側面および磁気トンネル接合素子の側面の下部に設けられている。フェンス層の頂点は、側壁膜の頂点よりも低く、かつ、トンネル絶縁膜よりも高い位置にある。

(もっと読む)

耐食性スペーサ層を備え、より高い信号雑音比を有するCPP−GMRセンサ

【課題】耐食性スペーサ層を備え、より高い信号雑音比を有するCPP−GMRセンサを提供する。

【解決手段】膜面垂直通電(CPP)型巨大磁気抵抗効果(GMR)センサのスペーサ層を形成する材料の電気抵抗と耐食性を増大させるための方法と装置。スペーサ層および、それゆえCPP−GMRセンサの抵抗を大きくすることにより、より大きな電圧をセンサにかけることができ、信号対雑音比をより高くすることができる。スペーサ層の耐食性を高めることにより、製造中にスペーサ層を腐食性材料に曝す影響が最小限となる。たとえば、スズを銀に添加して金属合金スペーサ層を形成すれば、このスペーサ層の耐食性とCPP−GMRセンサの電気抵抗は、銀のみからなるスペーサ層の場合より増大する。Ag−Sn合金により、より大きな電流がセンサを流れ、これによって信号対雑音比が増大する。

(もっと読む)

薄膜磁気センサ及びその製造方法

【課題】水分透過量が小さいSi系絶縁膜が回路表面に形成されており、Si系絶縁膜の密着性及び耐クラック性に優れた薄膜磁気センサ及びその製造方法を提供すること。

【解決手段】以下の工程を備えた薄膜磁気センサの製造方法及びこの方法により得られる薄膜磁気センサ。(1)基板表面に薄膜ヨーク、GMR膜、電極及び配線を備えた素子部を形成する素子部形成工程。(2)少なくとも電極の表面の全部又は一部を含む領域(薄膜ヨーク、GMR膜及び配線の表面を除く)にフォトレジスト膜を形成するフォトレジスト膜形成工程。(3)基板の表面にAl2O3膜を形成するAl2O3膜形成工程。(4)Al2O3膜の表面に、Cat−CVD法を用いてSi系絶縁膜を形成するSi系絶縁膜形成工程。(5)フォトレジスト膜、並びに、フォトレジスト膜の上に形成された余分なAl2O3膜及びSi系絶縁膜を除去する除去工程。

(もっと読む)

磁気メモリチップを有する半導体装置の製造方法

【課題】アセンブリ段階において外部磁場から磁気メモリチップを保護する。

【解決手段】主面に磁気メモリ素子および複数のワイヤボンドパッドが形成された磁気メモリチップを準備する。シリコンより高透磁率を有する第1の磁気シールド板を磁気メモリチップの主面に搭載する。磁気メモリチップをリードフレームのダイパッド上に搭載しダイアタッチフィルムにより接着する。磁気メモリチップのワイヤボンドパッドとリードフレームのリードとをワイヤで電気的に接続する。磁気メモリチップ、磁気シールド板、ワイヤ及びリードの一部を樹脂により封止する。複数の磁気メモリチップを有するシリコンウェハを準備し、シリコンウェハの裏面を研削することによりシリコンウェハを所定の厚さまで薄くしてダイアタッチフィルムを張り付けた後にシリコンウェハをダイシングして各々がダイアタッチフィルムをその裏面に有する複数の磁気メモリチップを形成する。

(もっと読む)

記憶素子及び記憶装置

【課題】外部放射線に対し耐性を有し、誤動作なく安定した動作する信頼性の高い記憶素子の提供。

【解決手段】記憶素子は、情報を磁性体の磁化状態により保持する記憶層と、記憶層に記憶された情報の基準となる磁化を有する磁化固定層と、記憶層と上記磁化固定層の間に設けられる非磁性体による中間層とを有する。そして記憶層、中間層、磁化固定層を有する層構造の積層方向に流れる電流に伴って発生するスピントルク磁化反転を利用して記憶層の磁化を反転させることにより情報の記憶を行うとともに、記憶層は、Bを含有する強磁性層を含み、Bにふくまれる10Bの同位体比率が、自然界における19.9%よりも低くなっている。

(もっと読む)

磁気抵抗素子の製造方法及び製造装置

【課題】エッチングに用いられるハロゲン系成分による素子の腐食を防止することが可能な磁気抵抗素子の製造装置及び製造方法を提供すること

【解決手段】本発明の磁気抵抗素子10の製造方法は、基板上に強磁性材料からなる第1の強磁性層13を形成する。酸化マグネシウムからなる絶縁層14は、第1の強磁性層13上に形成される。Fe及びCoの少なくとも一方を含有する第2の強磁性層15は、絶縁層14上に形成される。ハロゲン系元素を含むプラズマによるエッチングは、基板11上に第1の強磁性層13、絶縁層14及び第2の強磁性層15が積層された積層体に対して施される。積層体は、H2Oを含むプラズマであるH2Oプラズマに曝露される。

(もっと読む)

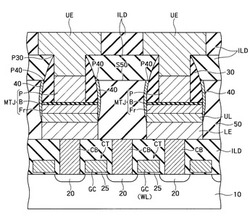

半導体記憶装置およびその製造方法

【課題】MTJ素子が微細化されても、製造工程においてMTJ素子が劣化され難い構成を有する半導体記憶装置を提供する。

【解決手段】本実施形態による半導体記憶装置は、半導体基板を備える。選択トランジスタが半導体基板上に形成されている。下部電極が選択トランジスタの一方の拡散層に電気的に接続されている。磁気トンネル接合素子が下部電極上に設けられている。第1の保護膜が磁気トンネル接合素子の側面に設けられている。上部電極が磁気トンネル接合素子および第1の保護膜上に設けられている。第2の保護膜が上部電極、第1の保護膜および下部電極の側面に設けられている。

(もっと読む)

半導体装置および半導体装置アセンブリ

【課題】外部からの磁場を遮蔽する磁気シールド効果が高い半導体装置を提供する。

【解決手段】半導体基板SUBの主表面上に形成されたスイッチング素子TRを覆うように形成された層間絶縁膜III1と、平板状の引出配線LELと、引出配線LELとスイッチング素子TRとを接続する接続配線ICLと、磁化の向きが可変とされた磁化自由層MFLを含み、引出配線LEL上に形成された磁気抵抗素子TMRとを備える。磁化自由層MFLの磁化状態を変化させることが可能な配線DLと配線BLとを備えている。磁気抵抗素子TMRが複数並んだメモリセル領域において、磁気抵抗素子TMRの上部に配置された第1の高透磁率膜CLAD2が、上記メモリセル領域から、メモリセル領域以外の領域である周辺領域にまで延在している。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】磁気抵抗素子への不純物の侵入や応力の負荷を抑制し、低い駆動電力で高精度に作動する半導体装置およびその製造方法を提供する。

【解決手段】本発明の半導体装置は、主表面を有する半導体基板SUBと、半導体基板SUBの主表面上に位置する磁気抵抗素子MRDとを備えている。その他、保護層IIIと、配線BLと、第1上部電極UEL1と、第2上部電極UEL2とを備えている。保護層IIIは、磁気抵抗素子MRDの側面を覆うように配置されている。配線BLは、上記磁気抵抗素子MRDの上部に位置する。第1上部電極UEL1は、上記磁気抵抗素子MRD上に、平面視における大きさが磁気抵抗素子MRDと実質的に同じであるものが配置されている。第2上部電極UEL2は、上記第1上部電極UEL1上にて、上記第1上部電極UEL1と電気的に接続されており、平面視における大きさが第1上部電極UEL1より大きい。

(もっと読む)

乱数発生装置

【課題】外部環境の影響を受けにくく、充分な乱数精度が得られる乱数発生装置を提供する。

【解決手段】磁化の向きが反転可能な磁化自由層と、非磁性材料からなる中間層と、磁化自由層に対して中間層を介して配置され、磁化の向きが固定された磁化固定層とを含み、スピン注入電流により磁化自由層の磁化の向きが反転される磁気抵抗効果素子20,21を含み、スピン注入電流に関する特性が互いに異なる、複数個の磁気抵抗効果素子20及び21を含んだ乱数発生装置を構成する。

(もっと読む)

磁気結合型アイソレータ

【課題】外部磁場やEMSに対する耐性を十分に確保することができる磁気結合型アイソレータを提供すること。

【解決手段】本発明の磁気結合型アイソレータは、入力信号により外部磁界を発生させるためのコイル2と、コイル2と電気的に絶縁されるとともに磁気的結合が可能な位置であって、平面視においてコイル2と重なるように配置されており、前記外部磁界を検出して電気信号に変換するための磁気抵抗効果素子R1〜R4と、平面視においてコイル2及び磁気抵抗効果素子R1〜R4と重なるように配置された上部シールド膜41と、磁気抵抗効果素子R1〜R4を囲繞するように配置されたミドルシールド膜43と、を具備することを特徴とする。

(もっと読む)

磁気結合型アイソレータ

【課題】外部磁場やEMSに対する耐性を十分に確保することができる磁気結合型アイソレータを提供すること。

【解決手段】本発明の磁気結合型アイソレータは、入力信号により外部磁界を発生させるためのコイル2と、コイル2と電気的に絶縁されるとともに磁気的結合が可能な位置であって、平面視においてコイル2と重なるように配置されており、前記外部磁界を検出して電気信号に変換するための磁気抵抗効果素子R1〜R4と、平面視においてコイル2及び磁気抵抗効果素子R1〜R4と重なるように配置された上部シールド膜41及び下部シールド膜42と、磁気抵抗効果素子R1〜R4を囲繞するように配置されたミドルシールド膜43と、を具備することを特徴とする。

(もっと読む)

磁気抵抗素子及びその製造方法

【課題】磁性層及び非磁性層の特性が劣化するのを抑制する。

【解決手段】磁気抵抗素子は、磁化方向が固定された固定層14と、磁化方向が可変である記録層12と、固定層14及び記録層12に挟まれた非磁性層13とを有する積層構造と、この積層構造の側面を覆い、かつ窒化シリコンからなる第1の保護膜16と、第1の保護膜16の側面を覆い、かつ窒化シリコンからなる第2の保護膜17とを含む。第1の保護膜16は、水素の含有量が4at%以下であり、第2の保護膜17は、水素の含有量が6at%以上である。

(もっと読む)

磁気センサ及びその製造方法

【課題】ヒステリシス特性に優れた磁気センサ及びその製造方法を提供する。

【解決手段】GMR素子とCVD酸化膜11oとの間には、GMR素子における少なくともフリー層FをGMRバー12a−2毎に覆う非磁性膜が形成されていることを特徴とする。

(もっと読む)

磁気センサ及びその製造方法

【課題】ヒステリシス特性に優れた磁気センサ及びその製造方法を提供する。

【解決手段】GMR素子とCVD酸化膜11oとの間には,GMRバー12a−2の表面を覆うように、基板11の全面に亘って非酸化性雰囲気で成膜したPVD絶縁膜11rが形成されていることを特徴とする。

(もっと読む)

磁気抵抗センサ装置

【課題】生産性が良好であって安価に製造し得る共に、磁気抵抗特性に優れ、且つ信頼性のある磁気抵抗センサ装置を提供する。

【解決手段】基板100と、前記基板100上に形成された信号処理回路5と、前記信号処理回路5を平坦化する平坦化膜6と、前記平坦化された信号処理回路上に形成された窒化ケイ素膜7と、前記窒化ケイ素膜7上に形成された磁気抵抗センサ素子9とを備えることを特徴とする磁気抵抗センサ装置とする。また、前記平坦化膜6は、SOG膜であることが好ましい。

(もっと読む)

非磁性中間層を有する磁性薄膜

【課題】高いMR比を実現するとともに、信頼性の向上した磁性薄膜を提供する。

【解決手段】磁性薄膜15は、一対の磁性層7,9と、一対の磁性層7,9の間に挟まれた非磁性中間層8と、を有し、センス電流が一対の磁性層7,9、及び非磁性中間層8の膜面に対して直交方向に流れるようにされている。非磁性中間層8は、SnO2を含む第1の層82と、第1の層82を挟んで設けられ、Snよりも腐食電位の高い材料からなる一対の第2の層81,83と、を有している。

(もっと読む)

化合物半導体積層体

【課題】InAs層等の活性層を直接GaAs等の基板上に形成した構造の化合物半導体積層体であって、信頼性が高く、かつ、バルク単結晶に対して電子移動度の低下が小さい化合物半導体積層体を提供すること。

【解決手段】本発明に係る化合物半導体積層体は、GaAs基板上にInAs層を0.3μm以上と厚く形成し、そのInAs層上にInAs層と基板に平行方向の格子定数が等しく、基板に垂直方向の格子定数差が3%以内の化合物半導体保護層を形成することを特徴とする。すなわち、GaAs、InP、Siのバルク単結晶板、またはそれらの薄膜基板上に、直にInxGa1−xAsySb1−y(0≦x≦0.5、0≦y≦1)を活性層として、0.3μm以上3μm以下の厚さで形成する。この活性層には、導電性の小さな半導体層を保護層として直に形成する。

(もっと読む)

1 - 20 / 28

[ Back to top ]