Fターム[5F092BC04]の内容

ホール/MR素子 (37,442) | MR素子の構造形状 (5,946) | 積層構造 (4,801) | MR素子を形成する層の積層順 (1,654) | 自由層が固定層より上にあるもの (1,135)

Fターム[5F092BC04]に分類される特許

161 - 180 / 1,135

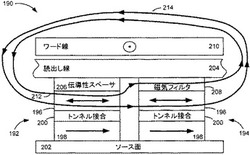

メモリセルおよび方法

【課題】マルチビット磁気ランダムアクセスメモリセルの不揮発性メモリセルのための装置およびプログラム方法を提供する。

【解決手段】第1の磁気トンネル接合(MTJ)192は、磁気フィルタ208を有する第2のMTJ192に隣接する。第2のMTJ192がプログラムされることを防ぐために第1の磁束212を磁気フィルタ208が吸収しつつ、第1の磁束212を用いて第1のMTJ192が第1の論理状態にプログラムされる。

(もっと読む)

磁気抵抗素子、半導体メモリおよび磁気抵抗素子の製造方法

【課題】 エッチング時間を長くすることなく、トンネル絶縁膜の汚染を防止し、磁気抵抗素子の電気的特性の悪化を防止する。

【解決手段】 磁気抵抗素子は、半導体基板上に配置される固定層と、固定層上に配置されるトンネル絶縁膜と、トンネル絶縁膜上に配置され、Feを含む第1自由層と、第1自由層上に配置され、FeおよびTaを含む第2自由層と、第2自由層上に配置され、Ruを含むストッパー層とストッパー層上に配置されるハードマスクとを有している。第1自由層とストッパー層との間隔を第2自由層により大きくできるため、ストッパー層のRuがトンネル絶縁膜に付着することを防止でき、ストッパー層のRuが第1自由層の界面に現れることを防止できる。この結果、エッチング時間を長くすることなく、トンネル絶縁膜の汚染を防止でき、磁気抵抗素子の電気的特性の悪化を防止できる。

(もっと読む)

半導体装置

【課題】磁気抵抗素子を有する半導体装置であって、フリー層に所望の磁化方向と反対方向の磁界の成分が印加されることによる誤動作を抑制することが可能な半導体装置を提供する。

【解決手段】半導体基板の主表面上に位置する、磁化自由層を有する磁気抵抗素子TMRと、磁気抵抗素子TMRの下方に位置し、第1方向に向けて延び、発生する磁界により磁化自由層の磁化状態を変化させることが可能な第1配線DLと、磁気抵抗素子TMRの上方に位置し、第2方向に向けて延び、発生する磁界により磁化自由層の磁化状態を変化させることが可能な第2配線BLとを備えている。磁化自由層は、第2方向に対して対称であり、平面視における第2方向に垂直な方向に対して非対称である。上記第1配線DLは、磁化自由層と平面視において重なる領域において、磁化自由層が磁化されやすい方向に延びる磁化容易軸の延在する方向Heに沿うように延在している。

(もっと読む)

トンネルバリアの形成方法および磁気トンネル接合(MTJ)の形成方法

【課題】高いMR比と低いRA値とを両立させるトンネルバリアの形成方法を提供する。

【解決手段】本発明のトンネルバリアの形成方法は、TMRセンサ40Aに用いられるトンネルバリア29を形成するものであり、ピンド層24に対してNOX処理を施す工程と、ピンド層24の上にM1層を形成する工程と、NOX処理を行い、M1層をMox1層25に変換する工程と、M1層よりも薄いM2層の蒸着とそのNOX処理とを繰り返すことで、Mox1層の上にMox2層26を含むスタックを形成する工程と、そのスタックの上に、Mox1層25およびMox2層26よりも薄い最上部金属層を形成する工程と、アニール処理により、内部の酸素を拡散させて最上部金属層を酸化することでMox3層27を得る工程とを含む。

(もっと読む)

面外磁気トンネル接合セルの強磁性自由層の磁化方向を切換える方法、磁気メモリシステムおよびデータを電子的に記憶する方法

【課題】関連の強磁性層の磁気異方性(すなわち、磁化方向)をウェハ面に垂直にまたは「面外に」位置合わせさせた、しばしば磁気トンネル接合セルと称される磁気スピントルクメモリセル、およびそれらを利用する方法を提供する。

【解決手段】面外磁気トンネル接合セルの強磁性自由層の磁化方向を切換える方法であって、ACスイッチング電流を上記面外磁気トンネル接合セルに通すステップを含む。ACスイッチング電流は、上記強磁性自由層の磁化方向を切換える。

(もっと読む)

磁界検知装置

【課題】 同じ構造のGMR素子を使用し、反応する外部磁界の向きを異ならせることができる磁界検知装置を提供する。

【解決手段】 GMR素子10の長手方向LをX方向とY方向に対して45度の向きで形成する。GMR素子10の固定磁性層の磁化の固定方向を、長手方向Lと直交する向きとし、バイアス用磁石21,22によって自由磁性層の磁化の向きを長手方向Lに揃える。第1の磁束案内層31aと第2の磁束案内層32aをX方向に細長くし、第1の磁束案内層31aと第2の磁束案内層32aをGMR素子10を挟んでY方向に間隔を空けて配置する。X方向の磁界成分が、第1の磁束案内層31aと第2の磁束案内層32aの間で導かれてGMR素子10にY方向の磁束として与えられる。

(もっと読む)

磁気抵抗効果メモリ

【課題】読み出しディスターブを低減する磁気抵抗効果メモリを提供する。

【解決手段】本発明の例に関わる磁気抵抗効果メモリは、磁化方向が不変な第1の磁性層と、磁化方向が可変な第2の磁性層と、第1の磁性層と第2の磁性層の間に設けられた中間層とを有する磁気抵抗効果素子1と、磁気抵抗効果素子1にパルス形状の読み出し電流を流して、前記磁気抵抗効果素子に記憶されたデータを判別する読み出し回路2と、を具備し、読み出し電流のパルス幅は、第2の磁性層内に含まれる磁化が、初期状態から共動してコヒーレントに歳差運動するまでの期間より短い。

(もっと読む)

低飽和磁化自由層を有するスピン転移磁気素子

【課題】より低いスイッチング電流密度で磁気素子に書き込みを行うこと。

【解決手段】磁気素子100は、固定層110と、非磁性であるスペーサ層120と、自由層磁化を有する自由層130とを備える。スペーサ層120は、固定層110と自由層130との間に存在する。自由層130は、被ドープ強磁性材料を含む。被ドープ強磁性材料は、自由層130が室温で1430emu/cm3以下の低飽和磁化を有するように、少なくとも1つの非磁性材料で希釈された少なくとも1つの強磁性材料か、フェリ磁性的にドープされた少なくとも1つの強磁性材料か、又は、少なくとも1つの非磁性材料で希釈され且つフェリ磁性的にドープされた少なくとも1つの強磁性材料を含む。書き込み電流が磁気素子100を通過する時、自由層磁化がスピン転移を用いて切換えられる。

(もっと読む)

マイクロ波生成方法およびスピントルク発振器

【課題】低電流密度下においてマイクロ波を生成可能なスピントルク発振器を提供する。

【解決手段】スピントルク発振器は、第1および第2の外表面を有する非磁性スペーサ層16と、上記第1の外表面と接触する磁界生成層33と、非磁性スペーサ層16の表面に対して垂直な永久磁化を有し上記第2の外表面と完全接触するスピン注入層12とを備える。磁界生成層33は、垂直磁気異方性を示すと共に第1の外表面と完全接触する第1のFGLサブ層331と、面内異方性を示すと共に第1のFGLサブ層331と完全接触する第2のFGLサブ層332とからなる二層構造を有する。従来の磁界生成層に代えて、一方の層が垂直磁気異方性を示し他方の層が面内異方性を示す二重層を設け、垂直異方性を示す層を非磁性スペーサ層16に最も近接させるようにしたので、1×108 A/cm2 という低電流密度下においてマイクロ波が生成可能となる。

(もっと読む)

発振器及び該発振器の動作方法

【課題】発振器及び該発振器の動作方法を提供する。

【解決手段】印加電流、印加電圧及び印加磁場のうち少なくとも一つによって可変的な磁化方向を有する少なくとも1層の磁性層を含み、所定の周波数を有した発振信号を生成する発振部、及び発振部と同じ基板上に集積され、発振信号を差動増幅し、出力信号を提供する出力端子を含む発振器である。

(もっと読む)

スイッチングが改良されたハイブリッド磁気トンネル接合要素を提供するための方法およびシステム

【課題】スイッチングが改良されたハイブリッド磁気トンネル接合要素を提供するための方法およびシステムを提供すること。

【解決手段】磁気デバイスで有用な磁気接合を提供するための方法およびシステムを説明する。磁気接合は、ピンド層、非磁性スペーサ層、および自由層を含む。非磁性スペーサ層は、ピンド層と自由層の間にある。自由層は、円錐状の容易磁気異方性を有する。磁気接合は、磁気接合に書き込み電流が流されるときに自由層が複数の安定な磁気状態間で切替え可能であるように構成される。

(もっと読む)

磁気ランダムアクセスメモリ及びその製造方法

【課題】 熱処理後においても安定して動作可能な磁気ランダムアクセスメモリ及びその製造方法を提供することである。

【解決手段】 実施形態に係る磁気ランダムアクセスメモリは磁化記憶層を持つ。前記磁化記憶層上に、熱処理により前記磁化記憶層から拡散する原子を含む第1の金属層が設けられる。前記第1の金属層上に、第1の界面磁性層が設けられ、前記第1の界面磁性層上に非磁性層が設けられる。前記非磁性層上に第2の界面磁性層が設けられる。前記第2の界面磁性層上に、熱処理により前記磁化参照層から拡散する原子を含む第2の金属層が設けられる。前記第2の金属層上に磁化参照層が設けられる。

(もっと読む)

磁気トンネル接合セル、装置、およびメモリアレイ

【課題】低電流および高面密度を可能とする、垂直異方性および強化層を有する磁気トンネル接合セルを提供する。

【解決手段】磁気トンネル接合セルは、強磁性自由層と、少なくとも約15Åの厚みを有する強化層と、酸化物バリヤ層と、強磁性基準層とを含む。強化層および酸化物バリヤ層は、強磁性基準層と強磁性自由層との間に配置され、酸化物バリヤ層は強磁性基準層に隣接して配置される。強磁性自由層、強磁性基準層、および強化層は、すべて、面外の磁化方向を有する。

(もっと読む)

メモリ装置およびその動作方法

【課題】磁気メモリ素子へのデータを書込む方法を改善する。

【解決手段】スピントルクトランスファランダムアクセスメモリ(STRAM)メモリセルのような磁気メモリ素子に、データを書込むための方法および装置。さまざまな実施形態に従えば、書込電流が磁気メモリセルを通して印加されて、所望の磁化状態への素子の磁気歳差運動を開始する。フィールドアシスト電流の流れは、書込電流の連続した印加の間に磁気メモリ素子に隣接して実質的に印加されて、素子上に磁場を誘起する。フィールドアシスト電流は、書込電流が停止された後も持続され、所望の磁化状態へのフィールドアシストされた歳差を提供する。

(もっと読む)

プログラム可能メモリ素子を備える装置、データ記憶メモリを備える装置、ならびにデータ書込および保持方法

【課題】磁気メモリ素子に対するデータ書込および保持を向上させるための装置および方法を提供する。

【解決手段】不揮発性データ記憶アレイなどにおける磁気メモリ素子に対するデータ書込および保持を向上させるための装置および方法である。さまざまな実施例によれば、プログラム可能メモリ素子は、基準層と記憶層とを有する。基準層には固定磁気配向が提供されている。記憶層は、前記固定磁気配向と反平行な磁気配向を有する第1の領域と、前記固定磁気配向と平行な磁気配向を有する第2の領域とを有するよう、プログラムされている。書込動作中の第1の領域の平行から反平行への磁気配向の遷移を助けるように記憶層の局所的加熱を向上させるために、メモリ素子に熱アシスト層を組み込んでもよい。

(もっと読む)

磁気抵抗効果素子及び磁気メモリ

【課題】記憶層にかかる漏れ磁界を可及的に低減することを可能にする。

【解決手段】膜面に垂直方向の磁気異方性を有する強磁性層10と、強磁性層上に設けられた第1の非磁性層8と、第1の非磁性層上に設けられ、かつ膜面に垂直方向の磁気異方性を有するとともに前記強磁性層の磁化の向きと反平行の磁化を有し、かつ強磁性層の積層方向の膜厚の1/2.8以上1/1.5以下の膜厚を有する参照層6と、参照層上に設けられた第2の非磁性層8と、第2の非磁性層上に設けられ、膜面に垂直方向の磁気異方性を有しスピン偏極した電子の作用により磁化の方向が変化する記憶層2と、を備えている。

(もっと読む)

半導体装置

【課題】メモリ素子の信頼性と消費電流の抑制を両立させることができる半導体装置を提供する。

【解決手段】半導体装置は、複数の磁気メモリセルMCと、複数のディジット線DLと、ディジット線ドライブ回路28Bと、ビット線BL[0:95」とを備える。複数のビット線BL[0:95」は、たとえば12本ごとの複数の群に分割される。半導体装置は、複数のビット線の各々を少なくとも2段階の強度で駆動可能に構成されたビット線ドライブ回路22L,22Rとをさらに備える。ビット線ドライブ回路22L,22Rは、書込群に対しては、書込データに対応する極性の電流で2段階のうち強い強度でビット線を駆動し、非書込群に対しては、2段階のうち弱い強度で自分自身のデータに対応する極性のデータ保持電流を流す。

(もっと読む)

耐久性が改良された熱アシスト磁気ランダムアクセスメモリ素子

【課題】 耐久性が改良された熱アシスト磁気ランダムアクセスメモリ素子を提供する。

【解決手段】 本発明は、熱アシストスイッチング書き込み操作に適した磁気メモリ素子であって、磁気トンネル接合の一端と電気的に連絡した電流線を備え、磁気トンネル接合が、固定磁化を有する第1の強磁性層と、所定の高温しきい値で自由に整列させることができる磁化を有する第2の強磁性層と、第1の強磁性層と第2の強磁性層の間に提供されたトンネル障壁とを備え、電流線が、書き込み操作中に磁気トンネル接合を通して加熱電流を流すように適合され、前記磁気トンネル接合が、加熱電流が磁気トンネル接合を通して流されるときに熱を発生するように適合された少なくとも1つの加熱要素と、前記少なくとも1つの加熱要素と直列の熱障壁とをさらに備え、前記熱障壁が、磁気トンネル接合内部で前記少なくとも1つの加熱要素によって発生する熱を閉じ込めるように適合される磁気メモリ素子に関する。

(もっと読む)

磁気ランダムアクセスメモリ

【課題】一端がビット線に接続された磁気抵抗素子1と、一端が磁気抵抗素子1の他端に接続され、ゲートがワード線に接続され、他端がソース線に接続された選択トランジスタ2、3とで構成されたメモリセル5よりなるスピン注入方式の磁気ランダムアクセスメモリにおいて、設計工数や製造コストが増大せず、特に小容量サイズのメモリではチップ面積の増加を最小限に抑え、MTJ素子に抵抗状態を変化させるのに充分な電流をながせる磁気ランダムアクセスメモリを提供する。

【解決手段】選択トランジスタがNチャンネルMOSトランジスタ2とPチャンネルMOSトランジスタ3とを並列接続され、ゲートにそれぞれワード線と反転ワード線とが接続された構成であることを特徴とする。

(もっと読む)

抵抗変化型メモリ

【課題】 メモリの動作特性の向上を図る。

【解決手段】実施形態の抵抗変化型メモリは、ビット線BLとワード線WLと、第1エミッタ21と、第1ベース23と、第1コレクタ22とを有する、第1駆動型の第1バイポーラトランジスタ2と、第2エミッタ31と、第2ベース33と、第2コレクタ32とを有する第2駆動型の第2バイポーラトランジスタ3と、第1及び第2端子を有する抵抗変化型メモリ素子1と、を具備し、メモリ素子1の第1端子は第1及び第2エミッタ21,31に接続され、メモリ素子1の第2端子は、ビット線BLに接続され、第1及び第2ベース23,33はワード線WLに接続される。

(もっと読む)

161 - 180 / 1,135

[ Back to top ]