Fターム[5F092BC04]の内容

ホール/MR素子 (37,442) | MR素子の構造形状 (5,946) | 積層構造 (4,801) | MR素子を形成する層の積層順 (1,654) | 自由層が固定層より上にあるもの (1,135)

Fターム[5F092BC04]に分類される特許

101 - 120 / 1,135

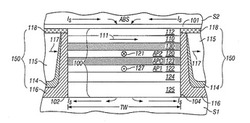

改善された硬質磁性体バイアス構造を備える面垂直電流(CPP)磁気抵抗(MR)センサ

【課題】改善された硬質磁性体バイアス構造を備える面垂直電流(CPP)磁気抵抗(MR)センサを提供する。

【解決手段】磁気記録ディスクドライブ用CPP−GMR又はCPP−TMR読み出しヘッドのための硬質磁性体バイアス構造が、2つのセンサシールドS1、S2間に位置し、センサの自由層110の側縁に隣接している。絶縁層116は、バイアス構造と下部シールドとの間、及び自由層110の側縁の間に位置する。バイアス構造150は、Ir又はRuのシード層114と、そのシード層114上の強磁性で化学的配列が規則付けられたFePt合金ハードバイアス層115と、そのFePt合金ハードバイアス層115上のRu又はRu/Irキャッピング層118とを含む。FePt合金は、そのc軸が全般的に層の平面内にある面心正方構造を有する。

(もっと読む)

磁気ランダムアクセスメモリ及びその動作方法

【課題】スピン注入方式の書き込みを実行するとき磁化方向に依らず書き込み特性が同様となる磁気ランダムアクセスメモリ及びその動作方法を提供する。

【解決手段】スピン注入方式の磁気ランダムアクセスメモリは、複数の磁気メモリセル10と電流供給部43+47+49と制御部41+70+80とを具備する。電流供給部は、磁気メモリセル又はその近傍へ書き込み電流を供給する。磁気メモリセルは、磁化状態によりデータを記憶する磁性体記憶層と、書き込み電流に基づいて書き込むデータに依らず同一の制御原理で磁性体記憶層にスピン電子を供給するスピン制御層とを備える。制御部は、書き込むデータに基づいて、スピン制御層の磁化方向を時間的に連続的に回転させながら、電流供給部の書き込み電流の供給を制御する。

(もっと読む)

磁気記憶素子および磁気記憶装置

【課題】半選択状態になった磁気記憶素子のデータの誤反転を抑制することにより信頼性の高い書き込み動作を行うことができる磁気記憶素子、およびこれを用いた磁気記憶装置を提供する。

【解決手段】磁化容易軸91と磁化困難軸92とを有する記録層3は、平面視においてすべての領域が第1導電層WTまたは第2導電層BLの少なくとも一方と重なる。磁化容易軸91に沿い、記録層3と平面視において重なる寸法が最大となる第1の線分の第1の端点TP,BPは、第2導電層BLと平面視において重ならない。上記第1の線分の中点を通り、平面視において第1の線分に直交し、記録層3と平面視において重なる第2の線分の1対の端点である第2の端点LP,RPのうち少なくとも一方は、第1導電層WTと平面視において重ならない。

(もっと読む)

磁気発振素子及びスピン波装置

【課題】高周波数の発振が得られる磁気発振素子及びスピン波装置を提供する。

【解決手段】実施形態によれば、第1電極と第2電極と第1磁性層と第2磁性層と第1スペーサ層とを備えた磁気発振素子が提供される。第1磁性層は第1電極と第2電極との間に設けられ磁化方向が可変である。第2磁性層は第1電極と第1磁性層との間に設けられ磁化方向が固定されている。第1スペーサ層は、第1磁性層と第2磁性層との間に設けられ非磁性である。第1電極と第2電極とを結ぶ第1方向における第1磁性層の厚さは、第1磁性層のスピン侵入長の2倍よりも厚い。第1磁性層の厚さは、第2電極の第1磁性層の側の第1面の最大幅よりも薄い。第1磁性層は、第1方向に沿ってみたときに第1面の外側に設けられた第1縁部を有する。第1面の縁の接線に対して垂直な方向における第1縁部の幅は、第1磁性層の交換長以上である。

(もっと読む)

抵抗変化メモリ

【課題】セルサイズの微細化が可能な抵抗変化メモリを提供する。

【解決手段】抵抗変化メモリ10は、第1の方向に延在する複数のワード線と、第2の方向に延在する第1乃至第3のビット線と、第1及び第3のビット線に接続された複数の可変抵抗素子20と、半導体基板30内に設けられ、かつ斜め方向に延在する複数のアクティブ領域AAと、複数のアクティブ領域AAに設けられた、かつ可変抵抗素子20に接続された複数の選択トランジスタ21と、選択トランジスタと第3のビット線とを接続する複数のコンタクトプラグ37とを含む。複数の可変抵抗素子20は、第2の方向に並ぶようにして、第1のビット線の下方かつ複数のワード線間のそれぞれに配置された第1の可変抵抗素子群と、第2の方向に並ぶようにして、第3のビット線の下方かつ複数のワード線間のそれぞれに配置された第2の可変抵抗素子群とからなる。

(もっと読む)

磁気記憶素子、磁気記憶装置、および磁気メモリ

【課題】磁壁が静止した状態から移動状態に遷移させるために必要な電流密度を低減化することができるとともに、磁壁の移動を安定に行うことができる磁気記憶素子、磁気記憶装置、および磁気メモリを提供する。

【解決手段】本実施形態の磁気記憶素子は、第1方向に延在し、磁壁により隔てられた複数の磁区を有する磁性細線と、前記磁性細線に前記第1方向の電流および前記第1方向と逆方向の電流を流すことが可能な電極と、電気的な入力を受け、前記磁性細線の全体または一部の領域の磁壁の移動をアシストするアシスト部と、を備えている。

(もっと読む)

磁気記憶装置

【課題】集積度が高い磁気記憶装置を提供する。

【解決手段】実施形態に係る磁気記憶装置は、基板と、前記基板上に設けられた複数個の磁気抵抗効果素子と、を備える。そして、前記複数個の磁気抵抗効果素子のうち、上方から見て互いに最も近い位置にある2個の磁気抵抗効果素子は、前記基板からの距離が相互に異なる。

(もっと読む)

磁気ランダムアクセスメモリ及びその製造方法

【課題】 界面磁性層が十分に結晶化された磁気ランダムアクセスメモリ及びその製造方法を提供する。

【解決手段】 実施形態に係る磁気ランダムアクセスメモリは、第1の磁性層、第1の界面磁性層、非磁性層、第2の界面磁性層、及び第2の磁性層が順に積層された磁気抵抗効果素子を有する。前記第1の磁性層の下層、前記第1の磁性層と前記第1の界面磁性層との間、前記第2の界面磁性層と前記第2の磁性層との間、及び前記第2の磁性層上のいずれかに第1の金属原子、第2の金属原子、及びB原子を含む金属層が設けられる。

(もっと読む)

抵抗変化型メモリ

【課題】メモリの動作マージンを向上する。

【解決手段】本実施形態の抵抗変化型メモリは、ビット線BLA,BLC間に接続された第1のセルSCAとビット線BLB,BLC間に接続された第2のセルSCBとを含むメモリセルMCと、第1のセルSCAを形成するメモリ素子8A及び選択トランジスタTrAと、第2のセルSCBを形成するメモリ素子8B及び選択トランジスタTrBとを具備し、メモリセルに対する書き込み動作時、ワード線が活性化されている期間において、メモリセルMC内の2つのメモリ素子8A,8Bを第1の抵抗状態に変化させた後、2つのメモリ素子8A,8Bのうち一方のメモリ素子を第2の抵抗状態に変化させる。

(もっと読む)

反強磁性物質層と弱い交換結合を有する磁気装置

【課題】スピントルク発振器において使われることができる磁気装置を提供する。

【解決手段】自由層10に弱い交換で結合した少なくとも一つの反強磁性層8から成る磁気装置6を含むスピントルク発振器(STO)4から成るシステム2において、磁気装置6は、磁気異方性を有する自由層10から成る。磁気異方性は、少なくとも部分的に不均一である。磁気装置は、自由層10に隣接して反強磁性層8が設けられ、弱い交換結合が自由層10の磁気異方性の不均一を減らす弱い交換結合するように構成される。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】 メモリセルの微細化を図りつつ、セル電流を確保する。

【解決手段】 実施形態による半導体記憶装置は、ゲート溝15と第1乃至第3の溝19a、19b、18とを有し、第1乃至第3の溝はゲート溝の底面に形成され、第3の溝は第1及び第2の溝の間に形成された半導体基板11と、第1の溝内形成された第1のゲート部21aと第2の溝内形成された第2のゲート部21bと第3の溝内形成された第3のゲート部21cとゲート溝内に形成された第4のゲート部21dとを有するゲート電極21と、を具備する。ゲート電極を有するセルトランジスタTrは、第1及び第3のゲート部間の半導体基板内に形成された第1のチャネル領域Ch1と、第2及び第3のゲート部間の半導体基板内に形成された第2のチャネル領域Ch2と、を有する。

(もっと読む)

マイクロコンピュータ周辺装置、初期設定方法、半導体集積装置

【課題】半導体集積回路装置におけるマイクロコンピュータ周辺装置の高速起動。

【解決手段】マイクロコンピュータ周辺装置は、マイクロコンピュータから受信した初期設定コマンドに基づく設定信号をレジスタを介して機能回路部に出力し、初期設定を行う。ここで、レジスタにおける設定信号のデータをMTJ素子等の不揮発性記憶素子を用いた保持回路で記憶しておく。電源再投入時には、保持回路に記憶された設定信号のデータで初期設定を行う。

(もっと読む)

半導体装置及びその製造方法

【課題】積層ハードマスクを部分的に残存させつつ、配線層用のビアプラグのアスペクト比を低減することが可能な半導体装置及びその製造方法を提供する。

【解決手段】基板上に第1の配線層102を形成し、第1の配線層102上に、半導体素子材料103、第1の絶縁膜104、及び第2の絶縁膜105を順に形成し、半導体素子材料103、第1の絶縁膜104、及び第2の絶縁膜105を含むピラー状の構造体を形成する。第1の配線層102上に、構造体の上面及び側面を覆うように、第3及び第4の絶縁膜109,106を形成し、第4の絶縁膜106を、第2の絶縁膜105が露出するように、部分的に除去する。第1及び第2の絶縁膜内に、半導体素子材料に接続された第1のビアプラグ107を形成し、第3及び第4の絶縁膜内に、第1の配線層102に接続された第2のビアプラグ108を形成し、第1及び第2のビアプラグ上に第2の配線層111を形成する。

(もっと読む)

多層膜の製造方法

【課題】多層膜内の特定層だけに格子振動を与えてその多層膜の特性を向上させる。

【解決手段】実施形態に係わる多層膜の製造方法は、第1の層(CoFeB)を形成する工程と、第1の層(CoFeB)上に第2の層(MgO)を形成する工程と、第2の層(MgO)の表面に対してGCIB照射を行うことにより、第2の層(MgO)の結晶情報を第1の層(CoFeB)に転写する工程とを備える。

(もっと読む)

磁気記録素子及び不揮発性記憶装置

【課題】書き込み時における磁化反転がより高速に起こる磁気記録素子及び不揮発性記憶装置を提供する。

【解決手段】実施形態によれば、積層体を備えた磁気記録素子が提供される。積層体は第1積層部と第2積層部とを含む。第1積層部は、膜面に対して垂直成分を有する第1の方向に磁化が固定された第1の強磁性層と、磁化の方向が膜面垂直な方向に可変である第2の強磁性層と、第1の強磁性層と第2の強磁性層との間の第1の非磁性層と、を含む。第2積層部は、積層軸に沿って第1積層部と積層される。第2積層部は、磁化の方向が膜面平行な方向に可変である第3の強磁性層と、膜面に対して垂直成分を有する第2の方向に磁化が固定された第4の強磁性層と、第3の強磁性層と第4の強磁性層との間の2の非磁性層と、を含む。積層軸を法線とする平面において、第4の強磁性層の外縁は第1積層部の外縁よりも外側の部分を有する。

(もっと読む)

磁気抵抗効果素子、磁気ヘッド、磁気ヘッドスライダ、ヘッドジンバルアセンブリ及びハードディスクドライブ装置

【課題】スペーサ層に隣接する磁性層の酸化を防止し、かつ大きなMR変化率を実現する。

【解決手段】磁気抵抗効果素子は、外部磁界に応答して磁化方向のなす相対角度が変化する第1及び第2の磁性層L1,L2と、第1の磁性層L1と第2の磁性層L2との間に位置するスペーサ層16と、を有している。第1の磁性層L1は、磁気抵抗効果素子が形成される基板に対し、第2の磁性層L2よりも近い側に位置している。スペーサ層16は、酸化ガリウムを主成分とする主スペーサ層16bと、主スペーサ層16bと第1の磁性層L1との間に位置し、一部が酸化された銅を主成分とするボトム層16aと、を有している。

(もっと読む)

磁気デバイス及び製造方法

【課題】 下部電極表面の非結晶性及び平坦性を確保しつつ、製造工程の効率化を図ることのできる磁気デバイスを提供すること。

【解決手段】 本磁気デバイスは、電極10と、電極10上に形成された磁気抵抗素子20とを備える磁気デバイスであって、電極10は、タンタルを含む第1金属層12と、第1金属層12上に設けられ、磁気抵抗素子20を構成する材料のうち少なくとも1つの同じ成分を含み、かつ当該同じ成分はCuより拡散しにくく、当該同じ成分を含む非結晶の合金を材料とするバッファ層16と、バッファ層16上に設けられ、タンタルを含む第2金属層18と、を有することを特徴とする。

(もっと読む)

磁気ランダムアクセスメモリ及びその動作方法

【課題】読み出し時の誤書き込みのリスクをより抑制し、かつ、より正確な読み出しを可能とする。

【解決手段】磁気ランダムアクセスメモリは、スピン注入により変更される自由強磁性層の磁化の向きでデータを書き込み可能な第1磁気抵抗素子を含むメモリセルと、スピン注入により変更される自由強磁性層の磁化の向きでリファレンス用データを記憶する複数の第2磁気抵抗素子を含み、メモリセルの読み出し動作時に用いられるリファレンスセルとを具備する。複数の第2磁気抵抗素子は、互いに直列に接続され、自由強磁性層の磁化の向きが互いに逆の向きで、固定強磁性層の磁界の向きが互いに同じ向きで、固定強磁性層同士又は自由強磁性層同士が電気的に接続されている。

(もっと読む)

電流センサ

【課題】簡便な構成で電気配線に流れる電流を広い電流レンジで検知する電流センサを提供する。

【解決手段】測定対象Aに接続される電気配線wa,wb1,wc1と、抵抗値が一定比率で増加する直線部分と抵抗値が飽和する飽和部分とからなる磁気抵抗特性を有し、それぞれが前記電気配線から異なる距離d1,d2,d3で離間して配置される磁気抵抗素子11a,11b,11cと、磁気抵抗素子11a,11b,11cそれぞれにセンス電流を流すセンス電流部12と、磁気抵抗素子11a,11b,11cにおけるセンス電流値の変化から磁気抵抗特性の前記直線部分から飽和部分へ移行する抵抗値の飽和点に到達したことを検知し、前記電流配線に流れる電流がある規定値に到達したとして出力する検知手段13と、を備え、検知手段13は、前記電流配線に流れる電流について磁気抵抗素子11a,11b,11cごとに異なる規定値への到達を検知する。

(もっと読む)

磁気センサ及びその製造方法

【課題】 特に、同一チップ上に感度軸方向が異なり、ブリッジ回路を構成する複数の磁気抵抗効果素子を形成でき、測定精度に優れた磁気センサを提供することを目的とする。

【解決手段】 同一チップ29上に磁気抵抗効果素子13a〜13dが複数個、備えられてブリッジ回路を構成している。各磁気抵抗効果素子の固定磁性層21はセルフピン止め型であり、直列回路を構成する磁気抵抗効果素子13a,13d(13b,13c)同士は、感度軸方向P1〜P4が反平行となっている。各磁気抵抗効果素子のフリー磁性層23の上面には、フリー磁性層23との間で磁場中でのアニール処理を行うことなく交換結合バイアスを生じさせ各フリー磁性層23の磁化方向を磁化変動可能な状態で感度軸方向に対して直交方向に揃えることができる反強磁性層24が設けられている。

(もっと読む)

101 - 120 / 1,135

[ Back to top ]