Fターム[5F092BC04]の内容

ホール/MR素子 (37,442) | MR素子の構造形状 (5,946) | 積層構造 (4,801) | MR素子を形成する層の積層順 (1,654) | 自由層が固定層より上にあるもの (1,135)

Fターム[5F092BC04]に分類される特許

21 - 40 / 1,135

半導体記憶装置

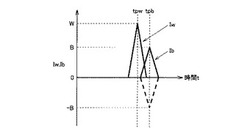

【課題】誤書込を抑制することが可能なMRAM装置を提供する。

【解決手段】三角波状のパルス電流Iwをワード線に流してパルス磁場をトンネル磁気抵抗素子の自由層に印加する。また、パルス電流Iwがピークに達した後にピークに達する三角波状のパルス電流Ibをビット線に流してパルス磁場を自由層に印加する。これにより、自由層の磁化ベクトルの歳差運動をその熱揺動よりも大きくして、パルス電流Iwのみで自由層の磁化方向が反転するのを防止できる。また、パルス電流Ibによって自由層の磁化方向を確実に反転させることができる。

(もっと読む)

固定層構造および自由層構造にCoFeBTaを有する磁気センサ

【課題】向上した磁気性能および堅牢性を有する磁気読み出しセンサを提供する。

【解決手段】磁気センサは、磁化自由層構造310と磁化固定層構造とを含む。磁化固定層構造は、非磁性結合層318によって互いに分離させた第1の磁性層314および第2の磁性層316を含む。磁化固定層構造の第2の磁性層はCoFeBTaの層を含んでおり、この層が原子の拡散を防止し、さらには所望のBCC結晶粒成長を促進する。磁化自由層構造は、原子拡散をさらに防止し、所望のBCC粒成長をさらに促進するためのかかるCoFeBTa層を含むこともできる。

(もっと読む)

半導体集積回路およびその動作方法

【課題】半導体集積回路の内蔵メモリとしてのMRAMへの不正アクセスに対する保護を改善すること。

【解決手段】半導体集積回路(10)は、プロセッサ(1)と不揮発性メモリ(3)とを具備する。不揮発性メモリ(3)は、複数の磁気ランダムアクセスメモリセルと、複数の磁気リードオンリーメモリセルとを含む。複数の磁気ランダムアクセスメモリセルはプロセッサ(1)による通常書き込みによって書き換えが可能とされ、複数の磁気リードオンリーメモリセルはプロセッサ(1)による通常書き込みによって書き換えが不可能とされる。不揮発性メモリ(3)と接続された感知回路(2)は、不揮発性メモリ(3)の不正アクセスによる複数の磁気リードオンリーメモリセルの状態遷移を感知する。状態遷移に応答して、感知回路(2)は不正アクセスの検出結果をプロセッサ(1)に通知する。

(もっと読む)

半導体装置

【課題】直流電源配線に電流が流れたか否かを検出可能な回路を備えた半導体装置を提供する。

【解決手段】半導体装置において、駆動回路BLDU,BLDD,BLBDU,BLBDDは、電流磁界またはスピン注入によってトンネル磁気抵抗素子TMR,TMRBを第1の磁化状態に初期設定するために、制御信号線BL,BLBに直流電流を流す。電源配線DLは、トンネル磁気抵抗素子TMR,TMRBに近接して設けられる。ここで、トンネル磁気抵抗素子TMR,TMRBは、電源配線DLに直流電流が流れるときに生じる電流磁界によって第2の磁化状態に変化する。センスアンプ10は、トンネル磁気抵抗素子TMR,TMRBが第1の磁化状態から第2の磁化状態に変化したか否かを判定するために、制御信号線BL,BLBを介してトンネル磁気抵抗素子TMR,TMRBに流れる電流を検出する。

(もっと読む)

磁気センサ

【課題】ピン層の磁化方向とフリー層の磁化方向との成す角度に対して検出精度が異なることを簡素な構成で抑制することができると共に、応答速度を向上させることができる磁気センサを提供する。

【解決手段】磁化方向が所定方向に固定されたピン層11および外部磁界に応じて磁化方向が変化するフリー層13を有し、ピン層11の磁化方向とフリー層13の磁化方向との成す角度に応じて抵抗値が変化する第1、第2磁気抵抗素子R1、R2を有する検出部10を備える。そして、第1、第2磁気抵抗素子R1、R2をピン層11の磁化方向が互いに直交する状態で直列接続し、検出部10から第1、第2磁気抵抗素子R1、R2の中点電圧を検出信号として出力する。

(もっと読む)

スピントランジスタおよびメモリ

【課題】IDP/IDAP比を高めることのできるスピントランジスタおよびメモリを提供する。

【解決手段】本実施形態によるスピントランジスタは、基板上に形成されたソース/ドレインの一方となる第1磁性層と、前記第1磁性層上に設けられチャネルとなる絶縁膜と、前記絶縁膜上に設けられ前記ソース/ドレインの他方となる第2磁性層と、前記絶縁膜の側面に設けられたゲート電極と、前記ゲート電極と前記絶縁膜の前記側面との間に設けられたゲート絶縁膜と、備えている。

(もっと読む)

歪検知装置及びその製造方法

【課題】微小領域で歪を高感度に検知することができる歪検知装置及びその製造方法を提供する。

【解決手段】実施形態によれば、半導体回路部と、半導体回路部の上に設けられた検知部と、を含む歪検知装置が提供される。半導体回路部は、半導体基板上に設けられたトランジスタを有する。検知部は、トランジスタの上方に設けられた空洞部と、空洞部と並置された非空洞部と、を有する。検知部は、可動梁、歪検知素子部、第1、第2埋め込み配線を含む。可動梁は、固定部分及び可動部分を有し、第1、第2配線層を含む。固定部分は非空洞部に固定される。可動部分は、固定部分から空洞部に延びトランジスタと離間する。歪検知素子部は、可動部分に固定され、第1、第2配線層と電気的に接続され、第1磁性層を含む。第1、第2埋め込み配線は、非空洞部に設けられ、第1、第2配線層と半導体回路部とを電気的に接続する。

(もっと読む)

磁気センサ装置

【課題】 TMR素子の設置環境が高温環境下であってもTMR素子の絶縁破壊を防ぎ、さらにはノイズの影響を受け難く、高いS/N比を得ることができる磁気センサ装置を提供すること。

【解決手段】 トンネル磁気抵抗素子2と、該トンネル磁気抵抗素子2の両端子に一端が接続された一対のリード線3と、一対のリード線3の他端に接続されトンネル磁気抵抗素子2を電圧駆動または電流駆動して抵抗変化を検出する駆動検出回路4とを備え、該駆動検出回路4が、一対のリード線3の他端に接続された一対の出力端子4a間に少なくとも一対のダイオード6aを互いに逆向きにして並列または直列に接続して構成された保護回路6を有している。

(もっと読む)

半導体装置およびその製造方法

【課題】素子特性を劣化させることなく、半導体材料または絶縁膜の結晶特性を改善することができる低温アニールを用いた半導体装置の製造方法、並びに、このような低温アニールに適した半導体装置を提供する。

【解決手段】本実施形態による半導体装置は、半導体基板の上方に設けられた金属からなる下部電極と、下部電極の上方に設けられた金属からなる上部電極と、下部電極と上部電極との間に設けられた結晶層とを備える。下部電極および上部電極の各膜厚は、結晶層の結晶化に用いられるマイクロ波の周波数に対応する表皮効果における表皮層よりも薄い。

(もっと読む)

磁気抵抗効果素子およびその製造方法

【課題】磁気特性の低下の抑制を図る。

【解決手段】磁気抵抗効果素子は、磁化方向が膜面に対して垂直でかつ不変である第1磁性層33と、前記第1磁性層上に形成されたトンネルバリア層34と、前記トンネルバリア層上に形成され、磁化方向が膜面に対して垂直でかつ可変である第2磁性層35と、を具備する。前記第1磁性層は、上部側に形成され、前記トンネルバリア層の下部に接する界面層32と、下部側に形成され、垂直磁気異方性の起源となる本体層31と、を有する。前記界面層は、内側に設けられた磁化を有する第1領域38と、その外側に前記第1領域を取り囲むように設けられた前記第1領域よりも磁化の小さい第2領域39と、を含む。

(もっと読む)

アナログ/デジタル変換器

【課題】変換精度が高いアナログ/デジタル変換器を提供する。

【解決手段】実施形態のアナログ/デジタル変換器は、電圧生成部と複数の比較器とを備える。電圧生成部は、基準電圧を、複数の可変抵抗器で分圧して複数の比較用電圧を生成する。複数の可変抵抗器の各々は、直列に接続されるとともに、外部信号に応じて各々の抵抗値が可変に設定される複数の可変抵抗素子を含む。各比較器は、複数の比較用電圧のうちの何れかの比較用電圧とアナログの入力電圧とを比較し、その比較結果に応じたデジタル信号を出力する。

(もっと読む)

磁気抵抗効果素子、磁気メモリ及び磁気抵抗効果素子の製造方法

【課題】磁気抵抗効果素子の特性劣化を抑制する。

【解決手段】本実施形態の磁気抵抗効果素子は、膜面に対して垂直方向に磁気異方性と不変な磁化方向とを有する第1の磁性体30と、膜面に対して垂直方向に磁気異方性と可変な磁化方向とを有する第2の磁性体10と、磁性層10,30の間の非磁性体20とを、含む。第1及び第2の磁性体のうち少なくとも一方は、ボロン(B)及び希土類金属及び遷移金属を含む磁性層301を備え、磁性層301において、希土類金属の含有量は、20at.%以上であり、遷移金属の含有量は、30at.%以上であり、ボロンの含有量が、1at.%以上、50at.%以下である。

(もっと読む)

角度検出センサおよびその製造方法

【課題】1つの基板に設けた複数の磁気抵抗素子部のピン磁性層を異なる方向に着磁させる。

【解決手段】基板10を用意し、基板10の一面13の上方に複数の磁気抵抗素子部22を形成する。次に、基板10において一面13から他面14までを貫通する貫通孔15を形成する。続いて、基板10の一面13側と他面14側とのいずれか一方から他方に貫通孔15を介して電流が流れる直線状の電流供給ライン40を形成する。ここで、電流供給ライン40としてワイヤ41を用いる。この後、ワイヤ41に電流を流すことによってワイヤ41の周囲にワイヤ41を中心とした同心円状の磁界を発生させると共に、基板10全体を加熱して磁場中アニールを行う。これにより、複数の磁気抵抗素子部22を構成するピン磁性層22aの磁化の向きがそれぞれ同心円状の磁界の接線方向に向くように着磁を行う。

(もっと読む)

混合器

【課題】

乗算信号の出力低下を回避しつつ、低いローカルパワーで作動可能とする。

【解決手段】

磁化固定層、磁化自由層、および前記磁化固定層と前記磁化自由層との間に配設された非磁性スペーサー層を備え、高周波信号S1およびローカル信号S2を入力したときに磁気抵抗効果によって両信号S1,S2を乗算して電圧信号(乗算信号)S3を生成する磁気抵抗効果素子2の磁化自由層に対し、磁場印加部3より発生する磁場を膜面法線方向、または膜面方向から膜面法線方向に傾けて掛けることで、Q値の高い共振特性を得ることができ、大きな乗算信号を得ることができ、さらに狭帯域周波数選択性の機能を有する周波数変換装置を提供する。

(もっと読む)

磁気センサ装置およびその製造方法

【課題】1つの基板に形成した複数の磁気抵抗素子部のピン磁性層を任意の方向に着磁させたとしても、着磁による熱拡散の影響を低減する。

【解決手段】基板10の一面11の上方に各磁気抵抗素子部50を形成する。次に、基板10のうち各磁気抵抗素子部50に対応する部分に溝13を形成して空間部14を形成する。この後、磁場の向きが第1の方向に設定された磁場中に、各磁気抵抗素子部50が形成された基板10を配置し、一方の磁気抵抗素子部50を局所的に加熱して磁場中アニールを行い、当該磁気抵抗素子部50のピン磁性層51の磁化の向きを第1の方向に着磁する。また、磁場の向きを第1の方向とは異なる第2の方向に設定した磁場中において、他方の磁気抵抗素子部50を局所的に加熱して磁場中アニールを行い、当該磁気抵抗素子部50のピン磁性層51の磁化の向きを第2の方向に着磁する。

(もっと読む)

周波数選択性を有する混合器

【課題】

大きな乗算信号を取り出すことが可能で、さらに受信用バンドパスフィルタ機能を有した混合器を提供することを主目的とする。

【解決手段】

磁化固定層、磁化自由層、および前記磁化固定層と前記磁化自由層との間に配設された非磁性スペーサー層を備え、高周波信号S1およびローカル信号S2を入力したときに磁気抵抗効果によって当該両信号S1,S2を乗算して電圧信号(乗算信号)S4を生成する磁気抵抗効果素子2から得た乗算信号は、共振特性の強度に応じて増減し、共振周波数f0と両信号S1,S2のそれぞれ周波数f1、f2が一致するときに最大強度を示し、共振周波数f0から周波数f1、f2の両方またはいずれか一つが離れると減衰する。あたかもバンドパスフィルタを挿入したときと同じ効果があり、磁場印加部3による磁場を制御することで、所望のバンドパスフィルタを有する周波数変換装置を提供できる。

(もっと読む)

半導体磁気記憶装置

【課題】磁気記憶素子を構成する層を、周辺回路部内で有効に活用する。

【解決手段】実施形態によれば、半導体磁気記憶装置は、セルトランジスタを含むセル部と、周辺トランジスタを含む周辺回路部とが形成された半導体基板を備える。さらに、前記装置は、前記セル部内に配置され、下部電極と、前記下部電極上に形成された電極間層と、前記電極間層上に形成された上部電極とを含む磁気記憶素子を備える。さらに、前記装置は、前記周辺回路部内に配置され、前記下部電極を形成している第1の層と、前記電極間層を形成している第2の層と、前記上部電極を形成している第3の層とを含む構造体を備える。さらに、前記装置は、前記第1の層に電気的に接続された第1及び第2のプラグを備える。さらに、前記第1の層は、前記第1のプラグと前記第2のプラグを電気的に接続する配線として機能する。

(もっと読む)

周波数変換装置

【課題】

本発明は磁気抵抗効果素子を用いて乗算信号を生成する混合器に関し、受信帯域幅を調整するため、複数の混合器を有した周波数変換装置を提供する。

【解決手段】

磁化固定層、磁化自由層、および前記磁化固定層と前記磁化自由層との間に配設された非磁性スペーサー層を備え、第1高周波信号およびローカル用の第2高周波信号を入力したときに磁気抵抗効果によって当該両高周波信号を乗算して乗算信号を生成する磁気抵抗効果素子と、前記磁化自由層に磁場を印加する磁場印加部とを有する混合器を複数備え、これら複数の混合器に対して、前記第1高周波信号と、前記複数の混合器毎にそれぞれ異なるローカル用の前記第2高周波信号とを入力したときに生成する複数の乗算信号を加算して出力することで、周波数変換装置とする。

(もっと読む)

半導体記憶装置

【課題】4個のトランジスタと2個のMTJ素子からなり、電源を印加しないでも不揮発性メモリとして動作するSRAMからなる半導体記憶装置を提供する。

【解決手段】第1及び第2のインバータ2,4と第1及び第2の転送用MOSFET3,5とを含むメモリセル1からなるSRAMにおいて、第1及び第2のインバータ2,4はスピン注入型のMTJ素子6,8と駆動用MOSFET7,9とからなり、これらのインバータ2,4からフリップフロップ回路が構成され、第1及び第2のインバータ2,4の出力端子は、それぞれ第1及び第2の転送用MOSFET3,5を介してビットライン及びビットラインバーに接続され、第1及び第2の転送用MOSFET3,5のゲートは、同一のワードラインに接続される。従来のSRAMに比較してメモリセルの面積が小さく、高速で低消費電力の不揮発性メモリが得られる。

(もっと読む)

改良されたトンネル障壁を有する磁気トンネル接合

【課題】磁気ランダムアクセスメモリ(MRAM)セル用に適し且つ第1強磁性層とトンネル障壁層と第2強磁性層とから成る磁気トンネル接合を製作する方法を提供する。

【解決手段】第1強磁性層を形成すること、トンネル障壁層22を形成すること及び第2強磁性層を形成することから成る。当該トンネル障壁層22を形成することは、金属製のMg層を蒸着すること及び当該金属のMgをMgO層22aに変えるために当該蒸着された金属製のMg層を酸化することから成る。当該トンネル障壁層が、少なくとも2つのMgO層22aから成るように、当該トンネル障壁層を形成するステップが、少なくとも2回実施される。

(もっと読む)

21 - 40 / 1,135

[ Back to top ]