Fターム[5F101BA54]の内容

不揮発性半導体メモリ (42,765) | 電荷蓄積機構 (9,664) | トラップ蓄積型 (3,039) | クラスタ (341)

Fターム[5F101BA54]に分類される特許

141 - 160 / 341

非揮発性メモリのための高効率ホットキャリア注入プログラミングの方法及び構造

【課題】 プログラミング効率を向上させた非揮発性メモリのためのプログラミングの方法及び構造を提供する。

【解決手段】 非揮発性メモリセル内の酸化膜半導体電界効果トランジスタ(MOSFET)は、ソースと、ドレインと、ソースとドレイン間のチャネル領域とを有し、これら全てがソース及びドレインの導電型と逆導電型の基板内に形成されている。MOSFETは、ドレイン電極を非揮発性メモリセルに供給される主電圧Vccの供給源に接続しかつ、ソースからドレインの方へ延在するチャネル領域の一部を反転させるようにソース及び基板へ選択された電圧を供給することによって、プログラミングされる。チャネル領域の反転部分は、ドレインに達する前にピンチオフ点で終わる。ソース−基板間のPN接合の逆バイアスを制御することによって、反転領域のピンチオフ点がソースの方へ引き戻され、それによってMOSFETのプログラミング効率を増大させる。

(もっと読む)

半導体記憶装置

【課題】チャネル部の基板面を湾曲させたセルを有する半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、基板面から突出する凸部18が形成され、この凸部18の上端部は湾曲し、凸部18の根元は第1の幅W1を有する半導体基板11と、凸部18の根元の基板面上に形成され、凸部18の上面Dよりも低い上面Cを有し、第2の幅W2を有する第1の素子分離絶縁膜STI1と、凸部18内に形成され、第1及び第2の幅よりも狭い第3の幅W3を有する第2の素子分離絶縁膜STI2と、電荷蓄積層26を含むゲート絶縁膜40と、ゲート絶縁膜上に形成されたゲート電極28とを具備し、第1の素子分離絶縁膜STI1の上面の上方においてゲート電極28とゲート絶縁膜40とが接する第1の部分Aの高さは、第2の素子分離絶縁膜STI2の上面の上方においてゲート電極28とゲート絶縁膜とが接する第2の部分Bの高さより低い。

(もっと読む)

フローティングボディ素子及びバルクボディ素子を有する半導体素子及びその製造方法

【課題】フローティングボディ素子及びバルクボディ素子を有する半導体素子及びその製造方法を提供する。

【解決手段】この半導体素子の製造方法は、バルクボディ素子領域及びフローティングボディ素子領域を有する基板を準備する工程を含む。バルクボディ素子領域の基板の活性領域を画定するとともに、フローティングボディ素子領域のうち第1素子領域の基板上に順に積層された第1犠牲パターン及び第1活性パターンを画定する素子分離膜を形成する。フォトリソグラフィ及びエッチング工程を用いて素子分離膜に第1犠牲パターンの一部分を露出させる第1リセス領域を形成する。第1犠牲パターンを除去して第1活性パターン下部に第1空間を形成する。第1空間の内壁及び第1リセス領域の内壁に第1埋込誘電膜を形成する。第1埋込誘電膜を有する基板上に少なくとも第1空間を埋め込む第1埋込パターンを形成する。

(もっと読む)

不揮発性メモリ素子およびその製造方法

【課題】メモリヒステリシス特性を示すと同時に信頼性を改善した不揮発性メモリ素子を提供する。

【解決手段】半導体基板100と、半導体基板上に形成され、絶縁膜および絶縁膜内に埋め込まれた複数の炭素ナノクリスタルを含む電荷トラップ構造物150と、電荷トラップ構造物上に形成されたゲート160と、を含む。

(もっと読む)

半導体装置

【課題】ゲート絶縁膜中に電荷蓄積部を含む不揮発性メモリセルを有する半導体装置において、不揮発性メモリ領域の面積を縮小する。

【解決手段】メモリゲート電極11Aに、局所的に電界が集中するコーナー部11cnを設け、メモリゲート電極11A中の電荷をFNトンネル動作によりゲート絶縁膜2a中の電荷蓄積部に注入する消去方式を用いる。FNトンネルにより消去時の消費電流を低減できるため、メモリモジュールの電源回路面積を低減できる。また、書込みディスターブ耐性を向上できるために、より簡易なメモリアレイ構成を採用してメモリアレイ面積を低減できる。両者の効果を併せてメモリモジュールの面積を大幅に低減し製造コストを低減できる。また、書込み消去の注入電荷中心が一致するため書換え耐性が向上する。

(もっと読む)

フラッシュメモリ素子、その製造方法及び動作方法

【課題】フラッシュメモリ素子、その製造方法及び動作方法を提供する。

【解決手段】上端部分の両側に屈曲を有するように形成され、この両側の屈曲部分がプログラム時や消去時に電荷が注入される領域として使われ、電荷が注入される領域としきい電圧を決定する領域とを分離するチャンネル領域と、このチャンネル領域上に形成されたゲート構造と、を備えることを特徴とするメモリ素子、その製造方法及び動作方法である。

(もっと読む)

半導体素子

【課題】フローティングゲート構造を有し、駆動電圧を低減可能な半導体素子を提供する。

【解決手段】半導体素子10は、n型Siからなる基板1上に形成したSiO2層4上に、電荷蓄積層5,6を順次積層したフローティングゲート構造からなる。電荷蓄積層5は、アンドープのSiからなる量子ドット51a〜51cと、それを被覆する酸化層52とからなる。電荷蓄積層6は、n+Siからなる量子ドット61a〜61cと、それを被覆する酸化層62とからなる。そして、量子ドット61a〜61c中に元来的に存在する電子は、パッド12,13からゲート電極9に印加される電圧に応じて、トンネル接合を介して量子ドット61a〜61cと量子ドット51a〜51cとの間を移動し、量子ドット51a〜51cおよび/または量子ドット61a〜61c中に分布する。この分布状態は、電流ISDによって検出される。

(もっと読む)

半導体装置の製造方法及び基板処理装置

【課題】高い核密度形成に大きく寄与する事ができる半導体装置の製造方法及び基板処理装置を提供する。

【解決手段】本発明の半導体装置の製造方法は、表面に絶縁膜が形成されたウエハ200を反応管203内に搬送する工程と、反応管203内に少なくともシリコン系ガスを導入して、ウエハ200の表面に形成された絶縁膜上にシリコングレインを形成する処理を行う工程と、処理後の基板を反応管203から搬出する工程とを有し、処理工程では、シリコン系ガスを単独で導入した場合に、シリコン系ガスが熱分解しない温度と圧力に設定した反応管203内に、シリコン系ガスとドーパントガスとを導入し、ドーパントガスの流量をシリコン系ガスの流量と同等又はそれ以上とする。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】1電界効果トランジスタ当たり2ビットの情報を記憶でき、しかも微細化が容易な半導体記憶装置を提供すること。

【解決手段】半導体基板11、ゲート絶縁膜12、ゲート電極13、ゲート電極に対して側方に離間して形成された2つの電荷保持部61、62と、2つソース/ドレイン拡散層領域17、18と、チャネル領域41、42とを備える。電荷保持部61、62は、電荷を蓄積する機能を有する第1の材料からなるナノドット15が、第2の絶縁体14と第3の絶縁体16との間に挟まれた構造を有する。第2の絶縁体14と第3の絶縁体16とは互いに密度、材料または結晶構造が異なる。各電荷保持部61、62のナノドット15に保持された電荷の多寡に応じて、ゲート電極13に電圧を印加した際の一方の拡散層領域から他方の拡散層領域に流れる電流量を変化させるようになっている。

(もっと読む)

半導体装置の作製方法

【課題】大面積基板に、高性能な半導体素子、及び集積回路を高スループットで生産性よく作製することを目的とする。

【解決手段】単結晶半導体基板(ボンドウエハー)より単結晶半導体膜を転置する際、単結晶半導体基板を選択的にエッチング(溝加工ともいう)し、作製する半導体素子の大きさに複数に分割された複数の単結晶半導体層を、異種基板(ベース基板)に転置する。従って、ベース基板には、複数の島状の単結晶半導体層(SOI層)を形成することができる。

(もっと読む)

不揮発性半導体記憶装置

【課題】不揮発性半導体記憶装置の消去電流を低減する。

【解決手段】不揮発性半導体記憶装置のメモリセルは、半導体基板に形成されたソース領域とドレイン領域を有する。そして、ソース領域とドレイン領域の間の半導体基板上にゲート絶縁膜を介して選択ゲート電極が形成されている。選択ゲート電極の側壁には、下部酸化シリコン膜と電荷蓄積膜である酸窒化シリコン膜を介してメモリゲート電極が形成されている。このように構成されたメモリセルにおいて、以下のように消去動作を行なう。メモリゲート電極への正電圧の印加によってメモリゲート電極から酸窒化シリコン膜に正孔を注入して書き込み状態のしきい値電圧から一定レベルまでしきい値電圧を下げ、その後、バンド間トンネリング現象により発生したホットホールを酸窒化シリコン膜に注入して消去動作を完了する。

(もっと読む)

半導体メモリ、それを用いた半導体メモリシステム、および半導体メモリに用いられる量子ドットの製造方法

【課題】電荷蓄積効率が良い複合フローティングゲートの構成を有する半導体メモリを提供する。

【解決手段】半導体メモリ110は、半導体基板101上に形成した絶縁膜105上に、極薄Si酸化膜により被膜したSi系量子ドット311を積層し、その上に高誘電率絶縁膜322で被膜したシリサイド量子ドット321を積層し、さらに高誘電率絶縁膜412で被膜したSi系量子ドット411を積層した複合フローティング構造を有する。ゲート電極104に所定の正電圧を印加することで電子をシリサイド量子ドット321に蓄積し、ゲート電極104に所定の負電圧を印加および微弱な光を照射することにより当該電子を放出することで多値メモリ動作を高速かつ安定的に実行する。

(もっと読む)

半導体装置及びその作製方法

【課題】外部から局所的に圧力がかかっても破損しにくい半導体装置を提供する。また、外部からの局所的押圧による非破壊の信頼性が高い半導体装置を歩留まり高く作製する方法を提供する。

【解決手段】単結晶半導体領域を用いて形成された半導体素子を有する素子基板上に、有機化合物または無機化合物の高強度繊維に有機樹脂が含浸された構造体を設け、加熱圧着することにより、有機化合物または無機化合物の高強度繊維に有機樹脂が含浸された構造体及び素子基板が固着された半導体装置を作製する。

(もっと読む)

不揮発性半導体記憶装置

【課題】微細化に有利な、二重ウェル、及びこの二重ウェルから離れたウェルを備えた不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、第1導電型の半導体基板1内に形成された第1導電型の第1ウェル10と、第1ウェル10に形成された複数のメモリセルトランジスタQ5−1、Q5−2と、第1ウェル10の側面領域を囲む第1部分7、及び第1ウェル10の下部領域を囲む第2部分9を有し、第1ウェル10を半導体基板1から電気的に分離する第2導電型の第2ウェルと、半導体基板1内に形成された第2導電型の第3ウェル領域5と、を備える。

(もっと読む)

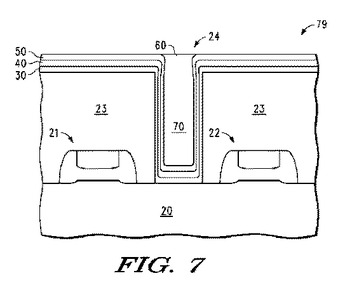

ボイドの無いコンタクトプラグ

コンタクトプラグを形成する半導体素子形成プロセスでは、チタンまたはタンタルコンタクト層(30)、窒化チタンバリア層(40)、及びタングステンシード層をコンタクト開口部(24)に順番に堆積させる。次に、コンタクトホール(24)への充填を、コンタクト開口部の底面から上に向かって、銅層(60)を電気メッキすることにより行なって、ボイドがコンタクト開口部(24)内に形成されることがないようにする。全ての余分な材料をCMPプロセスにより除去してコンタクトプラグ(70)を形成し、この場合、CMPプロセスを使用して、コンタクト層/シード層/バリア層(30,40,50)のうちの一つ以上の層を薄くする、または除去することもできる。  (もっと読む)

(もっと読む)

不揮発性メモリ素子、その製造方法及び半導体チップ

【課題】高集積化が容易であり、高い信頼性を持つ不揮発性メモリ素子及びその製造方法を提供する。

【解決手段】基板上105に形成され、第1導電型の第1ドーピング層115と、第1ドーピング層115から基板105の一面に対して上向きに伸長し、第1導電型と逆の導電性を有する第2導電型の半導体柱120と、半導体柱120の側壁を一回り取り囲む制御ゲート電極150aと、半導体柱120と制御ゲート電極150aとの間に介在された電荷保存層140aと、半導体柱120と電気的に連結されるように半導体柱120上に配置され、第1導電型の第2ドーピング層130と、を備える不揮発性メモリ素子。

(もっと読む)

不揮発性メモリ素子及びその製造方法

【課題】高集積化が容易で、且つ高い信頼性を有する不揮発性メモリ素子及びその製造方法を提供する。

【解決手段】本発明の不揮発性メモリ素子は、複数の第1半導体層、複数の第2半導体層、複数の第1ストレージノード、及び複数の第1制御ゲート電極を備える。複数の第1半導体層は、基板上に積層され、複数の第2半導体層は、複数の第1半導体層の間にそれぞれ介在して複数の第1半導体層の間に複数の第1トレンチを限定するように複数の第1半導体層の一端からリセスされ、複数の第1ストレージノードは、複数の第1トレンチの内部の第2半導体層の表面上に提供され、複数の第1制御ゲート電極は、複数の第1トレンチを満たすように複数の第1ストレージノード上に形成される。

(もっと読む)

電荷トラップ型メモリ素子

【課題】相対的に高い誘電定数と相対的に大きいバンドギャップを同時に確保できる物質で形成された電荷トラップ型メモリ素子及びその製造方法を提供する。

【解決手段】メモリ素子は、基板11上に形成されたトンネル絶縁膜21と、トンネル絶縁膜21上に形成された電荷トラップ層23と、電荷トラップ層23上にガドリニウム、またはこれより小さなサイズのランタン族元素を含む物質からなるブロッキング絶縁膜25と、を備える。ブロッキング絶縁膜25は、ガドリニウム、またはこれより小さなサイズのランタン族元素とアルミニウムとを含む物質からなる。

(もっと読む)

不揮発性メモリ素子の作動方法

【課題】電荷の安定化及び電子と正孔との再結合速度を向上させ、プログラム状態や消去状態で、反対電荷が電荷トラップ層内に残っていることを減らしたりまたは防止し、プログラム/消去状態の安定性を確保させる不揮発性メモリ素子の作動方法を提供する。

【解決手段】不揮発性メモリ素子にプログラムや消去に寄与するDCパルスと電荷の再結合や再配置を促進するAC摂動パルスとの複合パルスを印加してプログラムや消去を行う作動方法である。

(もっと読む)

複数のチャネル領域を互いに異なる高さに備える電子デバイス、およびその製造方法

不揮発性メモリセルを備える電子デバイスは、第1部分と第2部分を有する基板(10)を備える。第1部分の第1主面(111)は、第2部分の第2主面(113)よりも低い位置にある。電子デバイスは、第1部分上にある互いに不連続な複数の記憶素子を含む電荷ストレージスタック(12)を備え得る。電子デバイスは更に、第1部分上の制御ゲート電極(24)と、第2部分上において側壁スペーサ(74)を有する選択ゲート電極(94)とを備え得る。特定の実施形態において、電荷ストレージスタック(12)と制御ゲート電極(24)を形成するためにプロセスを用いてもよい。それぞれ異なる高さの複数の主面を有する基板を得るために、電荷ストレージスタック(12)と制御ゲート電極(94)の形成後に半導体層(40)を形成してもよい。選択ゲート電極(94)は半導体層(40)上に形成してもよい。  (もっと読む)

(もっと読む)

141 - 160 / 341

[ Back to top ]