Fターム[5F101BA54]の内容

不揮発性半導体メモリ (42,765) | 電荷蓄積機構 (9,664) | トラップ蓄積型 (3,039) | クラスタ (341)

Fターム[5F101BA54]に分類される特許

101 - 120 / 341

スプリット・ゲート・メモリ・デバイスの形成方法および装置

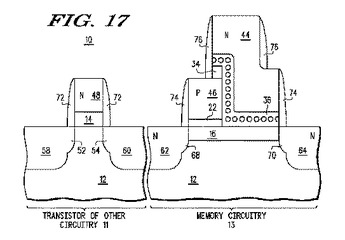

スプリット・ゲート・メモリ・デバイス(10)は、第1の仕事関数を有する選択ゲート(46)を基板(12)の第1の部分の上に有する。第2の仕事関数を有する制御ゲート(44)は、第1の部分に隣接する基板の第2の部分の上にある。スプリット・ゲート・メモリ・デバイス(10)の多数キャリアが電子であるとき、第1の仕事関数は第2の仕事関数よりも大きい。スプリット・ゲート・メモリ・デバイス(10)の多数キャリアがホールであるとき、第1の仕事関数は第2の仕事関数よりも小さい。基板(12)内の第1の電流電極(62)および第2の電流電極(64)は、制御ゲートおよび選択ゲートの下にあるチャネルによって分離される。制御ゲートおよび選択ゲートの異なる仕事関数は、デバイス性能を最適化するために各ゲートに対して異なる閾値電圧をもたらす。nチャネルデバイスでは、選択ゲートはp導電型であり、制御ゲートはn導電型である。  (もっと読む)

(もっと読む)

不揮発性メモリならびにその読み出し方法およびその書き込み方法

【課題】高セル密度化と、ビットラインの低抵抗化による高速化が両立し、読み出し、書き込み時の記憶内容への擾乱を受けにくい不揮発性メモリアレイを提供する。

【解決手段】複数のメモリセルは、接続領域411、第1の方向に延びる導電ビット線4010、第2の方向に延びる導電ワード線6030、および導電制御線6010,6020と共に2つの方向に2次元で配置されている。接続領域411は、1つのビット線に接続される4つのセルを含むメモリアレイを通って形成される。接続領域411は、処理を経済的にするために逆導電型領域401と同じ処理ステップで形成する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】微細化してもメモリセル間の干渉が少ない不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】シリコン基板上にそれぞれ複数の絶縁膜15及び電極膜WLを交互に積層させてメモリ積層体を形成する。このとき、電極膜WLはシリコンにより形成し、その内部にシリコン窒化物からなる粒子23を分散させる。次に、このメモリ積層体に貫通ホール20bを形成する。次に、熱酸化処理を行い、電極膜WLにおける貫通ホール20bに面した部分を酸化し、ゲート絶縁膜22を形成する。このとき、ゲート絶縁膜22内に粒子23が取り込まれる。次に、貫通ホール20bの側面上にトンネル絶縁膜24を形成し、貫通ホール20bの内部にシリコンピラーSPを埋設する。このようにして製造された不揮発性半導体記憶装置1においては、粒子23がメモリセルの電荷蓄積部分となる。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】一度の酸化処理でONO膜の上側酸化膜を下側酸化膜よりも厚く形成することができるミラービットの半導体装置の製造方法を提供する。

【解決手段】基板10上に第1酸化膜11、この第1酸化膜11よりも膜厚が薄い窒化膜12、第1酸化膜11よりも膜厚が薄い第2酸化膜13、及びゲート電極14を積層する工程と、第1酸化膜11の端部及び第2酸化膜13の端部を除去して窒化膜12を一部露出する工程と、第1酸化膜11が除去された基板10上に第3酸化膜15を形成すると同時に、窒化膜12の露出部分を酸化して第4酸化膜16を形成し且つゲート電極14の周囲に第5酸化膜17を形成して、第4酸化膜16と第5酸化膜17とが一体化した、第3酸化膜15よりも厚い酸化膜を形成する工程と、第3酸化膜15と第4酸化膜16との間に電荷蓄積層18aを形成する工程と、をこの順に行う。

(もっと読む)

金属ドープ層の形成方法、成膜装置及び記憶媒体

【課題】金属ドープ層を形成するに際して、金属を低濃度の領域において制御性良くドープさせることができると共に、膜厚方向における金属の濃度分布を制御することが可能な金属ドープ層の形成方法を提供する。

【解決手段】真空排気が可能になされた処理容器4内で被処理体Wの表面に金属が含まれた金属ドープ層100を形成する金属ドープ層の形成方法において、絶縁層原料ガスを用いて絶縁層を形成する絶縁層形成工程と、金属を含む金属層原料ガスを用いて金属層104を形成する金属層形成工程とを、金属層形成工程が少なくとも1回含まれるように交互に繰り返し行うようにする。これにより、金属を低濃度の領域において制御性良くドープさせる。

(もっと読む)

半導体記憶装置

【課題】不揮発性メモリの高速化を小面積で実現する。

【解決手段】例えば、SRAMに代表される低集積で高速なメモリアレイ53を半導体基板上に形成し、その上層にフラッシュメモリに代表される高集積で低速なメモリアレイ54を形成する。メモリアレイ54は、各メモリセルのチャネルが縦方向に形成され、小面積での大容量化が図られている。メモリアレイ53とメモリアレイ54は、データ線等が適宜共通化されており、外部からメモリアレイ54に書き込みを行う際には、メモリアレイ53に書き込みを行い、メモリアレイ53からメモリアレイ54に転送を行う。

(もっと読む)

半導体集積回路装置の製造方法

【課題】記憶情報を高速に読み出す半導体集積回路装置の製造方法を提供する。

【解決手段】本発明の半導体集積回路装置の製造方法は、半導体基板上に第1ゲート電極を形成する工程、この工程の後に第1ゲート電極を覆うように半導体基板上に導電性膜を形成する工程、この工程の後に導電性膜の一部を覆うように半導体基板上にマスクパターンを形成する工程、この工程の後にドライエッチングを行いマスクパターンで覆われていない導電性膜をサイドスペーサ状の第2ゲート電極に加工する工程で、且つマスクパターンで覆われた導電性膜を第2ゲート電極のコンタクト領域としてパターニングする工程、この工程の後にマスクパターンを除去する工程、この工程の後に不揮発性メモリセルを覆うように半導体基板上に層間絶縁膜を形成する工程、この工程の後に層間絶縁膜中に第2ゲート電極のコンタクト領域に接続するプラグを形成する工程、を有する。

(もっと読む)

マイクロコンピュータ及びデータプロセッサ

【課題】不揮発性メモリセルから記憶情報を高速に読み出すことができる半導体装置を提供する。

【解決手段】マイクロコンピュータは、内部バス68と、前記内部バスに結合されている中央演算部61と、前記内部バスに結合された不揮発性メモリ63とを含む。前記不揮発性メモリは、第1ゲートと第2ゲートとを含む複数の不揮発メモリセルと、前記複数の不揮発メモリセルの一つの前記第1ゲートに結合された第1回路21と、前記複数の不揮発メモリセルの一つの前記第2ゲートに結合された第2回路22と、前記第1回路に供給する第1電圧と前記第2回路に供給する第2電圧とを生成する電圧生成回路VS,77と、を含む。前記第1回路のゲート耐圧は前記第2回路のゲート耐圧より低い。

(もっと読む)

半導体装置、及び半導体装置の製造方法

【課題】ゲート絶縁膜や層間絶縁膜を熱的に安定な高誘電率絶縁膜から構成し、半導体装置を製造する際の熱処理を経ても、前記高誘電率絶縁膜の、他の構成部材との反応を抑制し、前記半導体装置の特性変動を抑制する。

【解決手段】側壁をSiO2、SiN及びSiONの少なくとも一つから構成し、上部絶縁膜又はゲート絶縁膜を、希土類金属、Y、Zr、及びHfからなる群より選ばれる少なくとも一つの金属M、Al及びSiの酸化物から構成し、金属Mに対するSiの個数比Si/Mを、金属MとAlとの複合酸化物中のSiO2固溶限における比率以上であるとともに、前記上部絶縁膜又は前記ゲート絶縁膜の誘電率をAl2O3と一致する比率以下とし、金属Mに対するAlの個数比Al/Mを、Alの作用で金属Mの酸化物の結晶化を抑制する比率以上であるとともに、金属Mの作用でAl2O3の結晶化を抑制する比率以下として、半導体装置を構成する。

(もっと読む)

埋め込み型トラッピング層によるトランジスタの閾値電圧の調整方法

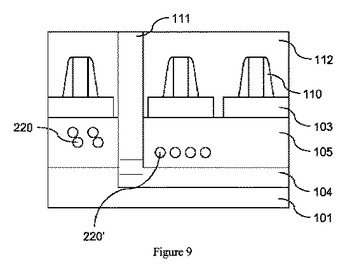

方法は、電子サブアセンブリの形成について、調整可能な閾値電圧を有する少なくとも1つの第1のトランジスタ(110)を担持する半導体層(103)が絶縁層(102、105)に接合される組み立てステップと、半導体層および第1のトラッピングゾーンが容量結合されるように、第1のトラッピングゾーン(220)が所定の第1の深さで絶縁層に形成される形成ステップであって、前記第1のトラッピングゾーンが、前記第1のトランジスタのチャネルの少なくとも下に延び、かつ前記第1のトラッピングゾーンの外側のトラップの密度より高い密度のトラップを有する形成ステップとを含み、前記第1のトランジスタからの有用な情報はこのトランジスタ内の電荷移動である。具体的な実施形態において、第2のトランジスタのチャネルの少なくとも下に延びる第2のトラッピングゾーンが、第1のトラッピングゾーンに使用されるのとは異なるエネルギーおよび/または用量および/または原子の第2の注入によって形成される。  (もっと読む)

(もっと読む)

不揮発性半導体記憶素子及びその製造方法並びに表示装置

【課題】複雑な工程を経ることなく不揮発性半導体記憶素子を製造する。

【解決手段】不揮発性半導体記憶素子10は、絶縁基板11と、絶縁基板11上に設けられ、ソース領域13s、チャネル領域13c、及びドレイン領域13dが形成された半導体層13と、半導体層13を覆うように設けられたゲート絶縁膜14と、ゲート絶縁膜14内に、半導体層13のチャネル領域13cに対応するように埋設されたメモリ用金属粒子層15と、ゲート絶縁膜14上に、半導体層13のチャネル領域13cに対応するように設けられたゲート電極16と、を備える。

(もっと読む)

半導体素子及び半導体装置

【課題】短チャネル効果が抑制され高い電流駆動力を有する細線半導体素子を実現する。

【解決手段】半導体基板上に設けられた絶縁領域と、絶縁領域上に略平行に整列して設けられた第一導電型の複数の線状半導体層と、各線状半導体層に離間して設けられた第二導電型のソース・ドレイン領域と、ソース・ドレイン領域の間に設けられたチャネル領域と、各線状半導体層の上面と側面上に設けられた第一の絶縁膜と、第一の絶縁膜上に設けられ、複数の線状半導体層と交差するように連続的に設けられたゲート電極とを有し、線状半導体層を線方向に流れる電流に垂直、且つ基板表面に平行に測ったチャネル領域の長さが、チャネル領域中の不純物濃度で決まる最大空乏層幅の二倍以下であり、複数の線状半導体層の間隔が、線状半導体層の上面とゲート電極との間隔の二倍以下であり、絶縁領域の表面の少なくとも一部に於ける誘電率が、酸化シリコンの誘電率よりも低い。

(もっと読む)

不揮発性半導体記憶素子、不揮発性半導体記憶装置、不揮発性半導体記憶素子のデータ書き込み方法、および、不揮発性半導体記憶装置のデータ書き換え方法

【課題】スケーラビリティが高く、ビットまたはバイト単位の書き換えが可能な不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶素子をマトリックスに配列し、Y側にページバッファを設ける。1本のワード線に接続されたメモリセルのデータをページバッファに読み出したのち、これらのメモリセルのデータを消去する。そして、ページバッファに読み出したデータのうち1または複数のデータを書き換え、書き換えられたページバッファの内容を前記1本のワード線に接続された各メモリセルに書き戻す。これを高速に行うことにより、ビットまたはバイト単位の書き換えをエミュレートする。

(もっと読む)

半導体集積回路装置及びその製造方法

【課題】 非導電性の電荷トラップ膜を電荷蓄積領域として用いる不揮発性メモリの読み出し電流を大幅に向上させることができ、また、読み出しディスターブによるデータ反転の読み出し不良を撲滅できる半導体集積回路装置を提供する。

【解決手段】 半導体集積回路装置は、半導体柱と絶縁体柱が一方向に交互に敷き詰めた状態で複数配置された柱列と、前記複数の半導体柱に夫々設けられた複数の不揮発性記憶素子であって、前記半導体柱の前記一方向に沿う側面にゲート絶縁膜を介在して制御ゲート電極が設けられ、前記半導体柱の上面部にドレイン領域が設けられ、かつ前記半導体柱の底面部にソース領域が設けられた複数の不揮発性記憶素子と、前記複数の不揮発性記憶素子の夫々の制御ゲート電極を含み、かつ前記柱列の前記一方向に沿う側面に前記一方向に沿って設けられた配線とを有する。

(もっと読む)

Si及び金属ナノ結晶核形成のためのプラズマ表面処理

【課題】 不揮発性メモリデバイスのようなデバイス、及び統合プロセスツールにおいてデバイスを形成する方法の提供。

【解決手段】 トンネル酸化物層を基板上に堆積させるステップと、トンネル酸化物層をプラズマに曝し、その結果、プラズマがトンネル酸化物の表面と近傍表面の形態を変化させ、プラズマ変化した近傍表面を形成するステップと、を含む。その後、トンネル酸化物の変化した近傍表面上にナノ結晶を堆積させる

(もっと読む)

半導体装置

【課題】不揮発性メモリセルを備えた半導体装置の高信頼度化を図る。

【解決手段】複数のメモリセルから構成されたメモリアレイに対して電気的に接続された電子回路が、メモリセルを構成する選択ゲート、メモリゲート、ウェル、ソース、およびドレインに電圧を印加し、書込み、消去、緩和パルス印加、ベリファイなどの動作の制御を行う。緩和パルス印加では、電荷蓄積膜の選択ゲート側にホールが電子より多く分布している状態において、選択ゲートに正電圧を印加し、メモリゲートに0Vを印加して、ホールと電子とを結合させて、電荷蓄積膜中の電荷を安定化させる。

(もっと読む)

半導体記憶装置及びその製造方法と半導体記憶装置の動作方法

【課題】書込み速度の向上と、かつ読出しディスターブの抑制を両立させることが可能な半導体記憶装置を提供する。

【解決手段】半導体層上に電荷蓄積膜とゲート電極105を形成し、ゲート電極105の下部に形成されたチャネル領域の両側の半導体層に2つの第1導電型の拡散領域A及びBを形成する。チャネル領域は、一方の拡散領域Aが接する側のチャネル幅Waよりも他方の拡散領域Bが接する側のチャネル幅Wbの方が大きく形成される。記憶動作時には一方の拡散領域Aへ他方の拡散領域Bよりも高い電圧を印加し、読出し時には他方の拡散領域Bへ一方の拡散領域Aよりも高い電圧を印加する。

(もっと読む)

メモリセルおよびその製造方法

メモリセルを開示する。メモリセルは、第1ワイヤ状チャネル構造と、第1ワイヤ状チャネル構造の外周面を囲む電荷トラップ構造を備え、電荷トラップ構造は、2つの電荷トラップ部分構造を有する。各電荷トラップ部分構造は、電荷を蓄積可能な異なる材料で形成されている。メモリセルの製造方法も開示する。 (もっと読む)

半導体記憶装置およびその製造方法

【課題】デバイス間バラツキや誤動作が起こりにくく信頼性の高い、かつ消費電力が抑えられた不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、絶縁体上に形成された第1導電型の半導体層100と、半導体層100上に形成された電荷蓄積機能を有する電荷蓄積膜103及び電荷蓄積膜103上に形成されたゲート電極105aと、ゲート電極105aの下方の半導体層100に形成されたチャネル領域108と、チャネル領域108の両側に、半導体層100内に形成された第2導電型の拡散領域106,107と、半導体層100を延長して形成した第1導電型のボディコンタクト領域109と、延長した半導体層100上にゲート電極105aを延長し、ボディコンタクト領域109と、チャネル領域108の両側の拡散領域106,107を分離するゲート電極引き出し部105bとを備える。

(もっと読む)

シリコンドット形成方法及びシリコンドット形成装置

【課題】低温で基板上に直接粒径の揃ったシリコンドットを均一な密度分布で形成する方法及び装置を提供する。

【解決手段】シリコンスパッタターゲット30と基体Sを配置したチャンバ1内に水素ガスを導入し、該ガスに高周波電力を印加してチャンバ1内に、プラズマ発光において波長288nmにおけるシリコン原子の発光強度Si(288nm) と波長484nmにおける水素原子の発光強度Hβとの比〔Si(288nm) /Hβ〕が10.0以下であるプラズマを発生させ、該プラズマでターゲット30をケミカルスパッタリングして500℃以下の低温で基体上に直接、粒径が20nm以下のシリコンドットを形成する。

(もっと読む)

101 - 120 / 341

[ Back to top ]