Fターム[5F101BA54]の内容

不揮発性半導体メモリ (42,765) | 電荷蓄積機構 (9,664) | トラップ蓄積型 (3,039) | クラスタ (341)

Fターム[5F101BA54]に分類される特許

21 - 40 / 341

フラッシュEEPROM(FLASHEEPROMMEMORY)の消去方法

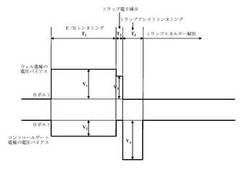

【課題】電荷の蓄積を制御することによりメモリセルを消去するフラッシュEEPROMの消去方法を提供する。

【解決手段】フラッシュメモリの消去方法は、F/Nトンネリング期間において、ウェル電極と第二半導体領域に対し正極性の第一電圧バイアスを印加し、且つコントロールゲート電極に対し負極性の第二電圧バイアスを印加するステップと、F/Nトンネリング期間のあとのトラップ減少期間において、ウェル電極と第二半導体領域に対し正極性の第三電圧バイアスを印加し、且つコントロールゲート電極に対し第一ゼロ電圧バイアスを印加するステップと、トラップ減少期間のあとのトラップアシストトンネリング期間において、コントロールゲート電極に対し負極性の第四電圧バイアスを印加し、且つウェル電極と第二半導体領域に対し第二ゼロ電圧バイアスを印加するステップと、を有する。

(もっと読む)

太陽電池

【課題】高温ポストアニールのステップを必要とせず、従来の低温ポリシリコン薄膜トラ

ンジスタと集積可能な、高効率の太陽電池を提供する。

【解決手段】基板と、前記基板上に形成された第1導電層と、前記第1導電層上に形成されたNドープまたはPドープの第1半導体層と、前記第1半導体層上に形成され、複数のレーザー誘起凝集シリコンナノドットを有するシリコンリッチ誘電体層と、前記シリコンリッチ誘電体層上に形成されたNドープまたはPドープの第2半導体層と、前記第2半導体層上に形成された第2導電層と、を含み、前記基板、前記第1導電層、および前記第1半導体層と、前記第2半導体層および前記第2導電層と、のいずれかは、透明材料からなることを特徴とする太陽電池。

(もっと読む)

不揮発性記憶素子及びその製造方法

【課題】 信頼性を向上可能な不揮発性記憶素子及びその製造方法を提供する。

【解決手段】 不揮発性素子は、基板100、基板100の上に形成され、制御ベースゲート120a及び制御ベースゲート120aの上に形成される制御金属ゲート125anを有する制御ゲート電極137、制御ゲート電極137と基板100との間に形成される電荷格納領域110a、制御ゲート電極137の上に形成される制御ゲートマスクパターン130、及び制御ゲートマスクパターン130及び制御ベースゲート120aの間に形成された制御金属ゲート125aの側壁の上に形成される酸化防止スペーサ135aを備える。このとき、制御金属ゲート125anの幅は、制御ゲートマスクパターン130の幅より小さくなるように形成されている。これにより、制御金属ゲート125anが酸化工程又は酸化物等によって酸化されることを防止することができる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】特性を向上させる不揮発性メモリを有する半導体装置を提供する。

【解決手段】半導体装置を、制御ゲート電極CGと、制御ゲート電極CGと隣合うように配置されたメモリゲート電極MGと、絶縁膜3と、その内部に電荷蓄積部を有する絶縁膜5と、を有するよう構成する。このうち、メモリゲート電極MGは、絶縁膜5上に位置する第1シリコン領域6aと、第1シリコン領域6aの上方に位置する第2シリコン領域6bと、を有するシリコン膜よりなり、第2シリコン領域6bは、p型不純物を含有し、第1シリコン領域6aのp型不純物の濃度は、第2シリコン領域6bのp型不純物の濃度よりも低く構成する。

(もっと読む)

3次元半導体素子及びその製造方法

【課題】工程不良を無くして収率を向上させることができる3次元半導体素子及びその製造方法が提供される。

【解決手段】3次元(3D)半導体メモリー素子は、基板に隣接する下段から上段まで伸張して、複数個のメモリーセルと連結された垂直チャンネルと、前記複数個のメモリーセルを有し、前記基板上に配置された階段形構造のゲートスタック形態にアレイされたセルアレイと、を含む。前記ゲートスタックは、前記下段に隣接する下部非メモリートランジスターに連結された下部選択ラインを含む下部膜と、前記上段に隣接する上部非メモリートランジスターに各々連結され、互いに連結されて単一の導電性ピースになって上部選択ラインをなす導電ラインを有する複数個の上部膜と、各々ワードラインを有し、セルトランジスターと連結され、前記下部選択ラインと前記上部選択ラインの間に配置される複数個の中間膜と、を含む。

(もっと読む)

半導体装置

【課題】パーコレーションリークを抑制可能な構造を有する半導体装置を提供する。

【解決手段】ソース領域18、ドレイン領域18及びチャネル領域を有する半導体領域と、チャネル領域上に形成された第1のトンネル絶縁膜12と、第1のトンネル絶縁膜上に形成され、エネルギー障壁を有する障壁層13と、障壁層上に形成された第2のトンネル絶縁膜14と、第2のトンネル絶縁膜上に形成され、SiY(SiO2)X(Si3N4)1-X (ただし、0≦X≦1、Y>0)で表される絶縁膜を具備する電荷蓄積部15と、電荷蓄積部上に形成され、エネルギー障壁の高さを制御する制御電極17とを備え、X及びYは、[2×2X/(4−2X)+(4−4X)/(4−2X)]×[Y/(Y+7−4X)]≧0.016 なる関係を満たし、障壁層は、クーロンブロッケイド条件を満たす導電性微粒子を含んだ微粒子層で形成されている。

(もっと読む)

半導体素子およびその製造方法

【課題】二酸化シリコンとシリコンとの良好な界面特性を有し、絶縁基板上に作製された半導体素子を提供する。

【解決手段】半導体素子10は、多結晶シリコン膜4と、絶縁膜5,9と、金属量子ドット8とを備える。多結晶シリコン膜4は、絶縁基板1上に配置され、アモルファスシリコン膜を熱プラズマジェットによってアニールして作製される。絶縁膜5は、SiO2からなり、多結晶シリコン膜4に接して多結晶シリコン膜4上に形成される。金属量子ドット8は、Ptからなり、Pt薄膜を熱プラズマジェットによってアニールして絶縁膜5上に形成される。絶縁膜9は、SiO2からなり、金属量子ドット8を覆うように絶縁膜5上に形成される。

(もっと読む)

不揮発性メモリー装置の製造方法

【課題】不揮発性メモリー装置の製造方法であって、特に半導体パターン厚さの均一性が向上される3次元半導体装置の製造方法、及び当該製造方法によって製造された3次元半導体装置を提供する。

【解決手段】この製造方法は、基板10の上に複数の第1の膜(鋳型膜)120及び複数の第2の膜(犠牲膜)が交互に積層された積層膜構造体を形成する段階、積層膜構造体を貫通する開口部、及び開口部周囲にアンダーカット領域を形成する段階、アンダーカット領域に局所的に配置される絶縁スペーサー155を形成する段階、絶縁スペーサー155が形成された開口部内に半導体パターン165を形成する段階を含む。

(もっと読む)

半導体素子用パターン構造物の形成方法

【課題】ラインパターン構造物の形成方法を提供すること。

【解決手段】ラインパターン構造物及びその形成方法において、ラインパターン構造物は切断部位を含むライン形状を有する少なくとも1つの第1ラインパターンを含む。最外郭に位置する前記第1ラインパターンと隣り合って前記第1ラインパターンと平行した延在ラインと、前記第1ラインパターンの切断部位と隣接する領域で前記第1ラインパターン方向へ向かうように前記延在ラインから突出された少なくとも1つの突出パターンを含む2つの第2ラインパターンを含む。前記ラインパターン構造物は不良が減少し、簡単な工程を通じて形成されてもよい。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】書込・消去特性が高く、動作の信頼性が高い半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体記憶装置は、半導体基板と、前記半導体基板上に設けられたトンネル絶縁膜と、前記トンネル絶縁膜上に設けられた第1電極と、前記第1電極上に設けられた電極間絶縁膜と、前記電極間絶縁膜上に設けられた第2電極と、を備える。前記電極間絶縁膜は、積層絶縁層と、前記積層絶縁層上に設けられ、前記積層絶縁層よりもバリアハイトが低い電荷蓄積層と、前記電荷蓄積層上に設けられ、前記電荷蓄積層よりもバリアハイトが高いブロック絶縁層と、を有する。前記積層絶縁層は、第1絶縁層と、前記第1絶縁層上に設けられ、前記第1絶縁層よりもバリアハイトが低い量子効果層と、前記量子効果層上に設けられ、前記量子効果層よりもバリアハイトが高い第2絶縁層と、を有する。

(もっと読む)

酸化チタン粒子、その製造方法、磁気メモリ、光情報記録媒体及び電荷蓄積型メモリ

【課題】従来にない新規な物性を発現し得る酸化チタン粒子及びその製造方法と、それを用いた磁気メモリ、光情報記録媒体及び電荷蓄積型メモリを提供する。

【解決手段】逆ミセル法を利用せずに、ゾル−ゲル法によってシリカ被覆水酸化チタン化合物粒子を直接製造し、当該シリカ被覆水酸化チタン化合物粒子を焼成処理する。これにより、温度が約460K付近において非磁性半導体と常磁性金属とに相転移する従来におけるバルク体とは異なり、室温で相転移せずに、全ての温度領域において、Ti3O5粒子本体が常磁性金属の特性を常に維持することができるという従来にない新規な物性を発現し得る酸化チタン粒子1を提供できる。

(もっと読む)

酸化チタン粒子、その製造方法、磁気メモリ、光情報記録媒体及び電荷蓄積型メモリ

【課題】従来にない新規な物性を発現し得る酸化チタン粒子、光情報記録媒体及びその製造方法と、それを用いた磁気メモリ及び電荷蓄積型メモリを提供する。

【解決手段】Ti3O5粒子本体2を形成した際に、Ti3O5粒子本体2の表面を覆っていたシリカガラスが除去された形状を有し、また、温度が約460K付近において非磁性半導体と常磁性金属とに相転移する従来におけるバルク体とは異なり、室温で相転移せずに、全ての温度領域において、Ti3O5粒子本体が常磁性金属の特性を常に維持することができるという従来にない新規な物性を発現し得る酸化チタン粒子1を提供できる。

(もっと読む)

半導体装置およびその製造方法

【課題】高耐圧MISFETを含む半導体装置の信頼性向上を図ることができる技術を提供する。

【解決手段】高耐圧MISFETQ4のゲート絶縁膜GOX4を、酸化シリコン膜と窒化シリコン膜という異なる種類の膜から形成する。具体的に、高耐圧MISFETQ4では、ゲート絶縁膜GOX4を、酸化シリコン膜PREOX1と、この酸化シリコン膜PREOX1上に形成された酸化シリコン膜OX1と、酸化シリコン膜OX1上に形成された窒化シリコン膜SN1と、窒化シリコン膜SN1上に形成された酸化シリコン膜OX2から形成している。

(もっと読む)

不揮発性半導体記憶装置

【課題】各メモリセルの書込消去特性を極力一定にできる不揮発性半導体記憶装置を提供する。

【解決手段】複数のメモリセルトランジスタMTは、活性領域Saが素子分離溝2によって互いに分離している。これらのメモリセルトランジスタMTは、それぞれ、活性領域Saの上面上または上方にトンネル絶縁膜3を介して電荷蓄積機能を有する電荷トラップ膜4を備えている。積層絶縁膜Bは、トンネル絶縁膜3および電荷トラップ膜4を少なくとも含んで構成され、トンネル絶縁膜3が素子分離溝2の内面に沿って形成されると共に電荷トラップ膜4がトンネル絶縁膜3の上面に沿って積層されており、素子分離溝2内の全領域に埋込まれている。

(もっと読む)

半導体装置

【課題】不揮発性メモリと容量素子を有し、性能を向上させる半導体装置を提供する。

【解決手段】スプリットゲート型の不揮発性メモリのメモリゲート電極MG6nとp型ウエルPW1との間および制御ゲート電極CG4nとメモリゲート電極MG6nとの間には、内部に電荷蓄積層5bを有する絶縁膜5が形成されている。この絶縁膜5は、酸化シリコン膜5aと、その上に形成された窒化シリコン膜5bと、その上に形成された酸化シリコン膜5cと、その上に形成されかつ酸化シリコン膜5cよりも薄い絶縁膜5dとの積層膜からなる。この絶縁膜5dは、ポリシリコンからなるメモリゲート電極MG6nに接している。絶縁膜5dは、Hf,Zr,Al,Ta,Laのうちの少なくとも1種を含む金属化合物により形成されているため、フェルミピニングを生じることができ、誘電率が高い。

(もっと読む)

半導体記憶素子、及び半導体記憶装置

【課題】 高効率に電荷を蓄積及び消去することができ、かつ蓄積した電荷を長時間保持することができる半導体記憶素子、及び半導体記憶装置を提供する

【解決手段】 半導体層19と、半導体層19上に設けられたトンネル絶縁膜18と、トンネル絶縁膜18上に設けられ、膜厚が0.9nm以上2.8nm以下であり、立方晶ハフニア粒子17を含む電荷蓄積膜16と、電荷蓄積膜16上に設けられたブロック絶縁膜15と、ブロック絶縁膜15上に設けられた制御電極13とを備えることを特徴とする半導体記憶素子。

(もっと読む)

3次元半導体装置

【課題】3次元的に配列される導電パターンの厚さを増加しその抵抗を減少できる3次元半導体装置を提供する。

【解決手段】この装置は基板上に順に積層された水平構造体と、水平構造体を垂直に横切る垂直構造体とを具備する。水平構造体の各々は基板に平行な導電ライン及び垂直構造体に隣接した導電ラインの一側壁を覆う第2パターンを含む。また垂直構造体の各々は半導体柱及び水平構造体に隣接した半導体柱の少なくとも一側壁を覆う第1パターンを含む。

基板上に順に積層された電極を含む電極構造体と、電極構造体を垂直に貫通する半導体パターンと、第1パターン及び第2パターンを具備して半導体パターンと電極構造体との間に介在するメモリー要素と、を含み、第1パターンは垂直に延長されて複数の電極を横切り、第2パターンは水平に延長されて複数の半導体パターンを横切る。

(もっと読む)

半導体記憶装置、及びその製造方法

【課題】 高効率に電荷を蓄積及び消去することができ、かつ蓄積した電荷を長時間保持することができる半導体記憶装置、及びその製造方法を提供する。

【解決手段】 半導体記憶装置10は、半導体基板11と、半導体基板11内に離間して設けられたソース領域3及びドレイン領域2と、ソース領域3とドレイン領域2との間であって半導体基板11上に設けられたトンネル絶縁膜12と、トンネル絶縁膜12上に設けられ、酸化物クラスターを含む電荷蓄積膜13と、電荷蓄積膜13上に設けられたブロック絶縁膜14と、ブロック絶縁膜14上に設けられたゲート電極15とを備える。

(もっと読む)

電気的浸透性ソース層を含む半導体デバイス及びこれの製造方法

電気的浸透性ソース層を含む半導体デバイス及びこれの製造方法に対する様々な実施例が与えられる。一実施例では、半導体デバイスは、ゲート層、誘電体層、メモリ層、ソース層、半導体チャネル層、及びドレイン層を含む。ソース層は電気的浸透性及びパーフォレーションを有する。半導体チャネル層はソース層及びメモリ層と接触する。ソース層及び半導体チャネル層は、ゲート電圧チューナブル電荷注入バリアを形成する。  (もっと読む)

(もっと読む)

不揮発性半導体メモリ

【課題】 従来のMONOSは、SiNに電荷を蓄積する構成であるが、電荷蓄積量が不十分であり閾値電圧変化幅を大きく取れず、またHfO2,ZrO2,TiO2中へLa系元素を導入した技術ではドーパント導入による電荷の高密度化は実現が困難である。

【解決手段】 窒化シリコン膜よりも十分に誘電率の高いZr酸化物、Hf酸化物等の窒化シリコンよりも十分に高い誘電率を有する金属酸化物を母体材料として、その中に電子の出し入れが可能なトラップレベルを発生させるために、価数が2つ上(VI価)以上の高価数物質を適量添加する構成の電荷蓄積層を有する不揮発性半導体メモリである。

(もっと読む)

21 - 40 / 341

[ Back to top ]