Fターム[5F101BA54]の内容

不揮発性半導体メモリ (42,765) | 電荷蓄積機構 (9,664) | トラップ蓄積型 (3,039) | クラスタ (341)

Fターム[5F101BA54]に分類される特許

41 - 60 / 341

3次元半導体装置の配線構造体

【課題】集積度及び信頼性を共に向上させた3次元半導体装置を提供する。

【解決手段】3次元半導体装置の配線構造が提供される。3次元半導体装置は3次元基板上に2次元的に配列された積層構造体、第1配線を含み、積層構造体の上部に配置される第1配線層及び第2配線を含み、第1配線層の上部に配置される第2配線層を含み、積層構造体各々は順次に積層された複数の下部ワードラインを含む下部構造体及び順次に積層された複数の上部ワードラインを含み、下部構造体の上部に配置される上部構造体を含み、第1配線各々は下部ワードラインの内の何れか1つに連結し、第2配線各々は上部ワードラインの内の何れか1つに連結する。

(もっと読む)

半導体記憶装置

【課題】スプリットゲート型のMONOSメモリセルを有する半導体記憶装置において、SSI方式による書込み時のディスターブ耐性を向上させる。また、非選択メモリセルのディスターブ耐性が向上することにより、メモリモジュールの面積を低減させる。

【解決手段】メモリゲート電極12の側面において、電荷蓄積膜9と絶縁膜11との間に絶縁膜10を形成し、メモリゲート電極12側面の絶縁膜10および11の合計の厚さを、メモリゲート電極12下部の絶縁膜11の厚さよりも厚く形成する。

(もっと読む)

スプリットゲート不揮発性メモリセルの作製に有用な半導体構造を形成する方法

半導体層(12)に半導体デバイス(10)を形成する方法が提供される。方法は、半導体層(12)の上方に選択ゲート誘電体層(14)を形成すること、選択ゲート誘電体層(14)の上方に選択ゲート層(16)を形成すること、選択ゲート層の少なくとも一部分を除去することによって、選択ゲート層(16)の側壁を形成することを含む。方法は、選択ゲート層(16)の側壁の少なくとも一部分に、および選択ゲート層(16)の少なくとも一部分の下に、犠牲層(22)を成長させること、犠牲層(22)を除去して、選択ゲート層の側壁の少なくとも一部分の表面および選択ゲート層の下の半導体層の表面を露出させることをさらに含む。方法は、制御ゲート誘電体層(28)、電荷蓄積層(32)、および制御ゲート層(34)を形成することをさらに含む。 (もっと読む)

半導体装置

【課題】不揮発性メモリを構成するメモリセルのサイズを縮小できる技術を提供する。

【解決手段】本発明では、ソース線S1がメモリセルMC1AとメモリセルMC8Aで共通となっている。これにより、メモリセルMC1AやメモリセルMC8Aごとに電気的に独立したソース線を設ける必要がなく、メモリセルのサイズを縮小化することができる。具体的に、共通するソース線S1は、ビット線D1やビット線D8と並行するように配置されているのではなく、選択ゲート線CGL1やメモリゲート線MGL1と並行するように延在している。これにより、メモリセルMC1A〜メモリセルMC8A間の間隔を狭めることができるので、メモリセルアレイ全体の占有面積を縮小化することができる。このソース線S1は、メモリセルMC1B〜メモリセルMC8Bとも共通化されている。

(もっと読む)

半導体集積回路装置の製造方法

【課題】共通ゲートを有する複数のトランジスタセルをアレー状に配置する構成を持つ不揮発性半導体集積回路装置において、STI領域のパターニング工程でのパターンの変形を防ぐ製造方法を提供する。

【解決手段】半導体メモリ等のメモリセルアレー等の露光において、矩形形状のSTI溝領域エッチング用単位開口を行列状に配置したSTI溝領域エッチング用単位開口群をネガ型レジスト膜28上に露光するに際して、列方向に延びる第1の線状開口群を有する第1の光学マスクを用いた第1の露光ステップと、行方向に延びる第2の線状開口群を有する第2の光学マスクを用いた第2の露光ステップとを含む多重露光を適用する。直行する2方向において、それぞれの方向に対してマスクを用いて露光を行うことで、矩形形状48の端部における近接効果を回避することができ、矩形形状48の端部が丸みを帯びるのを回避することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリを形成した半導体チップを充分に縮小化することができる技術を提供する。また、不揮発性メモリの信頼性を確保することができる技術を提供する。

【解決手段】本発明のメモリセルでは、コントロールゲート電極CG上に絶縁膜IF1を介してブーストゲート電極BGが形成されている。このブーストゲート電極BGは、メモリゲート電極MGとの間の容量カップリングにより、メモリゲート電極MGに印加される電圧を昇圧する機能を有している。つまり、メモリセルの書き込み動作や消去動作の際、メモリゲート電極MGに高電圧が印加されるが、本発明では、メモリゲート電極MGに高電圧を印加するために、ブーストゲート電極BGを使用した容量カップリングを補助的に使用する。

(もっと読む)

半導体装置およびその製造方法

【課題】スプリットゲート型メモリセルを有する半導体装置の信頼性を向上させる。主要な目的の1つは、制御ゲート電極の表面に形成されているシリサイド層と、メモリゲート電極の表面に形成されているシリサイド層との接触による短絡不良を防止する技術を提供することにある。他の主要な目的は、メモリゲート電極と制御ゲート電極との間の絶縁耐性を保持する技術を提供することにある。

【解決手段】制御ゲート電極8の一方の側壁に形成された積層ゲート絶縁膜9とメモリゲート電極10との間には、酸化シリコン膜や窒化シリコン膜などからなる側壁絶縁膜11が形成されており、メモリゲート電極10は、この側壁絶縁膜11と積層ゲート絶縁膜9とによって制御ゲート電極8と電気的に分離されている。

(もっと読む)

メモリセルのアレイを作製する方法、メモリセルのアレイ及びメモリセルのアレイにおいてメモリセルを動作させる方法

【課題】安価なメモリデバイスを提供する。

【解決手段】1F2当り少なくとも1ビットを記憶するよう構成されたメモリセルのアレイは、アレイの最小ピッチの半分に等しい距離で離間した電子メモリ機能を与える実質的に縦型の構造を含む。電子メモリ機能を与える構造は、ゲート当り1ビットを超えて記憶するよう構成されている。また、アレイは、実質的に縦型の構造を含むメモリセルに対する電気接点も含む。セルは、第1のソース/ドレイン領域に隣接したゲート絶縁物にトラップされた多数の電荷レベルの1つを有するようプログラムすることができる。これにより、チャネル領域は第1のしきい値電圧領域と第2のしきい値電圧領域とを有し、プログラムされたセルが低減されたドレインソース電流で動作する。

(もっと読む)

半導体記憶装置、及びその製造方法

【課題】動作信頼性を向上させる半導体記憶装置、及びその製造方法を提供すること。

【解決手段】活性領域AA上に形成された第1絶縁膜16と、前記第1絶縁膜16上に複数配置された微小結晶体の電荷蓄積部17と、前記電荷蓄積部17を覆うように、前記第1絶縁膜16上に形成された第2絶縁膜18と、前記第2絶縁膜18上に形成された制御ゲート19とを具備し、前記第1絶縁膜16のゲート幅方向の端部における前記電荷蓄積部17の密度は、ゲート幅方向の中心部における密度よりも大きい。

(もっと読む)

電荷を非対称に捕獲する多値メモリセル

【課題】高メモリ密度、低電力消費、及び高信頼性を達成可能なNAND型多値メモリセルを提供する。

【解決手段】NAND型多値メモリセルは、2つのドレイン/ソース領域を基板に有する。2つのドレイン/ソース領域の間における基板の上方には、酸化物−窒化物−酸化物構造体が形成される。このうち窒化物層は、電荷を非対称に捕獲する層として機能する。酸化物−窒化物−酸化物構造体の上方には、制御ゲートが配置される。ドレイン/ソース領域に非対称のバイアスをかけることで、ドレイン/ソース領域に高い電圧が生じ、これによってドレイン/ソース領域の略近傍における電荷捕獲層にGIDL(ゲートに起因するドレインでの電流漏れ)正孔注入処理を行い、正孔を非対称な分布で注入する。

(もっと読む)

3次元半導体メモリ装置及びその製造方法

【課題】3次元半導体メモリ装置及びその製造方法を提供する。

【解決手段】本装置は、積層された導電パターン、導電パターンを貫通する活性パターン及び導電パターンと活性パターンとの間に介在される情報貯蔵膜を含む少なくとも1つのメモリ構造体を含み、活性パターンは積層された下部及び上部貫通ホールを各々満たす下部及び上部半導体パターンを含むことができる。1つのメモリ構造体を構成する情報貯蔵膜は同一の工程段階を利用して実質的に同時に形成され、1つのメモリ構造体を構成する下部及び上部貫通ホールは互いに異なる工程段階を利用して順に形成され得る。

(もっと読む)

Fin−FET型不揮発性メモリ・セル及びアレイ並びにその製造方法

不揮発性メモリ・セルが、基板層を有し、第1の導電型のフィン形状半導体部材が基板層上にある。フィン形状部材は、第2の導電型の第1の領域と、第1の領域から離間配置された第2の導電型の第2の領域とを有し、チャネル領域が第1の領域と第2の領域との間に延びている。フィン形状部材は、第1の領域と第2の領域との間に上面及び2つの側面を有する。ワード線が、第1の領域に隣接し、チャネル領域の第1の部分の上面及び2つの側面に容量結合される。浮遊ゲートが、ワード線に隣接し、上面から絶縁され、チャネル領域の第2の部分の2つの側面に容量結合される。 (もっと読む)

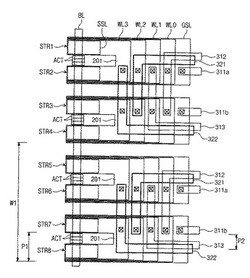

3次元メモリセルアレイを含む半導体メモリ素子及びその製造方法

【課題】高密度、且つ工程マージンの確保された3次元メモリセルアレイを含む半導体メモリ素子を提供する。

【解決手段】平坦な基板と、基板に対して垂直に形成され且つ各々複数の貯蔵セルを含む複数のメモリストリングからなるメモリストリングアレイと水平方向に互いに重畳した複数のワードラインを含み、ワードラインは各々基板に平行で且つメモリストリングに接続された第1部分及び第1部分から延伸され基板に対して上方に傾斜する第2部分を含み、メモリストリングアレイは複数のワードラインの各々の第1部分の中間部分に配置され、ワードラインの各々に接続されて各々対応する貯蔵セルを形成し、複数のワードラインの第1、第2グループは各々、メモリストリングアレイの第1、第2の側方に配置された第1、第2導電ラインのグループの各々と電気的に接続される。

(もっと読む)

半導体記憶素子の製造方法

【課題】金属ナノ結晶からなる離散的フローティングゲートを、移流集積法により形成する半導体記憶素子の製造方法を提供する。

【解決手段】製造方法は、シリコン基板1と、シリコン基板1上に形成されたトンネル絶縁膜に対向するように配置された第2の基板21との間に、金属ナノ粒子が分散された粒子分散液22を充填する充填工程と、トンネル絶縁膜の表面に沿った方向に、第2の基板21をシリコン基板1に対して相対的に移動させることにより、トンネル絶縁膜の表面における第2の基板21から露出した領域に形成される粒子分散液22のメニスカス領域23において、粒子分散液22の溶媒を蒸発させることにより、トンネル絶縁膜上に金属ナノ粒子を離散的に配置する。

(もっと読む)

半導体メモリー装置のチャンネルをプリチャージする方法

【課題】プログラムディスターバンスが効果的に遮断されて高いデータ信頼性を有する3次元半導体メモリー装置のチャンネルをプリチャージする方法を提供する。

【解決手段】本発明による半導体メモリー装置のプログラム方法は、複数のビットラインの中でプログラムビットラインに連結される少なくとも1つのインヒビットストリングのチャンネルと、インヒビットビットラインに連結されるインヒビットストリングの中で少なくとも何れか1つのチャンネルとを共通ソースラインに供給されるプリチャージ電圧に充電する段階と、ワードライン電圧を複数のセルストリングに供給してプリチャージされたチャンネルをブースティングさせる段階と、を有する。

(もっと読む)

ナノ構造ベースNANDフラッシュセルおよびその周辺回路の形成方法

ナノ構造に基づく電荷蓄積領域は、不揮発性メモリ装置に備えられており、選択ゲートおよび周辺回路の製造と一体に製造される。1つ以上のナノ構造コーティングは、メモリアレイ領域および周辺回路領域の基板に塗布される。選択ゲートや周辺トランジスタについての目標領域などの基板の不要な領域から、ナノ構造コーティングを除去するための様々な工程が、行われる。一例では、基盤のアクティブ領域にナノ構造を選択的に形成するために、自己組織化に基づく工程を用いて、1つ以上のナノ構造コーティングが形成される。自己組織化によって、ナノ構造コーティングのパターニングやエッチングを行うことなく、互いに電気的に分離されているナノ構造の個別のライン群を形成することができる。  (もっと読む)

(もっと読む)

不揮発性半導体集積回路装置

【課題】不揮発性半導体集積回路装置のチップサイズを縮小させる。

【解決手段】シリコン基板上に隣り合って配置された第1および第2ゲート電極とそれらの側方下部のシリコン基板に形成された一対のソース・ドレイン領域とを有し、第2ゲート電極とシリコン基板との間に配置された第2ゲート絶縁膜に電荷を蓄えることで情報を記憶するメモリセルにおいて、メモリセルの消去動作時には、消去非選択セルの第1ゲート電極に正電圧を印加する。

(もっと読む)

ナノ線メモリ

【課題】単純な構造のナノ点を有するメモリを利用してマルチレベルを保存することができるメモリ素子を提供する。

【解決手段】ソース210及びソース210と対応するドレイン220と、ソース210とドレイン220との間を連結するように形成されているナノチャンネル230とを含み、ナノチャンネル230は、ソース210及びドレイン220の電圧によってソース210とドレイン220との間を電気的に連結するナノ線と、ナノ線上に吸着されて形成され、電荷を補集する複数のポテンシャルを有するナノ点とを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】動作速度が速く、かつ書き換え可能な回数が多くい不揮発性メモリセルと、高い信頼性を有する不揮発性メモリセルとを有する半導体装置を提供する。

【解決手段】メモリゲート電極11a、11bがコントロールゲート電極5a、5bのサイドウォール形状に形成されたスプリットゲート型の不揮発性メモリにおいて、メモリゲート長La、Lbの異なるメモリセルを同一チップ内に混載することにより、動作速度が速く書き換え可能回数の多いメモリと信頼性のあるメモリとを有するメモリチップを安価に製造することができる。

(もっと読む)

不揮発性半導体記憶装置とその駆動方法および電子機器

【課題】周辺回路の増大を極力抑えつつ、データディスターブを改善する不揮発性半導体記憶装置を提供する。

【解決手段】第1ボディ領域100上に不純物拡散層104,124を、第1不純物拡散層104上に第2ボディ領域106を形成する。第1不純物拡散層104はメモリトランジスタMTのドレイン領域と選択トランジスタSTのソース領域、第1不純物拡散層124は選択トランジスタSTのドレイン領域をなす。第2ボディ領域106と第1不純物拡散層104に跨るように第2ボディ領域106上にメモリトランジスタMTのゲート部G_MTをMONOS構造で形成する。第1不純物拡散層104、第1ボディ領域100、第1不純物拡散層124に跨るように選択トランジスタSTのゲート部G_STをMOS型構造で形成する。両トランジスタMT,STは、バックゲートとなるボディ領域が電気的に分離される。

(もっと読む)

41 - 60 / 341

[ Back to top ]