Fターム[5F101BA54]の内容

不揮発性半導体メモリ (42,765) | 電荷蓄積機構 (9,664) | トラップ蓄積型 (3,039) | クラスタ (341)

Fターム[5F101BA54]に分類される特許

121 - 140 / 341

高κキャップ阻止誘電体‐バンドギャップ操作SONOS及びMONOS

【課題】阻止誘電体操作電荷トラップメモリーセルを提供する。

【解決手段】この阻止誘電体操作電荷トラップメモリーセルは、阻止誘電体によってゲートから分離された電荷トラップ要素を備える。該阻止誘電体は該電荷トラップ要素に接し高品質に作ることができる二酸化シリコン等のバッファ層(第1層)と、該ゲートに接するキャップ層(第2層)とを含む。該キャップ層は第1層より高い誘電率を有し、高κ材料でできているのが好ましい。第2層は相対的に高い伝導帯オフセットも有している。チャネルと該電荷トラップ要素の間にバンドギャップ操作トンネル層が設けられ、該多層阻止誘電体と組合わされて正孔トンネル現象による高速消去動作を可能にする。或いは、単一層からなるトンネル層が使用されてもよい。

(もっと読む)

半導体装置

【課題】書込/消去速度を劣化させることなく記憶保持時間を効率良く改善できるような、Si量子ドットを利用した半導体装置を提供することを目的とする。

【解決手段】電荷の蓄積が可能な電荷蓄積部と、チャネルを有する半導体と、前記電荷蓄積部と前記チャネルとの間に設けられ前記電荷蓄積部と前記チャネルとの間の電荷の移動を制御するゲートと、を備え、前記ゲートは、クーロンブロッケイド条件を満たす少なくとも1つの導電性粒子と、前記導電性粒子を挟む少なくとも二つのトンネル絶縁膜と、を有し、前記二つのトンネル絶縁膜の膜厚は、いずれも実効酸化膜厚に換算して0.5ナノメータ以上3.5ナノメータ以下であり、前記二つのトンネル絶縁膜のうちの前記チャネル側のトンネル絶縁膜の方が前記電荷蓄積部側のトンネル絶縁膜よりも実効トンネル膜厚が厚いものとされ、前記電荷蓄積部は、原子間結合の欠陥により形成された電荷捕捉準位であることを特徴とする半導体装置を提供する。

(もっと読む)

ナノドット形成方法、ナノドットを備えるメモリ素子の製造方法、ナノドットを備えるチャージトラップ層及びこれを備えるメモリ素子

【課題】ナノドット形成方法、ナノドットを備えるメモリ素子の製造方法、ナノドットを備えるチャージトラップ層及びこれを備えるメモリ素子を提供する。

【解決手段】コアを形成する第1ステップと、コア表面をポリマーでコーティングする第2ステップと、ポリマーコーティングされたコアを熱処理してコア表面を覆うグラフェン層を形成する第3ステップと、を含むナノドット形成方法。第3ステップ以後に前記コアを除去してもよい。かかるコア表面をポリマーでコーティングする前にコア表面を黒鉛化触媒物質でコーティングしてもよい。また、かかるコアは、電荷トラップ及び黒鉛化触媒機能を持つ金属粒子を含むか、電荷トラップ機能を持つ金属粒子を含みうる。

(もっと読む)

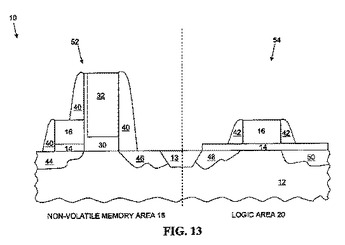

NVM回路をロジック回路と集積する方法

不揮発性メモリ(NVM)回路18を論理回路20とともに集積する方法が提供される。この方法は、基板12のNVM領域及びロジック領域の上に第1のゲート材料層16を堆積することを含む。この方法は更に、窒化膜、酸化膜及び窒化膜(ARC層)を有する複数の接し合う犠牲層22、24、26を互いに重ねて堆積することを含む。これら複数の接し合う犠牲層22、24、26は、NVM領域内のメモリトランジスタの選択ゲート16及び制御ゲート32をパターニングするために使用され、複数の接し合う犠牲層22、24、26のうちのARC層22はまた、ロジック領域20内のロジックトランジスタのゲート16をパターニングするために使用される。  (もっと読む)

(もっと読む)

不揮発性メモリ素子、その動作方法及びその製造方法

【課題】不揮発性メモリ素子、その動作方法及びその製造方法を提供する。

【解決手段】少なくとも一つの半導体層105と、半導体層105の内部にリセスされて配された複数の制御ゲート電極150と、複数の制御ゲート電極150と半導体層105との間に介在された複数の電荷保存層130と、複数の制御ゲート電極150を介して相互反対側に配され、半導体層105にそれぞれ容量結合された少なくとも一つの第1補助電極170a,及び少なくとも一つの第2補助電極170bと、を備える。

(もっと読む)

メモリセル、電子システム、メモリセルの形成方法、およびメモリセルのプログラミング方法

いくつかの実施形態は、誘電体材料によって互いにスペーシングされる、垂直に積層される電荷捕獲領域を有するメモリセルを含む。誘電体材料は、高k材料を含み得る。電荷捕獲領域のうちの1つ以上は、金属材料を含み得る。かかる金属材料は、ナノドット等の複数の個別の絶縁されたアイランドとして存在し得る。いくつかの実施形態は、メモリセルの形成方法を含み、トンネル誘電体上に2つの電荷捕獲領域が形成され、当該領域は互いに対して垂直に配置され、トンネル誘電体に最も近い領域は、もう1つの当該領域よりも深いトラップを有する。いくつかの実施形態は、メモリセルを含む電子システムを含む。いくつかの実施形態は、垂直に積層される電荷捕獲領域を有するメモリセルのプログラミング方法を含む。  (もっと読む)

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】絶縁膜の改質により電荷捕獲・放出特性を改善し、電界緩和、電荷書込み/消去/保持、電荷の過消去、それぞれに対応することのできる半導体記憶装置及びその製造方法を提供すること。

【解決手段】ソース・ドレイン拡散層と、前記ソース・ドレイン拡散層の間のチャネル領域上に順次形成された第1のゲート絶縁層、第1の電荷蓄積層、第2のゲート絶縁層、及び制御電極とを具備する、電気的に情報を書込み・消去・読み出し・保持することが可能なMONOS型不揮発性半導体記憶装置において、前記第1の電荷蓄積層は、主要元素としてAl及びOを含む絶縁膜を有し、該絶縁膜は、格子間O原子とAl原子を置換した4価カチオン原子との複合体からなる欠陥対、又は酸素欠損とO原子を置換したN原子との複合体からなる欠陥対を有することにより、Al2O3の価電子帯端から2eVないし6eVの範囲内に電子非占有準位を有することを特徴とするMONOS型不揮発性半導体記憶装置。

(もっと読む)

半導体素子及びこの半導体素子を用いた装置

【課題】高速な書込み及び消去動作を比較的低電圧で行い、かつ書換え劣化を抑えることで、メモリウインドウが大きく信頼性の高いメモリ素子を、低コストで提供する。

【解決手段】メモリ素子は、絶縁基板上に設けられた半導体層と、P型の導電型を有する第1の拡散層領域及び第2の拡散層領域と、第1の拡散層領域と第2の拡散層領域との間のチャネル領域を覆い、チャネル領域より電荷を注入され得る電荷蓄積膜と、電荷蓄積膜をはさんでチャネル領域とは反対側に位置するゲート電極とを有する。

(もっと読む)

不揮発性半導体メモリおよびその書き込み方法ならびにその消去方法

【課題】「書き込みおよび消去」の高速化と「電荷保持特性および読み出し特性」の向上とを両立させる。

【解決手段】シリコン基板10と、シリコン基板に離間して設けられたソース領域およびドレイン領域14a、14bと、ソース領域およびドレイン領域との間のシリコン基板上に設けられた第1障壁層21と、伝導帯内に量子化された少なくとも1つのエネルギー準位を含む第1エネルギー準位群が形成される第1量子井戸層22と、第2障壁層23と、伝導帯内に第1エネルギー準位群のエネルギー準位とそれぞれ異なる量子化された少なくとも1つのエネルギー準位を含む第2エネルギー準位群が形成され、第2エネルギー準位群のうちで、第1エネルギー準位群のうちのいずれかのエネルギー準位EC1よりも大きなエネルギー準位EC2が存在する第2量子井戸層24と第3障壁層25と、制御電極26とを有するメモリセル1を備え、第2量子井戸層は電子が蓄積可能。

(もっと読む)

不揮発性メモリのためのプログラム及び消去方法

【課題】本発明は、絶縁膜を電荷保存層として利用するフラッシュメモリ装置、そのプログラム及び消去方法、それを含むメモリシステム及びコンピュータシステムを提供する。

【解決手段】電荷保存層を有する不揮発性メモリ装置のプログラム又は消去方法であって、少なくとも一つの単位プログラム又は消去ループを行うステップを含み、各単位プログラム又は消去ループは、不揮発性メモリ装置の位置(例えば、ワードライン又は基板)に正又は負の電圧のような少なくとも一つのプログラムパルス、少なくとも一つの消去パルス、少なくとも一つの時間遅延、少なくとも一つのソフト消去パルス、少なくとも一つのソフトプログラムパルス及び/又は少なくとも一つの検証パルスを印加することを特徴とする。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】 STI起因の応力が印加されることによる結晶欠陥発生を抑制することができ、微細化及び信頼性の向上をはかる。

【解決手段】 基板101上に、不揮発性メモリセル部,周辺回路領域の低電圧動作回路部,及び周辺回路領域の高電圧動作回路部を有し、各部の素子間がSTIで分離された不揮発性半導体記憶装置であって、高電圧動作回路部のSTI埋め込み絶縁膜の上面は基板表面より上方に位置し、低電圧動作回路部のSTI埋め込み絶縁膜の少なくとも一部の上面は基板表面より下まで後退した形状になっている。

(もっと読む)

アルミニウム酸化物層の形成方法及びそれを利用した電荷トラップ型メモリ素子の製造方法

【課題】アルミニウム酸化物層の形成方法及びそれを利用した電荷トラップ型メモリ素子の製造方法を提供する。

【解決手段】下部膜上に非晶質アルミニウム酸化物層を形成する第1ステップと、非晶質アルミニウム酸化物層上に結晶質補助層を形成する第2ステップと、非晶質アルミニウム酸化物層を結晶化する第3ステップと、を含むことを特徴とするアルファアルミニウム酸化物層の形成方法及びそれを利用したメモリ素子の製造方法である。前記第2ステップは、非晶質アルミニウム酸化物層上に非晶質補助層を形成するステップと、非晶質補助層を結晶化するステップと、を含む。

(もっと読む)

不揮発性半導体記憶装置

【課題】チャネル領域の側面に、補助電極として側面電極を設けることにより、動作マージンを向上させるNAND型不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板100と、この半導体基板100に設けられ、直列に接続される複数のメモリセルトランジスタを有するメモリセルアレイをそなえている。そして、メモリセルトランジスタは、半導体基板100に形成されるソース領域およびドレイン領域と、チャネル領域211と、トンネル絶縁膜102と、電荷蓄積層104と、制御絶縁膜106と、制御電極108と、チャネル領域211の側面に設けられる側面絶縁膜110と、チャネル領域211を挟んで対向する2つの側面電極112を備えている。そして、側面電極112は、直列に接続される前記メモリセルトランジスタ間で共通化されていることを特徴とする。

(もっと読む)

逆転構造の不揮発性メモリ素子、そのスタックモジュール及びその製造方法

【課題】逆転構造の不揮発性メモリ素子、そのスタックモジュール及びその製造方法を提供する。

【解決手段】少なくとも一つの底ゲート電極は、基板上に提供され、少なくとも一層の電荷保存層は、少なくとも一つの底ゲート電極上に提供され、少なくとも一層の半導体チャンネル層は、少なくとも一層の電荷保存層上に提供される不揮発性メモリ素子である。少なくとも一層の半導体チャンネル層の両側に電気的にそれぞれ連結された少なくとも一つのソース電極及び少なくとも一つのドレイン電極をさらに備える。

(もっと読む)

不揮発性メモリ素子のプログラム方法

【課題】不揮発性メモリ素子のプログラム方法を提供する。

【解決手段】(イ)メモリセルにプログラム電圧を印加し、次いで、第1検証電圧で検証する第1プログラミングステップと、(ロ)第1検証電圧を利用した検証を通過したメモリセルに電荷の安定化を促進するための摂動パルスを印加するステップと、

(ハ)摂動パルスの印加後に第1検証電圧より高い第2検証電圧で検証するステップと、を含むことを特徴とする不揮発性メモリ素子のプログラム方法である。

(もっと読む)

結晶質アルミニウム酸化物層のエネルギーバンドギャップを高める方法及びエネルギーバンドギャップの高い結晶質アルミニウム酸化物層を備える電荷トラップメモリ素子の製造方法

【課題】結晶質アルミニウム酸化物層のエネルギーバンドギャップを高める方法及びエネルギーバンドギャップの高い結晶質アルミニウム酸化物層を備える電荷トラップメモリ素子の製造方法を提供する。

【解決手段】下部膜上に非晶質アルミニウム酸化物層を形成する第1ステップと、非晶質アルミニウム酸化物層内に水素(H)または水酸基(OH)を導入する第2ステップと、水素または水酸基が導入された非晶質アルミニウム酸化物層を結晶化させる第3ステップと、を含むことを特徴とするアルミニウム酸化物層のエネルギーバンドギャップを高める方法である。これにより、結晶化されたアルミニウム酸化物層のエネルギーバンドギャップは、7.0eVより大きい。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】スプリットゲート型MONOSメモリセルにおいて、SSI方式による書込み時のディスターブ耐性を向上させることのできる技術を提供する。

【解決手段】選択用nMISQncと、選択用nMISQncの側面に絶縁膜6b、6tおよび電荷蓄積層CSLを介して形成されたメモリ用nMISQnmとを含むメモリセルMC1において、選択ゲート電極CGのゲート長方向端部下のゲート絶縁膜4の厚さが、ゲート長方向中央部下のゲート絶縁膜4の厚さよりも厚く形成され、選択ゲート電極CGと電荷蓄積層CSLとの間に位置し、かつ半導体基板1に最も近い下層の絶縁膜6bの厚さが、半導体基板1と電荷蓄積層CSLとの間に位置する下層の絶縁膜6bの厚さの1.5倍以下に形成される。

(もっと読む)

抵抗素子を有する半導体装置及びその形成方法

【課題】本発明は、製造工程の間に相対的に安定に維持され、予測可能な抵抗値を有する抵抗素子を含む半導体装置とその形成方法を提供する。

【解決手段】この半導体装置は、第1領域と第2領域を備える基板と、第1領域の基板上の、第1ゲート絶縁膜及び該第1ゲート絶縁膜上の第1ゲート電極膜を備えた少なくとも一つの第1ゲート構造物と、を備える。

(もっと読む)

高速消去式電荷捕捉メモリーセル

【課題】 7Vほどものメモリーウィンドウを有する高速なプログラムと消去の速度を達成する。

【解決手段】 バンドギャップを構造設計した電荷捕捉メモリーセルは、プラチナゲートのような金属又は金属化合物のゲートから、酸化アルミニウムのような高い誘電定数を有する材料のブロッキング層によって隔離され、チャンネルを含む半導体本体から改良されたトンネリング誘電体によって隔離される電荷捕捉素子を有する。

(もっと読む)

不揮発性メモリ素子及びその製造方法

【課題】不揮発性メモリ素子及びその製造方法を提供する。

【解決手段】トンネリング膜、電荷保存層、ブロッキング絶縁膜及びゲート電極を備える電荷トラップメモリ素子において、ブロッキング絶縁膜は、ガンマ相のアルミニウム酸化膜よりエネルギーバンドギャップが大きいアルミニウム酸化膜であることを特徴とする不揮発性メモリ素子である。ブロッキング絶縁膜として結晶質アルミニウム酸化膜は、エネルギーバンドギャップが7.0eV以上であり、欠陥が少ない。結晶質アルミニウム酸化膜は、非晶質アルミニウム酸化膜の上部または内部にAlF3膜を導入するか、またはAlF3を非晶質アルミニウム酸化膜の拡散またはイオンインプランテーション後に熱処理してなされる。したがって、メモリ素子の電荷保有能が高まり、プログラム及び消去に必要な動作電圧が低くなり、その動作速度も速くなりうる。

(もっと読む)

121 - 140 / 341

[ Back to top ]