Fターム[5F101BG07]の内容

不揮発性半導体メモリ (42,765) | 応用 (153) | 回路切り替え冗長回路等 (46)

Fターム[5F101BG07]に分類される特許

1 - 20 / 46

半導体装置

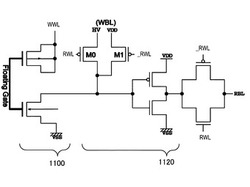

【課題】外部からの回路構成情報の呼び出し処理を不要にして、電源投入後すぐに動作できる半導体装置を提供する。

【解決手段】半導体装置は、ワード線とデータ線とが交差する位置にそれぞれ配置された複数の不揮発メモリセル1100を有する。不揮発メモリセル1100の出力にはインバータ回路が接続され、さらに不揮発メモリセルの出力とWBL(Write Bit Line)との間に第1トランジスタM1と、第1トランジスタよりも抵抗が低い第2トランジスタM2とを備える。インバータ回路の出力とRBL(Read Bit Line)との間にはトランスファーゲートを備える。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】新たな構造の半導体装置を提供し、書き込み後の当該半導体装置のメモリセルのしきい値電圧のばらつきを小さくし、動作電圧を低減する、または記憶容量を増大する。

【解決手段】酸化物半導体を用いたトランジスタと、酸化物半導体以外の材料を用いたトランジスタとをそれぞれ有する複数のメモリセルと、複数のメモリセルを駆動する駆動回路と、駆動回路に供給する複数の電位を生成する電位生成回路と、を有し、駆動回路は、

データバッファと、複数のメモリセルのそれぞれに複数の電位のうちいずれか一の電位をデータとして書き込む書き込み回路と、メモリセルに書き込まれたデータを読み出す読み出し回路と、読み出されたデータと、データバッファに保持されたデータとが一致するか否かをベリファイするベリファイ回路と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置の製造後におけるチャージ蓄積用素子からのチャージの放電を防止してデバイス機能素子のチャージダメージを低減する半導体装置及びその製造方法を提供する。

【解決手段】 半導体基板上に形成されたデバイス機能素子と、半導体基板上に形成されたチャージ蓄積用素子と、半導体基板上に形成され、デバイス機能素子とチャージ蓄積用素子との間に接続され、電気的に書き換え可能な不揮発性メモリトランジスタにより形成された分離用素子とを有する。

(もっと読む)

半導体装置、及び半導体装置の制御方法。

【課題】簡便な半導体装置の評価試験を実現する。

【解決手段】半導体装置10は、それぞれ内部信号MAを生成する第1及び第2のコアチップCC0,CC1を備え、第1及び第2のコアチップCC0,CC1のそれぞれに、貫通電極を介して他方のコアチップとスパイラル接続された第2及び第3のノードN2,N3を設け、この第2及び第3のノードN2,N3を介して、観測対象の内部信号MAを外部に出力することを技術思想とするものである。こうして出力される複数の内部信号MAを外部のテスター等によって観測することで、各コアチップの評価試験を並列に行える。

(もっと読む)

欠陥フラッシュメモリダイの動作不能化

【課題】複数のフラッシュメモリダイを含むデバイス内の欠陥フラッシュメモリダイを動作不能化する製品ならびに関連する方法およびシステムを提供する。

【解決手段】動作不能化されていないフラッシュメモリダイに基づくフラッシュメモリのデータ記憶容量を示すラベルを、複数のフラッシュメモリダイを含むパッケージに付すことができる。ダイレベル、パッケージレベル、および/またはボードレベルにおいて、様々な動作不能化方法を適用することができる。

(もっと読む)

半導体装置

【課題】制御チップと複数の被制御チップが積層されたタイプの半導体装置において、コマンド信号よりも層アドレス信号を早く伝送させる。

【解決手段】互いに異なる層情報を保持する複数の被制御チップCC0〜CC7と、被制御チップCC0〜CC7に対して層アドレス信号A13〜A15及びコマンド信号ICMDを共通に供給する制御チップIFとを備える。層アドレス信号A13〜A15を構成する各ビットは、複数の第1の貫通電極のうち、被制御チップごとに並列接続された少なくとも2本の貫通電極を経由して伝送され、コマンド信号ICMDを構成する各ビットは、出力切り替え回路及び入力切り替え回路によって選択された対応する1本の貫通電極を経由して伝送される。これにより、コマンド信号ICMDよりも先に層アドレス信号A13〜A15が各被制御チップに到達する。

(もっと読む)

半導体記憶システム

【課題】 複数のチップを実装した場合において、複数のチップ間で通信する通信線を設けることなく、ピーク電流を抑制可能な半導体記憶システムを提供する。

【解決手段】 半導体記憶システムによれば、電源配線81は、第1の半導体記憶装置71aと第2の半導体記憶装置71bに共通接続され、第1、第2の半導体記憶装置に電源を供給する。電圧検知回路74a,74b,74cは、第1、第2の半導体記憶装置のそれぞれに設けられ、電源配線の電源電圧を検知する。制御回路7は、第1、第2の半導体記憶装置のそれぞれに設けられ、電圧検知回路により電源電圧の低下が検知された場合、電源電圧が復帰するまで、第1、又は第2の半導体記憶装置の動作を、次の動作に遷移させない。

(もっと読む)

不揮発性メモリー装置の製造方法

【課題】不揮発性メモリー装置の製造方法であって、特に半導体パターン厚さの均一性が向上される3次元半導体装置の製造方法、及び当該製造方法によって製造された3次元半導体装置を提供する。

【解決手段】この製造方法は、基板10の上に複数の第1の膜(鋳型膜)120及び複数の第2の膜(犠牲膜)が交互に積層された積層膜構造体を形成する段階、積層膜構造体を貫通する開口部、及び開口部周囲にアンダーカット領域を形成する段階、アンダーカット領域に局所的に配置される絶縁スペーサー155を形成する段階、絶縁スペーサー155が形成された開口部内に半導体パターン165を形成する段階を含む。

(もっと読む)

半導体記憶装置

【課題】消去回数の増加を抑制し、書き込み速度の向上及びメモリセルの劣化を防止することが可能な半導体記憶装置を提供すること。

【解決手段】読み出しレベルに応じてデータを保持可能なセルMCが形成されたセルアレイ1と、前記セルMCに書き込まれた回数N(N:0以上の整数)をカウントし、その回数に応じて書込電圧Vpgm及び読出電圧Vcgrを前記セルに転送する制御部9と、前記書込電圧を用いてデータを書み込み、前記読出電圧を発生し、データを読み出す電圧発生回路とを具備し、書込要求があると、前記読出電圧を発生させ、前記データを読み出し、読み出された閾値電圧より高い閾値電圧に遷移させる前記書き込み電圧を前記電圧発生回路に発生させ、前記セルへの前記回数N回目(≧2)の書き込み要求が規定値に達していると、前記制御部は前記セルが保持する前記データを消去させる。

(もっと読む)

半導体メモリ装置の駆動方法

【課題】オフ状態のソース、ドレイン間のリーク電流の低いトランジスタを書き込みトランジスタに用いて、データを長期間にわたり保存する半導体メモリ装置の駆動方法を提供する。

【解決手段】書き込みトランジスタのドレインと素子トランジスタのゲート、および、容量素子の一方の電極を接続したメモリセルを複数用いて形成されたマトリクスにおいて、書き込みトランジスタのゲートを書き込みワード線に接続し、キャパシタの他方の電極を読み出しワード線に接続する。そして、容量素子に蓄えられた電荷量を、読み出しワード線の電位を変化させることにより確認し、基準以上に電荷量が減少している場合にはメモリセルのリフレッシュをおこなう。

(もっと読む)

垂直的に集積された不揮発性記憶セルサブストリングを含む不揮発性記憶装置の形成方法、及び形成された不揮発性記憶装置

【課題】 セルの電気的特性の均一性を向上させ得る3次元不揮発性記憶装置及びその形成方法を提供する。

【解決手段】 本発明の不揮発性記憶装置の形成方法は不揮発性記憶セルが高集積化された垂直的積層を形成するための段階を含む。不揮発性記憶セルでは、直列に電気的に連結される複数の垂直サブストリングを使用して記憶セルが半導体基板上に垂直に積層される。このとき、記憶セルの垂直方向の積層は劣等に作用するメモリセルストリングが発生しないように、製造工程において補正するためにダミー記憶セルを利用する。

(もっと読む)

3次元半導体装置

【課題】3次元的に配列される導電パターンの厚さを増加しその抵抗を減少できる3次元半導体装置を提供する。

【解決手段】この装置は基板上に順に積層された水平構造体と、水平構造体を垂直に横切る垂直構造体とを具備する。水平構造体の各々は基板に平行な導電ライン及び垂直構造体に隣接した導電ラインの一側壁を覆う第2パターンを含む。また垂直構造体の各々は半導体柱及び水平構造体に隣接した半導体柱の少なくとも一側壁を覆う第1パターンを含む。

基板上に順に積層された電極を含む電極構造体と、電極構造体を垂直に貫通する半導体パターンと、第1パターン及び第2パターンを具備して半導体パターンと電極構造体との間に介在するメモリー要素と、を含み、第1パターンは垂直に延長されて複数の電極を横切り、第2パターンは水平に延長されて複数の半導体パターンを横切る。

(もっと読む)

半導体記憶装置

【課題】不良要素の効率良い置き換えを可能にする構成を有する半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数の単位構造を有する。単位構造は、複数のメモリセルと接続された複数のビット線と、複数のビット線のうちの隣接する複数のビット線とそれぞれ接続された複数のセンスアンプと、複数のセンスアンプと共通に接続された第1データ線SBUSと、第1データ線と接続された演算回路Yと、演算回路と接続された第2データ線DBUSと、第2データ線と接続された複数のデータラッチXDLを含む。複数の単位構造は、相互に独立しており、またその一部はスペア用単位構造である。複数の単位構造の1つは、スペア用単位構造と置き換えられる。

(もっと読む)

半導体装置

【課題】高周波動作向けの半導体装置を高性能化させる。

【解決手段】シリコン基板S1上に形成された抵抗素子TDR1および不揮発性メモリNVM1を有する半導体装置であって、不揮発性メモリNVM1は、シリコン基板S1上に埋め込み酸化層BOX1を介して配置されたシリコン層SOI1に形成されている。特に、抵抗素子TDR1と不揮発性メモリNVM1とは互いに電気的に接続され、不揮発性メモリNVM1のオン状態またはオフ状態により、抵抗素子TDR1の導通状態または非導通状態が切り替わる。

(もっと読む)

半導体装置およびその製造方法

【課題】データ保持特性の良好な不揮発性メモリおよびその製造技術を提供する。

【解決手段】ゲート絶縁膜6上に多結晶シリコン膜7および絶縁膜8を順次堆積し、これら多結晶シリコン膜7および絶縁膜8をパターニングしてゲート電極7A、7Bを形成した後、ゲート電極7A、7Bの側壁に酸化シリコン膜からなるサイドウォールスペーサ12を形成する。その後、基板1上にプラズマCVD法で窒化シリコン膜19を堆積することにより、ゲート電極7A、7Bと窒化シリコン膜19とが直接接しないようにする。

(もっと読む)

不揮発性半導体記憶装置

【課題】チップ面積の増大を抑制しつつ、不良ブロックの非選択処理が可能な不揮発性半導体記憶装置を提供する。

【解決手段】メモリマット10〜60を含むメモリアレイをコの字型に配置し、メモリアレイが配置されていない空き領域にロジック回路92およびアナログ回路91を配置している。これにより、アナログ回路91およびロジック回路92などの周辺回路と電源パッド101およびデータパッド100などのパッド帯との間で電源電圧および信号のやりとりが容易となる。また、アナログ回路91については電源パッド101に近くなるため、電源配線抵抗による電圧降下を抑制でき、かつ電源パッド101付近でチャージポンプ用電源配線102と周辺回路用電源配線103とを分離することが可能となる。

(もっと読む)

NAND型フラッシュメモリ

【課題】メモリセルのしきい値電圧の分布幅の拡大を抑制することが可能なNAND型フラッシュメモリを提供する。

【解決手段】NAND型フラッシュメモリは、第1の絶縁膜、電荷保持層、第2の絶縁膜、および、制御ゲートを含み、電荷保持層に保持された電荷量に応じた情報を記憶するメモリセルが直列に複数接続されたNANDストリングと、制御ゲートおよび半導体ウェルに印加する電圧を制御する制御回路とを備え、書き込み動作後、選択メモリセルにデータが書き込まれたか否かを検証するベリファイリード動作を行う前に、制御回路は、選択メモリセルの制御ゲートに、半導体ウェルの電位と同電位または書き込み電圧と同極性である第1の電圧を印加し、書き込み対象ではない非選択メモリセルの制御ゲートには、書き込み電圧と同極性であり第1の電圧よりも絶対値として大きい第2の電圧を印加するデトラップ動作を行う。

(もっと読む)

不揮発性記憶装置、集積回路装置及び電子機器

【課題】付加情報を記憶することができる不揮発性記憶装置、集積回路装置及び電子機器を提供すること。

【解決手段】不揮発性記憶装置は、電気的に書き換え可能な不揮発性の複数のメモリーセル及び複数のビット線を含む主記憶回路10と、電気的に書き換え可能な不揮発性の複数の情報メモリーセル及び複数のビット線を含む情報記憶回路20と、主記憶回路10の対応ビット線と情報記憶回路20の対応ビット線との電気的接続をオン状態又はオフ状態にするための選択トランジスターを含む選択回路とを含み、情報記憶回路20は、主記憶回路10の不良アドレス情報を記憶する第1の情報メモリーセルと、管理情報及び不揮発性記憶装置の外部の回路のための調整情報のうちの少なくとも一方の情報である付加情報を記憶する第2の情報メモリーセルとを含む。

(もっと読む)

不揮発性記憶装置、集積回路装置及び電子機器

【課題】加工精度の向上等が可能な不揮発性記憶装置、集積回路装置及び電子機器を提供すること。

【解決手段】不揮発性記憶装置は、電気的に書き換え可能な不揮発性の複数のメモリーセル及び複数のビット線が配置される主記憶回路10と、電気的に書き換え可能な不揮発性の複数の情報メモリーセル及び複数のビット線が配置され、少なくとも主記憶回路10の不良メモリーセルのアドレス情報を記憶する情報記憶回路20と、主記憶回路10の複数のビット線のうちの対応ビット線と情報記憶回路20の複数のビット線のうちの対応ビット線との電気的接続をオン状態又はオフ状態にするための選択トランジスターが配置される選択回路30とを含み、情報記憶回路20は主記憶回路10と選択回路30との間に配置される。

(もっと読む)

EEPROM

【課題】2つのメモリトランジスタに同一のデータを確実に書き込むことができる、W(ダブル)セル方式のEEPROMを提供する。

【解決手段】半導体層には、第1不純物領域8、第2不純物領域9、第3不純物領域10、第4不純物領域11、第5不純物領域12および第6不純物領域13が形成されている。セレクトゲート15は、第1不純物領域8と第2不純物領域9との間の領域に、第1絶縁膜14を挟んで対向している。第1フローティングゲート16は、第2不純物領域9と第3不純物領域10との間の領域および第5不純物領域12に、第1絶縁膜14を挟んで対向している。第2フローティングゲート20は、第3不純物領域10と第4不純物領域11との間の領域および第6不純物領域13に、第1絶縁膜14を挟んで対向している。第5不純物領域12および第6不純物領域13は、第2不純物領域9と接続されている。

(もっと読む)

1 - 20 / 46

[ Back to top ]