Fターム[5F101BG10]の内容

不揮発性半導体メモリ (42,765) | 応用 (153) | その他 (59)

Fターム[5F101BG10]に分類される特許

1 - 20 / 59

不揮発性プログラマブルスイッチ

【課題】セル面積の小さい不揮発性プログラマブルスイッチを提供する。

【解決手段】第1配線に接続される第1端子と第2配線に接続される第2端子と第3配線に接続される第3端子とを有する第1不揮発性メモリトランジスタと、第4配線に接続される第4端子と第2配線に接続される第5端子と第3配線に接続される第6端子とを有する第2不揮発性メモリトランジスタと、第2配線にゲート電極が接続されたパストランジスタと、を備え、第1および第4配線が第1電源に接続され、第3配線が第1電源の電圧よりも高い電圧に接続されるときに第1不揮発性メモリトランジスタの閾値電圧が増加し、第2不揮発性メモリトランジスタの閾値電圧が低下し、第1および第4配線が第1電源に接続され、第3配線が第1電源の電圧よりも低い電圧に接続されるときに第1不揮発性メモリトランジスタの閾値電圧が低下し、第2不揮発性メモリトランジスタの閾値電圧が増加する。

(もっと読む)

半導体装置

【課題】作製工程が簡略化され、容量素子の面積が縮小化された昇圧回路を有する半導体

装置を提供することを課題とする。

【解決手段】直列に接続され、第1の入力端子部から出力端子部へ整流作用を示す複数の

整流素子と、第2の入力端子部に接続され、互いに反転する信号が入力される第1の配線

及び第2の配線と、それぞれ第1の電極、絶縁膜及び第2の電極を有し、昇圧された電位

を保持する複数の容量素子とから構成される昇圧回路を有し、複数の容量素子は、第1の

電極及び第2の電極が導電膜で設けられた容量素子と、少なくとも第2の電極が半導体膜

で設けられた容量素子とを有し、複数の容量素子において少なくとも1段目の容量素子を

第1の電極及び第2の電極が導電膜で設けられた容量素子とする。

(もっと読む)

二重フローティングゲート構造を有するトランジスタを備えた不揮発性メモリ

【課題】CMOS製造プロセスに用いることのできる材料を用いかつノイズマージンの広い不揮発性メモリを提供する。

【解決手段】本実施形態の不揮発性メモリによれば、第1および第2のPチャネルトランジスタはそれぞれ第1の半導体領域上に設けられ、第1の半導体領域上に、第1の絶縁膜と、第1のフローティングゲート、第2の絶縁膜、第2のフローティングゲート、第3の絶縁膜、および第1の制御ゲートが、この順序で積層された構造を有し、前記第1および第2のNチャネルトランジスタはそれぞれ第2の半導体領域上に設けられ、前記第2の半導体領域上に、第4の絶縁膜、第3のフローティングゲート、第5の絶縁膜、第4のフローティングゲート、第6の絶縁膜、および第2の制御ゲートがこの順序で積層された積層構造を有している。

(もっと読む)

アプリケーション回路及び半導体デバイスの動作方法

【課題】バッテリレス電子タイマに適用される半導体デバイス、及びその動作方法とアプリケーション回路を提供する。

【解決手段】半導体デバイス600は、第1導電型半導体基板と、ゲート誘電層と、フローティングゲート606と、第2導電型ウェル608と、第1導電型ウェル610と、第2導電型ソース拡散層612と、第2導電型ドレイン拡散層614と、第2導電型制御ゲート拡散層616と、を含む。制御ゲート拡散層616、ソース拡散層612及びドレイン614の間の漏れ電流が二重のウェル領域上に印加されるバイアスを調節することにより減少される。

(もっと読む)

ICカード表示システム

【課題】カード所有者がカード内に蓄積された情報を知りたい場合等に、外部のカード読取装置を用いてカード内に蓄積された情報を解読し、カード読取装置に搭載されているディスプレイ上に前記の蓄積情報を読み出さなければならないという不便さがあった。

【解決手段】ICカード本体と、ICカード本体における外部からの機械的な変形を電力に変換するセルフ電源装置と、ICカード本体の外側へ露出して表示を行うディスプレイ面を有し、セルフ電源装置で発生した電力の供給を受けてディスプレイ面に情報を表示する表示装置とを備えるICカード表示システムが提供される。

(もっと読む)

積層半導体メモリ装置、これを含むメモリシステム及び貫通電極の欠陥リペア方法

【課題】貫通電極の製造歩留まりを高めることができる積層半導体メモリ装置及びこれを含むメモリシステムを提供すること。

【解決手段】積層半導体メモリ装置は、プロセッサチップの上部に積層された複数のメモリチップ、複数の貫通電極(TSV)及び入出力バッファを含む。貫通電極の各々は前記メモリチップをすべて貫通し、前記プロセッサチップに接続される。入出力バッファは、前記メモリチップの全部又は一部と前記貫通電極の各々との間に結合され、前記貫通電極の状態に基づいて選択的に活性化する。

(もっと読む)

半導体装置及びそれを用いた論理回路

【課題】面積を縮小させることが出来、また歩留まりを向上させる半導体装置及びそれを用いた論理回路を提供すること。

【解決手段】第1トランジスタTr1と第2トランジスタTr2とが形成され、前記第1トランジスタTr1はソース及びドレインとして機能する第1拡散層群103と、第1ゲート電極102と、第2ゲート電極104とを備え、前記第2トランジスタTr2はソース及びドレインとして機能する第2拡散層群201と、電荷を蓄積可能な浮遊ゲート202と、第3ゲート電極200とを備え第2ゲート電極200は、前記第1トランジスタTr1の閾値Vthを制御可能とし、この第2ゲート電極104の電位は、前記浮遊ゲート202が蓄積する電荷量に応じた値である。

(もっと読む)

半導体装置と、それを用いた可変インピーダンス回路および共振回路

【課題】電源電圧が遮断されている場合でも記憶データに基づいてスイッチ回路を導通状態または非導通状態にすることが可能な半導体装置を提供する。

【解決手段】この半導体集積回路装置では、浮遊ゲートおよび制御ゲートを有するメモリトランジスタMAと、ゲートが浮遊ゲートに接続され、メモリトランジスタMAの記憶データに応じてオンまたはオフするNチャネルMOSトランジスタQAとを含む。したがって、電源電圧VCCが遮断されている場合でも、メモリトランジスタMAの記憶データに基づいてトランジスタQAをオンまたはオフさせることができる。

(もっと読む)

不揮発性半導体記憶装置とその駆動方法および電子機器

【課題】周辺回路の増大を極力抑えつつ、データディスターブを改善する不揮発性半導体記憶装置を提供する。

【解決手段】第1ボディ領域100上に不純物拡散層104,124を、第1不純物拡散層104上に第2ボディ領域106を形成する。第1不純物拡散層104はメモリトランジスタMTのドレイン領域と選択トランジスタSTのソース領域、第1不純物拡散層124は選択トランジスタSTのドレイン領域をなす。第2ボディ領域106と第1不純物拡散層104に跨るように第2ボディ領域106上にメモリトランジスタMTのゲート部G_MTをMONOS構造で形成する。第1不純物拡散層104、第1ボディ領域100、第1不純物拡散層124に跨るように選択トランジスタSTのゲート部G_STをMOS型構造で形成する。両トランジスタMT,STは、バックゲートとなるボディ領域が電気的に分離される。

(もっと読む)

半導体装置の製造方法

【課題】不揮発性メモリを備える半導体装置において、不揮発性メモリを構成するメモリセルの加工精度を向上することができる技術を提供する。

【解決手段】ポリシリコン膜PF1とダミーゲート電極DMY1を覆うようにポリシリコン膜PF2を形成する。このとき、ポリシリコン膜PF2は、段差DIFおよびギャップ溝GAPの形状を反映して形成される。特に、ギャップ溝GAPを覆うポリシリコン膜PF2には凹部CONが形成される。続いて、ポリシリコン膜PF2上に反射防止膜BARCを形成する。このとき、流動性の高い反射防止膜BARCは、段差DIFの高い領域から低い領域に流出するが、凹部CONに充分な反射防止膜BARCが蓄積されているので、流出する反射防止膜BARCを補充するように凹部CONから反射防止膜BARCが供給される。

(もっと読む)

薄膜トランジスタを利用して不揮発性メモリとする方法およびその装置

【課題】薄膜トランジスタ(TFT)のベースを利用して電荷を保存し、不揮発性メモリとする方法を提供する。

【解決手段】薄膜トランジスタ10を利用し、そのうち薄膜トランジスタ10は中間がベース21、両端がそれぞれドレイン電極22、ソース電極23である半導体層20を備え、絶縁表面31を備えた基板30上に設置され、ゲート電極絶縁層41が前記半導体層20上に設置され、ゲート電極40がゲート電極絶縁層41上に設置され、電子がゲート電極40の電場作用下で、熱電子界放射により電子正孔対を形成し、電子正孔対がゲート電極40の垂直電場により分離され、複数のキャリア(nチャネルでいうと正孔)が薄膜トランジスタ10のベース21に注入され、薄膜トランジスタ10の閾値電圧の変化を引き起こし、書き込み動作が完了する。

(もっと読む)

絶縁ゲート型半導体装置の製造方法

【課題】非ヒステリシストランジスタとヒステリシストランジスタとを混載する場合において、欠陥や不純物混入リスクの少ない良好な基板界面を保ったまま、同一材料の絶縁膜を用いて、ヒステリシストランジスタと非ヒステリシストランジスタとを同一基板上に混載することができる絶縁ゲート型半導体装置の製造方法を提供する。

【解決手段】第1及び第2のトランジスタ形成領域上に第1のトランジスタにヒステリシス特性を与える絶縁膜1を形成し、これを第1のトランジスタのゲート絶縁1膜とする工程、及び、第2のトランジスタ形成領域上の絶縁膜1を部分的にエッチング除去することにより、第2のトランジスタにヒステリシス特性を与えない絶縁膜とし、これを第2のトランジスタのゲート絶縁膜とする工程を含む。

(もっと読む)

不揮発性半導体記憶装置

【課題】第1ゲート電極と第2ゲート電極間の寄生容量の少なく高速アクセスが可能なソースサイド注入方式のスプリットゲート型不揮発性メモリセルを備えた不揮発性半導体記憶装置を提供する。

【解決手段】メモリセルが、書き込み・消去用の第1メモリセルユニットU1と、読み出し用の第2メモリセルユニットU2と、第3メモリセルユニットU3とを備えてなり、第1メモリセルユニットU1の第2ゲート電極7、第2メモリセルユニットU2の第3ゲート電極11、第3メモリセルユニットU3の第4ゲート電極13同士が電気的に接続してフローティングゲートFGが形成される。第4ゲート電極13上に第2の絶縁膜を介して第5ゲート電極15が形成され、第5ゲート電極15が制御端子CGと電気的に接続することにより、フローティングゲート7,11,13が制御端子CGと容量結合している。

(もっと読む)

半導体集積回路装置及びその製造方法

【課題】不揮発性記憶素子と、容量素子若しくは抵抗素子とを有するシステムICの製造方法を提供する。

【解決手段】半導体基板の主面の素子分離領域5上に下部電極10cが設けられ、かつ下部電極10c上にONO膜11,12,13からなる誘電体膜を介在して上部電極19cが設けられた容量素子Cを有する半導体集積回路装置であって、半導体基板の主面の素子分離領域5と下部電極10cとの間に耐酸化性膜8、及び下部電極10cと上部電極19cとの間に耐酸化性膜12を有する。

(もっと読む)

再構成可能な半導体デバイス

【課題】 再構成可能な半導体デバイスを提供する。

【解決手段】 再構成可能な半導体デバイスが開示されている。半導体デバイスは、基板と、基板上に形成された第1の絶縁材料と、異なる極性を有する2つのチャネルと、絶縁材料上に形成され、かつ対向する端部で、これらのチャネルに、共通に結合された複数のターミナル電極と、ターミナル電極に形成された第2の絶縁材料と、第2の絶縁材料上に形成された少なくとも1つのコントロールゲートとを含む。チャネルは、異なる極性を有し、電荷蓄積層は、第2の絶縁材料内側に形成されている。コントロールゲートに、フォワードバイアスまたはリバースバイアスが印加され、次にバイアスが切断される。半導体デバイスの電圧−電流特性は、電荷蓄積層に生成された電荷に従って変化する。

(もっと読む)

不揮発性半導体メモリ素子、および不揮発性半導体メモリ装置

【課題】標準ロジックのCMOSプロセスで不揮発性メモリを実現し、キャパシタをコンパクトに配置して面積を最小限にする、不揮発性半導体メモリ素子を提供する。

【解決手段】第1トランジスタT1および第2トランジスタT2を形成するトランジスタ形成部30を上下方向(縦方向)に配置し、このトランジスタ形成部の左側に、メタル配線(ビット線)12を配置し、また、第1トランジスタのゲートのポリシリコン層8と、第2トランジスタのソースに接続されるメタル配線13とを左右方向(横方向)に配置する。またトランジスタ形成部30の左側にn型ウェル2を配置し、このn型ウェル2の表面と第2トランジスタの第2のゲート領域部(符号4で示す領域)とに対向するようにフローティングゲート9を左右方向に配置し、このフローティングゲート9に電位を付与するコントロールゲート配線19も左右方向に配置する。

(もっと読む)

不揮発性メモリならびにその読み出し方法およびその書き込み方法

【課題】高セル密度化と、ビットラインの低抵抗化による高速化が両立し、読み出し、書き込み時の記憶内容への擾乱を受けにくい不揮発性メモリアレイを提供する。

【解決手段】複数のメモリセルは、接続領域411、第1の方向に延びる導電ビット線4010、第2の方向に延びる導電ワード線6030、および導電制御線6010,6020と共に2つの方向に2次元で配置されている。接続領域411は、1つのビット線に接続される4つのセルを含むメモリアレイを通って形成される。接続領域411は、処理を経済的にするために逆導電型領域401と同じ処理ステップで形成する。

(もっと読む)

メモリセル構造、該メモリセル構造を用いたメモリデバイス、及び該メモリデバイスを具備した集積回路

【課題】従来のメモリセルよりも小型かつ長寿命なメモリセルのデザインを提供する。

【解決手段】メモリデバイス用メモリセル構造は、フローティングゲートノードFGを有したリードトランジスタ120と、第1プログラミング端子160を有したトンネリングコンデンサ130と、第2プログラミング端子150を有したカップリングコンデンサスタック200とを具備する。トンネリングコンデンサ130及びカップリングコンデンサスタック200は、FGに接続されている。カップリングコンデンサスタック200は、FGと第2プログラミング端子150との間に直列に接続された少なくとも2つのカップリングコンデンサから成り、トンネリングコンデンサ130よりも大きい静電容量を有する。

(もっと読む)

不揮発性メモリセル及び不揮発性メモリセル内蔵データラッチ

【課題】 標準的なCMOSICの製造工程で容易に製造できて集積回路の調整用等として簡便性に優れる不揮発性メモリを提供する。

【解決手段】 フローティングゲートFGを有するNMOSトランジスタTr1と、この第1のNMOSトランジスタTr1のドレイン側とソース側に接続されたNMOSトランジスタTr2,Tr3と、フローティングゲートFGをゲートとするPMOSトランジスタTr4及びPMOSトランジスタTr5を有するとともに、NMOSトランジスタTr2,Tr3のゲートには読出し信号RDが入力され、PMOSトランジスタTr4のソースとnウェルには制御ゲート信号CGが入力され、PMOSトランジスタTr5のソースとnウェルには消去信号ERが入力され、NMOSトランジスタTr1のソースに書込みデータ信号W−Dataが入力されるように構成した。

(もっと読む)

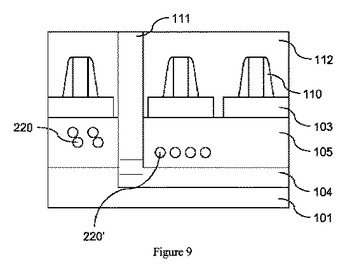

埋め込み型トラッピング層によるトランジスタの閾値電圧の調整方法

方法は、電子サブアセンブリの形成について、調整可能な閾値電圧を有する少なくとも1つの第1のトランジスタ(110)を担持する半導体層(103)が絶縁層(102、105)に接合される組み立てステップと、半導体層および第1のトラッピングゾーンが容量結合されるように、第1のトラッピングゾーン(220)が所定の第1の深さで絶縁層に形成される形成ステップであって、前記第1のトラッピングゾーンが、前記第1のトランジスタのチャネルの少なくとも下に延び、かつ前記第1のトラッピングゾーンの外側のトラップの密度より高い密度のトラップを有する形成ステップとを含み、前記第1のトランジスタからの有用な情報はこのトランジスタ内の電荷移動である。具体的な実施形態において、第2のトランジスタのチャネルの少なくとも下に延びる第2のトラッピングゾーンが、第1のトラッピングゾーンに使用されるのとは異なるエネルギーおよび/または用量および/または原子の第2の注入によって形成される。  (もっと読む)

(もっと読む)

1 - 20 / 59

[ Back to top ]