Fターム[5F102FA06]の内容

接合型電界効果トランジスタ (42,929) | 目的、効果 (2,241) | サージ入力対策(保護回路) (79)

Fターム[5F102FA06]に分類される特許

1 - 20 / 79

半導体装置の製造方法

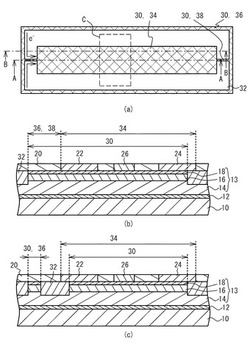

【課題】チャージアップに起因するリーク電流及び閾値電圧の変動を抑制することが可能な半導体装置の製造方法を提供すること。

【解決手段】本発明は、半導体層内に、活性領域30を含むFET34、活性領域30からなるスクライブライン36、FET34とスクライブライン36との間に位置する不活性領域32、及び不活性領域32を横断してFET34とスクライブライン36とを電気的に接続する接続領域38を設ける工程と、半導体層上に絶縁膜20を形成する工程と、ドライエッチング法により絶縁膜20に選択的に開口部21を形成する工程と、を有する半導体装置である。

(もっと読む)

半導体装置およびその製造方法

【課題】窒化ガリウム(GaN)系のHEMTを保護するダイオード構造を備えた半導体装置とその製造方法を提供する。

【解決手段】基板10のうちGaN層13に2次元電子ガスが生成される領域が活性層領域40とされ、基板10のうち活性層領域40を除いた領域にイオン注入が施されていることにより活性層領域40とは電気的に分離された領域が素子分離領域50とされている。そして、ダイオード60は素子分離領域50の層間絶縁膜20の上に配置されている。このように、基板10のうちHEMTが動作する活性層領域40とは異なる素子分離領域50を設けているので、1つの基板10にGaN−HEMTとダイオード60の両方を備えた構造とすることができる。

(もっと読む)

保護素子、半導体装置及び半導体装置の製造方法

【課題】ヘテロ接合を利用した新規な保護素子を提供すること。

【解決手段】 半導体装置10の保護部36は、配線下層11Bと、配線下層11Bとは異なるバンドギャップを有する配線上層13を有している。配線上層13は、第1部位41と中間部位43と第2部位45を含んでいる。配線上層13と配線下層11Bの接合面に形成される2次元電子ガス層が、第1部位41と中間部位43の間で分離されており、第2部位45と中間部位43の間で分離されている。第1部位41と配線下層11Bの接合面に形成される2次元電子ガスが、ドレイン電極21に電気的に接続されている。第2部位45と配線下層11Bの接合面に形成される2次元電子ガスが、ソース電極28に電気的に接続されている。中間部位43と配線下層11Bの接合面に形成される2次元電子ガスが、ゲート電極25に電気的に接続されている。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】第1の極性を有する第1の化合物半導体層と共にこれと逆極性(第2の極性)の第2の化合物半導体層を用い、化合物半導体層の再成長をすることなく、第2の極性に対応した導電型の含有量が実効的に、容易且つ確実に所期に制御された、複雑な動作を可能とする信頼性の高い高耐圧の化合物半導体装置を得る。

【解決手段】第1の極性を有する電子走行層2bと、電子走行層2bの上方に形成された第2の極性を有するp型キャップ層2eと、p型キャップ層2e上に形成された第1の極性を有するn型キャップ層2fとを有しており、n型キャップ層2fは、厚みの異なる部位2fa,2fbを有する。

(もっと読む)

半導体装置

【課題】 本実施形態は、面積効率に優れた半導体装置を実現することを目的としている。

【解決手段】 本実施形態の半導体装置は、半導体基板と、半導体基板上に形成された電界効果トランジスタと、前記電界効果トランジスタの形成領域に隣接するダイオード形成領域とを備え、前記ダイオード形成領域は前記トランジスタの形成領域と前記半導体基板上で絶縁され、前記ダイオード形成領域内は櫛状に並んだアノード電極とカソード電極から形成され、前記アノード電極とカソード電極は、電界効果トランジスタを構成する櫛状にならんだゲート電極、ソース電極およびドレイン電極とは電極方向とは異なる方向となるように形成されることを特徴とする。

(もっと読む)

集積されたダイオードを有するSOI基板を備える複合半導体装置

【課題】高電圧が印加されても、故障しにくい複合半導体装置を提供する。

【解決手段】複合半導体装置200は、ダイオード210及び絶縁層204を含むSOI基板(semiconductor on insulator)を備える。複合半導体装置200は、ダイオード210の上に形成された遷移体220及び遷移体220の上に形成されたトランジスタ230も含む。ダイオード210は半導体貫通ビア、外部電気接続部又はその両方の組み合わせを用いてトランジスタ230の両端間に接続される。

(もっと読む)

窒化物系半導体装置

【課題】ゲート絶縁膜の破壊を防止すると共に、信頼性を向上させた、ノーマリオフの双方向動作が可能な窒化物系半導体装置を提供する。

【解決手段】窒化物系半導体素子10は、第1MOSFET部30及び第2MOSFET部31を備えており、第1ゲート電極26と第2ゲート電極27との間に設けられた第1SBD金属電極28及び第2SBD金属電極29がAlGaN層20とショットキー接合されている。第1SBD金属電極28と第1電極24とが接続されており、電気的に短絡していると共に、第2SBD金属電極29と第2電極25とが接続されており、電気的に短絡している。

(もっと読む)

集積されたダイオードを備える複合半導体装置

【課題】高電圧が印加されても、故障しにくい複合半導体装置を提供する。

【解決手段】複合半導体装置200はダイオード210の上に形成された遷移体220を含み、この遷移体220は2以上の半導体層を含む。複合半導体装置200は遷移体220の上に形成されたトランジスタ230も含む。ダイオード210は半導体貫通ビア、外部電気接続部又はその両方の組み合わせを用いてトランジスタ230の両端間に接続される。

(もっと読む)

窒化物半導体装置

【課題】ダイオード等の保護素子の外付けによる部品点数の増加及び占有面積の増大を抑えた、双方向に高いアバランシュエネルギー耐量を有する窒化物半導体装置を提供する。

【解決手段】半導体基板10は、第1のn型領域12A、第2のn型領域12Bとともにトランジスタ11を構成する。半導体基板10の裏面には、裏面電極13が接合され、また、半導体基板10の上には、HFET21が形成されている。HFET21は、AlGaN層23A及びGaN層23Bを備える半導体層積層体23と、第1のオーミック電極24A、第2のオーミック電極24B、第1のゲート電極25A、第2のゲート電極25Bにより構成されている。第1のオーミック電極24Aと第1のn型領域12A、第2のオーミック電極24Bと第2のn型領域12Bはそれぞれ電気的に接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】GaN系トランジスタを簡便な構造で適切に保護することができる半導体装置及びその製造方法を提供する。

【解決手段】ゲート電極110gと保護ダイオード用電極115pとが互いに接続されている。絶縁膜113は、所定値以上の電圧がゲート電極110gに印加された場合にリーク電流を保護ダイオード用電極115pと電子走行層104及び電子供給層103との間に流し、所定値は、HEMTがオン動作する電圧より高く、ゲート絶縁膜109gの耐圧よりも低い。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】装置面積を増大させることなく、保護素子を有する半導体装置を提供する。

【解決手段】P型のIII族窒化物半導体からなる第1P型層200と、第1P型層200の一部上には、ゲート絶縁膜420およびゲート電極440とが設けられている。第1P型層200内のうち、ゲート電極440の両脇には、N型のソース領域340およびドレイン領域320が設けられている。また、第1P型層200の下には、N型のIII族窒化物半導体からなる第1N型層100が設けられている。基板内には、N型のIII族窒化物半導体とオーミック接続する材料からなるオーミック接続部(たとえばN型GaN層520)が、ソース領域340および第1N型層100と接するように設けられている。また、ドレイン電極600は、ドレイン領域320および第1P型層200と接するように設けられている。

(もっと読む)

半導体装置

【課題】充電対象素子へ充電電流を効率的に供給することが可能な半導体装置を提供する。

【解決手段】充電対象素子Cに充電電流を供給する半導体装置1は、第1導電型の半導体層1と、充電対象素子Cの第1電極に結合される第1ノードN1を有し、半導体層1の主表面上に形成される第2導電型の第1の半導体領域2と、電源電圧が供給される電源電位ノードNL1に結合される第2ノードN3および第3ノードN4を有し、第1の半導体領域2の表面において半導体層1と間隔をあけて形成される第1導電型の第2の半導体領域3と、第2ノードN3および第3ノードN4から半導体層1への電荷キャリアの移動を制限する電荷キャリア移動制限部とを備える。

(もっと読む)

スイッチング回路

【課題】ゲート電流を抑制し且つ高速動作が可能なスイッチング回路を提供する。

【解決手段】窒化物半導体層の主面上に、第1の主電極Dswと第2の主電極Sswの間に配置された制御電極Gswを有するスイッチング素子Tswと、スイッチング素子Tswの第1の主電極Dswにアノード端子が接続された第1の整流素子D1、第1の整流素子D1のカソード端子に第1の主電極DD1が接続され、スイッチング素子Tswの制御電極Gswに第2の主電極SD1が接続された第1の駆動素子TD1、スイッチング素子Tswの制御電極Gswに第1の主電極DD2が接続され、スイッチング素子の第2の主電極Sswに第2の主電極SD2が接続された第2の駆動素子TD2、及び、第1の駆動素子TD1の制御電極GD1と第2の駆動素子TD2の制御電極GD2にそれぞれ入力される制御信号を受信する入力端子IN_H,IN_Lを有する駆動回路10とを備える。

(もっと読む)

低電圧デバイス保護付き高電圧複合半導体デバイス

【課題】低電圧デバイス保護付き高電圧複合半導体デバイスを提供する。

【解決手段】電圧保護されたデバイスを含複合半導体デバイスの1つの好適な実現では、ノーマリオフ複合半導体デバイス300が、第1出力キャパシタンス318を有するノーマリオンIII-窒化物パワートランジスタ310と、このノーマリオンIII-窒化物パワートランジスタとカスコード接続された低電圧(LV)デバイス320を具えて、このノーマリオフ複合半導体デバイスを形成し、このLVデバイスは第2出力キャパシタンス348を有する。第1出力キャパシタンス対第2出力キャパシタンスの比率を、ノーマリオンIII-窒化物パワートランジスタのドレイン電圧対LVデバイスの降伏電圧の比率に基づいて設定して、LVデバイスの電圧保護を行う。

(もっと読む)

半導体装置

【課題】半導体装置内に保護ダイオードをレイアウトする。

【解決手段】半導体装置は、電界効果トランジスタ11と、電界効果トランジスタ11の形成領域30に隣接するダイオード形成領域12とを備え、ダイオード形成領域12はトランジスタの形成領域30と半導体基板上で絶縁され、ダイオード形成領域12内において、電界効果トランジスタ11のゲート電極1がバス配線7を介して半導体基板とショットキー接合とオーミック接合のいずれか又は両方の接合をする第1のダイオード電極20と、電界効果トランジスタ11のソース電極2がパッド5を介して半導体基板とオーミック接合とショットキー接合のいずれか又は両方の接合をする第2のダイオード電極21とを備えることによってゲート電極1とソース電極2間にダイオードが形成されたことを特徴とする。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】良好なノーマリ・オフ動作を可能とすることに加え、アバランシェ耐量が大きく、外部のダイオードを接続することを要せず、確実に安定動作を得ることができる信頼性の高い高耐圧のHEMTを得る。

【解決手段】化合物半導体積層構造2に形成された電極用リセス2Cを、ゲート絶縁膜6を介して電極材料で埋め込むようにゲート電極7を形成すると共に、化合物半導体積層構造2に形成された電極用リセス2Dを、少なくとも電極用リセス2Dの底面で化合物半導体積層構造2と直接的に接するように電極材料で埋め込み、化合物半導体積層構造2とショットキー接触するフィールドプレート電極8を形成する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲート電極の電界集中を緩和して耐圧の更なる向上を実現することに加え、デバイス動作速度を向上させ、アバランシェ耐量が大きく、サージに対して強く、例えばインバータ回路等に適用する場合に外部のダイオードを接続することを要せず、ホールが発生しても安定動作を得ることができる信頼性の高い高耐圧の化合物半導体装置を実現する。

【解決手段】化合物半導体積層構造2に形成された電極用リセス2Cを、ゲート絶縁膜6を介して電極材料で埋め込むようにゲート電極7を形成すると共に、化合物半導体積層構造2に形成されたフィールドプレート用リセス2Dをp型半導体で埋め込み、化合物半導体積層構造2とp型半導体層8aで接触するフィールドプレート8を形成する。

(もっと読む)

保護素子およびそれを備えた半導体装置

【課題】被保護素子に接続されることにより、被保護素子の破壊を未然に防止できる保護素子を提供すること。

【解決手段】アノード電極15とカソード電極16との間に主たる電流を流す被保護素子に対して、電気的に並列に接続される保護素子1であって、GaN層13よりもバンドギャップの大きなAlGaN層14が形成され、AlGaN層14の表面に離間してアノード電極15とカソード電極16とが形成され、アノード電極15とカソード電極と16の間の2次元電子ガス層13Aを流れる電流のオンオフを制御する制御電極19を備えたオンオフ可能領域21を備え、制御電極19が所定の抵抗体20を介してアノード電極15に接続されてなり、アノード電極15が被保護素子のアノード電極15と接続され、カソード電極16が被保護素子のカソード電極16と接続され、被保護素子より耐圧が低く設定されている。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置が有する保護膜や層間絶縁膜にかかる電界を抑制し、半導体装置の絶縁破壊耐圧を向上する。

【解決手段】半導体装置は、基板1と、基板の上方に形成されたキャリア走行層4と、キャリア走行層の上に形成された化合物半導体層5,6,7と、化合物半導体層の上に形成されたソース電極10と、基板の裏面から基板を貫通し、キャリア走行層の内部まで形成された第1の溝12と、第1の溝の内部に形成されたドレイン電極14と、ソース電極10と第1の溝12との間に位置し、化合物半導体層の上に形成されたゲート電極11と、ソース電極の斜め下方であってソース電極と第1の溝との間に位置し、基板の裏面から基板を貫通し、キャリア走行層4の内部まで形成された第2の溝13と、を備える。

(もっと読む)

半導体装置

【課題】破壊耐量が高い、2DEGを用いた半導体装置を提供する。

【解決手段】ソース・ドレイン間の耐圧よりも耐圧が低いSBDダイオード18のカソード電極がドレイン電極16に接続され、アノード電極がポリシリコンダイオード20を介してゲート電極14に接続されている。これにより、L負荷耐量試験回路によるL負荷耐量試験において、ゲート信号がターンオフされると、ドレイン電圧が印加され、SBDダイオード18にアバランシェ電流が流れ始め、電圧降下が発生し、ゲート電圧Vgが印加される。ゲートに閾値電圧Vthよりやや高い電圧(ゲートがオンする程度の電圧)が印加されると、ソース・ドレイン間が導通状態となる。これにより、ドレイン電圧がソース電極12とドレイン電極16との間の耐圧よりも低いSBDダイオード18の耐圧にクランプされた状態で、ドレイン電流が徐々に減少していく。

(もっと読む)

1 - 20 / 79

[ Back to top ]