Fターム[5F102GB02]の内容

接合型電界効果トランジスタ (42,929) | 主電流経路 (2,759) | 基板表面に平行(横型FET) (2,444) | 裏面電極取出し (197)

Fターム[5F102GB02]に分類される特許

1 - 20 / 197

三次元配置部品を有する化合物半導体集積回路

高周波増幅器

高周波半導体装置

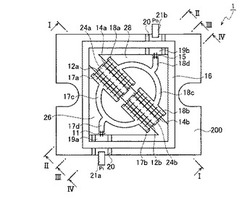

【課題】半導体チップを実装できる幅を増大し、実装基板上を有効に使用可能な高周波用半導体装置を提供する。

【解決手段】導体ベースプレートと、導体ベースプレート上に配置されたマルチセル構成の半導体チップと、導体ベースプレート上に配置され、半導体チップを内在する矩形のキャビティを形成する金属壁と、金属壁の入出力部に設けられた貫通孔とを備え、半導体チップを、金属壁に囲まれた矩形のキャビティ内において、半導体チップの長手方向が、貫通孔の設けられていない金属壁の延伸方向から0度より大で、90度より小の所定の角度に配置した半導体装置。

(もっと読む)

高周波半導体装置

【課題】ボンディングワイヤの長さを長くすることなくインダクタンスの値を大きくできる高周波用半導体装置を提供する。

【解決手段】高周波半導体装置1は、マルチセル構成の半導体チップ24と、整合回路と、半導体チップ24と整合回路間に並列に接続された複数本のボンディングワイヤ12、14とを備え、複数本のボンディングワイヤ12、14は、半導体チップ24に対して平面上で90°以下の所定の角度を有する。

(もっと読む)

半導体装置

【課題】VIAホールを高密度に形成したとしても半導体素子が割れやすくなるのを防止し、素子の形成歩留りを向上させることができる半導体装置を提供する。

【解決手段】半導体装置は、基板110と、基板の第1表面に配置され、それぞれ複数のフィンガーを有するゲート電極124、ソース電極120およびドレイン電極122と、ソース電極120の下部に配置されたVIAホールSCと、基板の第1表面とは反対側の第2表面に配置され、VIAホールを介してソース電極に接続された接地電極とを備え、VIAホールSCは、基板110を形成する化合物半導体結晶のへき開方向とは異なる方向に沿って配置される。

(もっと読む)

半導体装置

【課題】裏面電極と導通したパッドを破ることなく、複数のバイアホールの検査を短時間で実施できる半導体装置を提供する。

【解決手段】半導体装置は、基板と、該基板の裏面に形成された裏面電極と、該基板を貫通するN個(Nは2以上の整数)のバイアホール16のそれぞれを経由して該裏面電極と電気的に接続されるように該基板の表面に形成されたN個のパッドと、該N個のパッドのそれぞれに電気的に接続されたN個のエピ抵抗30とを有する。そして、該N個のエピ抵抗を介して該N個のパッドと接続された配線34と、該配線と接続された検査用パッド36と、該N個のパッド、及び該N個のバイアホールを経由して該裏面電極に電流を流すように該基板の表面に形成された電流印加用パターンと、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】高周波特性の悪化を防ぎ、耐湿性を向上させる。

【解決手段】半導体基板1の主表面上の素子領域内に、ドレイン電極2が設けられている。一端がドレイン電極2に接続されたドレイン配線5が主表面上に設けられている。主表面上の素子領域外に、ドレイン配線5とは離間したドレイン電極パッド12が設けられている。Auメッキ層9が主表面上に設けられ、主表面との間に空隙10が形成されている。空隙10はドレイン配線5の一端とドレイン電極2を内包する。硬化されたポリイミド膜14が空隙10の開口部11を閉塞し、ドレイン電極パッド12を覆うことなく、ドレイン配線5の他端を覆っている。空隙10の内面に撥液膜15が設けられている。硬化されたポリイミド膜14に設けられた開口16を介してAuメッキ層18により、ドレイン配線5の他端とドレイン電極パッド12が接続されている。ドレイン配線5の他端はポリイミド膜14から出ていない。

(もっと読む)

ワイドバンドギャップ半導体デバイス

【課題】製造が容易であり、デバイス特性の変動を抑制できるワイドバンドギャップ半導体デバイスを得る。

【解決手段】SiC基板1上にAlN格子緩和層2、GaNチャネル層3、及びAlGaN電子供給層4が順に設けられている。これらは、1.42eVより広いバンドギャップを持つ半導体材料からなる。AlGaN電子供給層4に、トランジスタを含む活性領域9が設けられている。SiC基板1は、光学的な不純物又は格子欠陥により着色され、可視光領域の光を吸収する。従って、このデバイスは波長360nm〜830nmの可視光領域の光に対して不透明である。

(もっと読む)

半導体素子および半導体素子の製造方法

【課題】バッファ層を有する半導体素子において、チャネルの基準電位を固定する半導体素子及びその製造方法を提供する。

【解決手段】基板10と、基板上に設けられ、エネルギーギャップの異なる複数種類の窒化物半導体が積層された積層体を少なくとも1層有するバッファ層20と、バッファ層上に設けられた窒化物半導体のチャネル層30と、バッファ層の側面に電気的に接続された側面電極60と、チャネル層の上方に形成され、チャネル層と電気的に接続されたチャネル電極52,56とを備える半導体素子。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体パッケージ内における半導体素子の位置ずれを抑制することができる半導体装置を提供すること。

【解決手段】実施形態に係る半導体装置10は、凸部23が形成されたパッケージ基板11、導電性の接着剤25、およびパッケージ基板11上に実装された半導体素子14、を具備する。パッケージ基板11は、少なくとも2箇所に凸部23が形成された基板である。導電性の接着剤25は、凸部23を含むパッケージ基板11上に形成される。パッケージ基板11上に実装される半導体素子14は、各凸部23に係合する複数のバイアホール24を有している。さらに、半導体素子14は、少なくとも2箇所のバイアホール24が、各凸部23に接着剤25を介して係合するようにパッケージ基板11上に実装される。

(もっと読む)

窒化物半導体装置

【課題】ダイオード等の保護素子の外付けによる部品点数の増加及び占有面積の増大を抑えた、双方向に高いアバランシュエネルギー耐量を有する窒化物半導体装置を提供する。

【解決手段】半導体基板10は、第1のn型領域12A、第2のn型領域12Bとともにトランジスタ11を構成する。半導体基板10の裏面には、裏面電極13が接合され、また、半導体基板10の上には、HFET21が形成されている。HFET21は、AlGaN層23A及びGaN層23Bを備える半導体層積層体23と、第1のオーミック電極24A、第2のオーミック電極24B、第1のゲート電極25A、第2のゲート電極25Bにより構成されている。第1のオーミック電極24Aと第1のn型領域12A、第2のオーミック電極24Bと第2のn型領域12Bはそれぞれ電気的に接続されている。

(もっと読む)

半導体装置の製造方法

【課題】設計された形状およびサイズのゲート電極を形成することが可能な半導体装置の製造方法を提供すること。

【解決手段】本実施形態に係る半導体装置の製造方法は、半導体層12の表面上のうち、互いに離間した位置に、チタン層17a、18a、アルミニウム層17b、18b、ニッケル層17c、18c、金層17d、18dがこの順で積層した積層体17、18を形成し、これらを、アルミニウムの融点より高い温度で加熱して複数の金属体17´、18´を形成するするとともに、これらの複数の金属体17´、18´を半導体層12にオーミック接触させる。この後、複数の金属体17´、18´を薄膜化して複数の合金層13a、14aを形成し、合金層13a、14aを含むドレイン電極13およびソース電極14を形成する。次に、ドレイン電極13とソース電極14との間のレジスト層19に開口部20し、この開口部20内にゲート電極15を形成する。

(もっと読む)

半導体電力増幅器

【課題】ビアホールの数を少なくしてもループ発振などの特性劣化が生じにくい半導体電力増幅器を提供する。

【解決手段】半導体電力増幅器は、ゲート電極Gと、ドレイン電極Dと、前記ゲートフィンガー電極に対向して配置されるソースフィンガー電極横手方向の両サイドに引き出される2つのソース電極Sと、を有するユニットFETと、前記ユニットFETが、前記ソース電極間を結ぶ略直線方向に複数個並列配置され、隣り合うユニットFET間に存在する2つのソース電極の両方を共通して高周波グランド面と接続する第1の接地インダクタンス値を有する第1のビアホール18Kと、隣り合うユニットFETが存在しない側のソース電極上に配置され、接地インダクタンスを等しくするために前記高周波グランド面に接続する第2の接地インダクタンス値を有する第2のビアホール18Dと、を有する。

(もっと読む)

半導体装置の製造方法

【課題】設計の自由度を損なわずに、高いオン特性とオフ特性を持つ半導体装置を容易に製造する。

【解決手段】可視光に対して透明な半導体基板1の表面にソース電極2及びドレイン電極3を形成する。半導体基板1の表面においてソース電極2とドレイン電極3との間に表側ゲート電極4を形成する。半導体基板1の表面においてソース電極2とドレイン電極3との間以外の領域に合わせマーク5を形成する。半導体基板1を透過して見える合わせマーク5に基づいて半導体基板1を位置合わせして、半導体基板1の裏面において表側ゲート電極4と対向する位置に裏側ゲート電極6を形成する。

(もっと読む)

集積電力段

【課題】集積電力段において、入力電圧を集積電力段の一側面(例えば上面)で受け取り、出力電圧を集積電力段の反対側面(例えば底面)から出力する。

【解決手段】集積電力段は負荷段の上に位置する共通ダイを備え、共通ダイはドライバ段102及び電力スイッチ104を備える。電力スイッチは制御トランジスタ110及び同期トランジスタ112を含む。制御トランジスタのドレインD1が共通ダイの入力電圧を共通ダイの一側面(例えば上面)で受ける。制御トランジスタのソースS1が同期トランジスタのドレインD2に結合され、前記共通ダイの出力電圧を共通ダイの反対側面(例えば底面)で出力する。電力段の下にインターポーザ106を含めることができる。インターポーザは共通ダイの反対側面で共通ダイの出力電圧に結合される出力インダクタ118及び必要に応じ出力キャパシタ120を含む。

(もっと読む)

半導体装置

【課題】冷却効率を向上させることができる半導体装置を提供すること。

【解決手段】実施形態に係る半導体装置10は、裏面に複数の凹部16を有するシリコン基板11と、この基板11の表面上に形成された半導体層12と、半導体層12の表面上に、互いに離間して形成されたドレイン電極13およびソース電極14と、ドレイン電極13とソース電極14との間の半導体層12上に形成されたゲート電極15と、複数の凹部16の内部を含むシリコン基板11の裏面全体に形成された裏面金属17と、を具備する。

(もっと読む)

半導体装置およびその製造方法

【課題】放熱性と耐久性に優れた半導体装置およびその製造方法を提供する。

【解決手段】導電ベースプレートと、導電ベースプレート上に接合される半導体チップと、半導体チップと導電ベースプレートとの接合面の中央部に配置された第1接着剤と、半導体チップと導電ベースプレートとの接合面の周辺部に配置された第2接着剤とを備え、第1接着剤は第2接着剤よりも相対的に熱伝導率が高く、第2接着剤は第1接着剤より相対的に接合力が高い半導体装置。

(もっと読む)

半導体装置

【課題】差分周波数Δfが数百MHzにおいても高周波半導体チップのドレイン端面の電圧が平滑化された半導体装置を提供する。

【解決手段】高周波半導体チップと、高周波半導体チップの入力側に配置された入力側分布回路と、高周波半導体チップの出力側に配置された出力側分布回路と、入力側分布回路に接続された高周波入力端子と、出力側分布回路に接続された高周波出力端子と、高周波半導体チップのドレイン端子電極近傍に配置された平滑化キャパシタとを備え、高周波半導体チップと、入力側分布回路と、出力側分布回路と、平滑化キャパシタとが1つのパッケージに収納されたことを特徴とする半導体装置。

(もっと読む)

半導体装置

【課題】電流コラプスが抑制され、耐圧の高い半導体装置を提供する。

【解決手段】基板110と、基板110の上方に形成された窒化物系化合物半導体からなるバッファ層120と、バッファ層120上に形成された窒化物系化合物半導体からなるチャネル層130と、チャネル層130の上方に形成された窒化物系化合物半導体からなる電子供給層132と、電子供給層132の上方に形成された第1の電極136と、電子供給層132の上方に形成された第2の電極138と、を備え、第2の電極138の電位に対して、基板110の電位および第1の電極136の電位が同じ側であり、第2の電極138の下の領域のバッファ層120の厚さおよびチャネル層130の厚さの合計が、第1の電極136の下の領域のバッファ層120の厚さおよびチャネル層130の厚さの合計より、大きい半導体装置。

(もっと読む)

III−V族トランジスタとIV族ダイオードを含む積層複合デバイス

【課題】III−V族トランジスタとIV族ダイオードからなる積層複合デバイスを提供する。

【解決手段】積層複合デバイスはIV族ダイオードと該IV族ダイオードの上に積層されたIII−V族トランジスタとを備える。IV族ダイオードのカソードがIII−V族トランジスタのソースと接触され、IV族ダイオードのアノードがIII−V族トランジスタのゲートに結合されて前記複合デバイスパッケージの底面上の複合アノードを与え、III−V族トランジスタのドレインが複合デバイスパッケージの底面に対向する上面上の複合カソードを与える。

(もっと読む)

1 - 20 / 197

[ Back to top ]