Fターム[5F102GK02]の内容

接合型電界効果トランジスタ (42,929) | バッファ層(中間層) (2,318) | 単一半導体層 (1,628) | 4族 (58)

Fターム[5F102GK02]に分類される特許

1 - 20 / 58

炭化珪素半導体装置およびその製造方法

【課題】ゲート領域近傍のチャネル部分の抵抗を低減することにより、従来よりも特性オン抵抗が低い炭化珪素半導体装置を提供する。

【解決手段】炭化珪素半導体装置は、基板11と、基板11上に設けられ、主表面13Aと、主表面13Aと交差する厚さ方向とを有する炭化珪素層4とを有している。炭化珪素層4は、チャネル層13と、ソース領域15と、ドレイン領域17と、ソース領域15とドレイン領域17との間において、厚さ方向に沿って主表面13Aからチャネル層13中に突き出るように延びるゲート領域16とを含んでいる。ゲート領域16の対向方向に沿った寸法は、主表面13Aから離れるにつれて小さくなっている。

(もっと読む)

シリコン基板上に高電子移動度トランジスタを成長させた構造及びその方法

【課題】シリコン基板上に高電子移動度トランジスタを成長させた構造及びその方法の提供。

【解決手段】本シリコン基板上に高電子移動度トランジスタを成長させた構造及びその方法は、半導体産業において半導体装置製造に用いられる。本発明によると、UHVCVDシステムを使用してGeフィルムをSi基板上に成長させ、その後、高電子移動度トランジスタを該Geフィルム上に成長させることで、バッファ層の厚さとコストを低減する。該Geフィルムの機能は、Si基板上にMOCVDによりIII-V MHEMT構造を成長させるときに、シリコン酸化物の形成を防止することである。本発明においてMHEMTを使用する理由は、MHEMT構造中の変成バッファ層がGeとSi基板間の非常に大きな格子不整合度のために形成される貫通転位をブロックし得ることにある。

(もっと読む)

半導体デバイス、半導体基板、半導体基板の製造方法および半導体デバイスの製造方法

【課題】単一基板上にソース・ドレインを同一工程で同時形成したIII−V族半導体のnMISFETおよびIV族半導体のpMISFETのソース・ドレイン領域抵抗または接触抵抗を小さくする。

【解決手段】第1半導体結晶層104に形成された第1チャネル型の第1MISFET120の第1ソース124および第1ドレイン126が、第1半導体結晶層104を構成する原子と、ニッケル原子との化合物、または、コバルト原子との化合物、またはニッケル原子とコバルト原子との化合物からなり、第2半導体結晶層106に形成された第2チャネル型の第2MISFET130の第2ソース134および第2ドレイン136が、第2半導体結晶層106を構成する原子と、ニッケル原子との化合物、または、コバルト原子との化合物、または、ニッケル原子とコバルト原子との化合物からなる。

(もっと読む)

半導体装置

【課題】電流の減少を抑制することが可能な半導体装置を提供すること。

【解決手段】本発明は、炭化シリコンからなる基板10と、基板10上に設けられた窒化アルミニウムからなるバッファ層12と、バッファ層12上に設けられた窒化ガリウムからなるチャネル層14と、チャネル層14上に設けられた窒化物半導体からなる電子供給層16と、電子供給層16上に設けられたソース電極20、ドレイン電極22及びゲート電極24と、を具備し、バッファ層12の厚さの逆数の平均値の逆数は20nm以下であり、バッファ層12の最も厚い部分と、最も薄い部分との厚さの差は6nm以上であることHEMT100である。

(もっと読む)

半導体基板、半導体装置および半導体基板の製造方法

【課題】十分な感度を有したp型キャリアのホール素子の製造に適した半導体基板を提供する。

【解決手段】表面の全部または一部がシリコン結晶面であるベース基板と、前記ベース基板の上に位置し、前記シリコン結晶面に達する開口を有し、結晶の成長を阻害する阻害体と、前記開口の底部の前記シリコン結晶面の上に位置する第1結晶層と、前記第1結晶層の上に位置し、互いに離して配置した一対の第1金属層と、前記第1結晶層の上に位置し、互いに離して配置した一対の第2金属層と、を有し、前記一対の第1金属層のそれぞれを結ぶ第1最短線と、前記一対の第2金属層のそれぞれを結ぶ第2最短線とが、交わる関係、または、ねじれの位置関係にある半導体基板を提供する。

(もっと読む)

半導体基板、半導体装置、および半導体基板の製造方法

【課題】GaN系半導体は、面方位が(111)のシリコン基板上にエピタキシャル成長される。GaNの格子定数と、とシリコン(111)面の格子定数の差が、約17%と大きいのでめ、成長されたGaNには1010cm−2を超える転位が導入される。転位により、GaNを用いたトランジスタのリーク電流が増大する。また、トランジスタの移動度が低下する。

【解決手段】シリコン基板と、シリコン基板の(150)面上に、エピタキシャル成長された窒化物半導体層と、を備える半導体基板を提供する。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】所望の不純物濃度と、高い結晶性とを有するドリフト層を有する炭化珪素半導体装置およびその製造方法を提供する。

【解決手段】バッファ層31は、基板30上に設けられ、不純物を含有する炭化珪素から作られ、1μmより大きく7μmより小さい厚さを有する。ドリフト層32は、バッファ層31上に設けられ、バッファ層31の不純物濃度よりも小さい不純物濃度を有する炭化珪素から作られている。

(もっと読む)

炭化ケイ素金属半導体電界効果トランジスタ及び炭化ケイ素の金属半導体電界効果トランジスタを製造する方法

【課題】深いレベルのドーパントがほとんど存在しない半絶縁性のSiC基板上にMESFETを形成することにより、バックゲート効果が減少された、SiCのMESFETを提供する。

【解決手段】半絶縁性の基板上10に選択的にドープされたP型の炭化珪素の層13、及びN型のエピタキシャル層14を積層し、背面ゲート効果を減少させる。また2つの凹部を有するゲート構造体も備える。これにより、出力コンダクタンスを1/3に減少することができ、また電力のゲインを3db増加することができる。クロム42をショットキーゲート接点として利用することもでき、酸化物−窒化物−酸化物(ONO)の保護層60を利用して、MESFET内の表面効果を減少させる。また、ソース及びドレインのオーム接点をn型チャネル層上に直接形成して、これにより、n+領域を製造する必要がなくなる。

(もっと読む)

ソース領域の下にp型埋込み層を備えたトランジスタ及びその作製方法

【課題】本発明は、金属半導体電界効果トランジスタ(MESFET)を提供する。

【解決手段】このMESFETは、ソース(13)とドレイン(17)とゲート(24)とを備えている。このゲート(24)を、ソース(13)とドレイン(17)の間及びn導電型チャネル層(18)上に設ける。ドレイン(17)に向かって延びている端部を備えるp導電型領域(14)をソースの下に設ける。このp導電型領域(14)をn導電型チャネル領域(18)から隔ててソース(13)に電気的に結合させる。

(もっと読む)

半導体積層構造および電界効果トランジスター

【課題】ダイヤモンド基板上に、クラックが抑制され、かつ膜厚が厚い単結晶窒化物層を有する半導体積層構造を提供すること。

【解決手段】ダイヤモンド基板上に直接成長した窒化物層が多結晶となる上記課題を解決するため、本発明に係る半導体積層構造は、ダイヤモンド基板と、ダイヤモンド基板上の、Siを含む第1の層と、第1の層上の、単結晶窒化物で構成される第2の層とを備える。Siを含む第1の層をダイヤモンド基板と第2の層との間に設けることにより、第2の層の膜厚を大きくしても、第2の層を構成する窒化物を、クラックの抑制された単結晶とすることができる。したがって、当該半導体積層構造を利用することで、高いドレイン電流および出力電力密度を有する電界効果トランジスターを実現することが可能である。

(もっと読む)

電界効果トランジスタ

【課題】スイッチング速度を向上でき、動作不良品を低減できる、横型の電界効果トランジスタを提供する。

【解決手段】ゲート配線43は、基部44と、基部44から突出する複数の指状部45と、隣接する指状部45の先端部46を接続する接続部47と、を有する。ゲート配線43の指状部45は、ソース配線23の指状部25とドレイン配線33の指状部35と、の間に配置されている。ゲート配線43の基部44は、ソース配線23の基部24とドレイン配線33の指状部35との間に配置され、かつ、ソース配線23の指状部25との間に絶縁膜を介在させて指状部25と交差している。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート−ソース間およびゲート−ドレイン間のキャパシタンスの低減と、JFETをオンさせる際に必要なゲート印加電圧が高電圧になることを抑制する。

【解決手段】n-型チャネル層2の表面に直接p+型ゲート領域4を形成し、p+型ゲート領域4のうちn-型チャネル層2と接する部分と比較して、n-型チャネル層2から離れた部分が幅広となるようにする。そして、p+型ゲート領域4のうち幅広とされた部分がn-型チャネル層2から所定距離離れるようにする。例えば、n-型チャネル層2に凹部2aを形成し、この凹部2a内にp+型ゲート領域4を形成する。

(もっと読む)

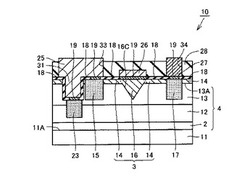

炭化珪素半導体装置およびその製造方法

【課題】ゲート−ソース間およびゲート−ドレイン間のキャパシタンスの低減と、JFETをオンさせる際に必要なゲート印加電圧が高電圧になることを抑制する。

【解決手段】凹部4c内に形成されたi型(イントリンシック半導体)側壁層5を介してp+型ゲート領域6を形成する。このような構成とすれば、n+型層4とp+型ゲート領域6との間にさらにp+型ゲート領域6よりも低濃度のp-型層が必要とされない。このため、n-型チャネル層3に直接接触している高濃度のp+型ゲート領域6によって、n-型チャネル層3内に伸びる空乏層幅を制御できる。したがって、n+型層4とp+型ゲート領域6との間にさらにp-型層が備えられる場合と比較して、ゲート印加電圧が高電圧になることを抑制できる。また、p+型ゲート領域6の側面がi型側壁層5によってn+型層4と分離されるため、ゲート−ソース間およびゲート−ドレイン間のキャパシタンスを低減できる。

(もっと読む)

ゲルマニウムベースの量子井戸デバイス

量子井戸トランジスタは、ゲルマニウムの量子井戸チャネル領域を有する。シリコンを含有したエッチング停止領域が、チャネル近くへのゲート誘電体の配置を容易にする。III−V族材料のバリア層がチャネルに歪みを付与する。チャネル領域の上及び下の傾斜シリコンゲルマニウム層によって性能が向上される。複数のゲート誘電体材料によって、high−k値のゲート誘電体の使用が可能になる。  (もっと読む)

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ゲート−ソース間およびゲート−ドレイン間のキャパシタンスの低減を図ると共に、JFETをオンさせる際に必要なゲート印加電圧が高電圧になることを抑制する。

【解決手段】p+型ゲート領域2をSiC基板1の内部に埋め込んだ構造とする。これにより、ゲート−ソース間およびゲート−ドレイン間のキャパシタンスの低減を図ることが可能となる。また、p+型ゲート領域2がn-型チャネル層3に直接接触させられる構造であるため、p+型ゲート領域2から広がる空乏層によって容易にn-型チャネル層3をピンチオフさせることができ、JFETをオンさせる際に必要なゲート印加電圧が高電圧になることを抑制できる。

(もっと読む)

半導体装置およびその製造方法

【課題】DモードとEモードの素子を組み合わせた半導体装置およびその製造方法を提供する。

【解決手段】DモードとEモードのJFETにおけるチャネル領域を設定する場所にそれぞれ凹部2aと凸部2bを備えることで、同一基板上に厚みが異なるn型チャネル層3を形成する。そして、このような厚みが異なるn型チャネル層3によってDモードとEモードで作動するJFETを同一基板上に備えることができるため、SiCでもDモードとEモードのJFETを組み合わせたSiC半導体装置を実現することが可能となる。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル層の厚みのバラツキを抑制できるJFET、MOSFETもしくはMESFETを備えた半導体装置およびその製造方法を提供する。

【解決手段】n+型層3に対して異方性エッチングを行うことによって凹部4を形成したのち、この凹部4内にエピタキシャル成長させることによってn型チャネル層5を形成する。これにより、n型チャネル層5を一定の膜厚かつ一定の濃度で形成することが可能となる。このため、従来の構造と異なり、n型チャネル層5の膜厚が一定なバラツキのない構造とすることが可能となる。したがって、JFETの特性も一定とすることが可能となる。

(もっと読む)

III−V族チャネルとIV族ソース−ドレインとを有する半導体デバイス、及びその製造方法

【課題】III−V族チャネルとIV族ソース−ドレインとを有する半導体デバイス及びその製造方法を提供する。

【解決手段】III−V族材料のエネルギーレベルの密度とドーピング濃度をIII−V族材料とIV族材料のヘテロエピタキシと素子の構造設計によって高める。本発明の方法は、基板100上にダミーゲート材料層を堆積し、フォトリソグラフィでダミーゲート材料層にダミーゲートを区画することと、ダミーゲートをマスクとして使用し、セルフアライン型イオン注入によってドーピングを行い、高温で活性化を行い、ソース−ドレイン108を形成することと、ダミーゲートを除去することと、ソース−ドレインのペアの間の基板にエッチングで凹陥部を形成することと、凹陥部にエピタキシャル法によりチャネル含有スタック素子112を形成することと、チャネル含有スタック素子上にゲート120を形成することと、を含む。

(もっと読む)

イオン注入せずに縦型接合形電界効果トランジスタおよびバイポーラ接合トランジスタを製造する方法およびそれによって製造されたデバイス

縦型接合形電界効果トランジスタ(VJFET)またはバイポーラ接合トランジスタ(BJT)のような半導体デバイスを製造する方法が記載される。その方法はイオン注入を必要としない。VJFETデバイスは、エピタキシャル成長した埋め込みゲート層のみでなく、エピタキシャル再成長したn型チャネル層及びエピタキシャル再成長したp型ゲート層も有する。その方法で製造されたデバイスも記載される。 (もっと読む)

横型接合型電界効果トランジスタ

【課題】漏れ電流の発生を防止すると共に、十分な耐圧を実現することが可能な横型接合型電界効果トランジスタを提供する。

【解決手段】この発明に従った横型JFET10では、バッファ層11は、SiC基板1の主表面上に位置し、p型不純物を含む。チャネル層12は、バッファ層11上に位置し、バッファ層11におけるp型不純物の濃度より高い濃度のn型不純物を含む。n型のソース領域15およびドレイン領域16は、チャネル層12の表面層において互いに間隔を隔てて形成され、p型のゲート領域17は、チャネル層12の表面層においてソース領域15およびドレイン領域16の間に位置する。バリア領域13は、チャネル層12とバッファ層11との境界領域において、ゲート領域17の下に位置する領域に配置され、バッファ層11におけるp型不純物の濃度より高い濃度のp型不純物を含む。

(もっと読む)

1 - 20 / 58

[ Back to top ]