Fターム[5F102GM09]の内容

接合型電界効果トランジスタ (42,929) | ゲート下介在層(ゲートメタル電極底面とチャネル層表面間に介在する層) (3,125) | 不純物濃度分布が不均一 (60)

Fターム[5F102GM09]に分類される特許

1 - 20 / 60

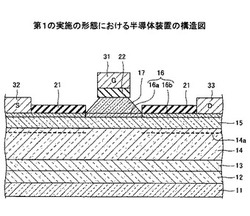

半導体装置の製造方法及び半導体装置

【課題】オン抵抗を増加させることなく、ノーマリーオフとなる半導体装置を提供する。

【解決手段】基板11の上に、第1の半導体層14、第2の半導体層15及びp型の不純物元素が含まれている半導体キャップ層16を順次形成する工程と、前記半導体キャップ層を形成した後、開口部を有する誘電体層21を形成する工程と、前記開口部において露出している前記半導体キャップ層の上に、p型の不純物元素が含まれている第3の半導体層17を形成する工程と、前記第3の半導体層の上にゲート電極31を形成する工程と、を有することを特徴とする半導体装置の製造方法により上記課題を解決する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】長期にわたって安定した動作が可能な化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1上方に形成された電子走行層3及び電子供給層5と、電子供給層5上方に形成されたゲート電極11g、ソース電極11s及びドレイン電極11daと、電子供給層5とゲート電極11gとの間に形成された第1のp型半導体層7aと、ソース電極11sと電子供給層5との間に形成されたp型半導体層7と、が設けられている。第2のp型半導体層7上のソース電極11sには、第1の金属膜11saと、第1の金属膜11saにゲート電極11g側で接し、第1の金属膜11saよりも抵抗が大きい第2の金属膜11sbと、が設けられている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】ゲート電極とチャネル層との間の障壁層に低抵抗領域を備えた構成において、ゲートリーク電流を防止することによりドレイン電流の最大値の向上を図ることが可能な半導体装置を提供する。

【解決手段】化合物半導体で構成されたチャネル層14と、チャネル層14上に設けられた上部障壁層15とを備え、上部障壁層15における表面層には、不純物を含有することにより周囲よりも低抵抗に保たれた低抵抗領域15gが設けられている。また、この低抵抗領域15gを挟んだ位置において上部障壁層15に接続されたソース電極17sおよびドレイン電極17dを備えている。さらに、低抵抗領域15g上に設けられたゲート絶縁膜18と、このゲート絶縁膜18を介して低抵抗領域15g上に設けられたゲート電極19とを備えている。

(もっと読む)

化合物半導体基板

【課題】化合物半導体層全体の膜厚を抑制しつつ、半導体素子の高い性能と信頼性を両立することのできる化合物半導体基板を提供する。

【解決手段】シリコン単結晶の基板12と、基板上に形成される化合物半導体の第1の半導体層16と、第1の半導体層上に形成され、第1の半導体層よりもバンドギャップエネルギーの大きい、化合物半導体の障壁層18と、障壁層上に形成され、障壁層よりもバンドギャップエネルギーの小さい化合物半導体の第2の半導体層20と、第2の半導体層上に形成され、第2の半導体層よりもバンドギャップエネルギーの大きい化合物半導体の第3の半導体層22とを有することを特徴とする化合物半導体基板。

(もっと読む)

半導体装置とその製造方法

【課題】 エッチングによるダメージを抑制しながら、ヘテロ接合面の近傍に負イオンを導入する技術を提供する。

【解決手段】 導入領域8上に保護膜30を形成する保護膜形成工程と、保護膜形成工程の後に、導入領域8を負イオンを含むプラズマに曝すプラズマ工程を備えている。保護膜30は、プラズマに対するエッチング速度が導入領域8よりも小さい。保護膜30には、負イオンを通過させることが可能な材料が用いられている。プラズマ中の負イオンは、保護膜30を通過し、導入領域8に導入される。

(もっと読む)

テラヘルツ波素子

【課題】単色性が強く、高効率にテラヘルツ波を発生または検出することができるテラヘルツ波素子を提供する。

【解決手段】テラヘルツ波素子100は、バッファ層102と電子供給層104とのヘテロ接合を含む半導体多層構造101〜104と、半導体多層構造101〜104上に形成されたゲート電極105、ドレイン電極106およびソース電極107とを有し、ゲート電極105とヘテロ接合界面との間の静電容量は、ドレインとソースとの間を流れる電流の方向と直交する方向に周期的に、第1の静電容量と第1の静電容量の値と異なる第2の静電容量とを有している。

(もっと読む)

半導体装置

【課題】電流コラプスの発生を抑制できるIII族窒化物半導体トランジスタおよびその製造方法を提供する。

【解決手段】FET1では、第1窒化物半導体層103の上に第2窒化物半導体層104が設けられ、少なくとも一部が第2窒化物半導体層104に接するようにソース電極106およびドレイン電極107が設けられている。第2窒化物半導体層104の上面においてソース電極106とドレイン電極107との間に位置するように凹部110aが形成されており、ゲート電極108が凹部110aの開口を覆うように凹部110aの上方に設けられている。

(もっと読む)

高電子移動度トランジスタ

【課題】ノーマリオフ特性を得つつスイッチング特性が向上した高電子移動度トランジスタ(HEMT)を提供する。

【解決手段】窒化物半導体からなるHEMT100は、n型不純物を含むか又はアンドープの第1層103と、第1層上に設けられ第1層よりもバンドギャップエネルギーが大きい第2層105と、第2層上に設けられp型不純物を含む第3層106と、第3層上に設けられ下側から上側に向かってバンドギャップエネルギーが小さくなっている第4層107と、を有する。

(もっと読む)

炭化珪素半導体装置

【課題】従来よりオン抵抗が低くかつ高い耐圧を有する炭化珪素半導体装置を提供する。

【解決手段】この発明に従ったJFET10は、n型基板11と、p型層2、12と、n型層13と、ソース領域15と、ドレイン領域17と、ゲート領域16とを備える。n型基板11は、{0001}面に対するオフ角が32°以上である主表面11Aを有し、炭化珪素(SiC)からなる。p型層2、12は、n型基板11の主表面11A上に形成され、導電型がp型である。n型層13は、p型層2、12上に形成され、導電型がn型である。ソース領域15およびドレイン領域17は、n型層13において、互いに間隔を隔てて形成され、導電型がn型である。ゲート領域16は、n型層13において、ソース領域15とドレイン領域17との間の領域に形成され、導電型がp型である。

(もっと読む)

半導体装置、及び半導体装置の製造方法

【課題】BiFETデバイスに含まれるFETのオン抵抗の悪化を抑制する。

【解決手段】共通基板1上に第1SL10及び第2SL20積層体が順に形成された半導体装置であって、第2積層体が除去されて残存する第1積層体は、電界効果型トランジスタを構成し、第1積層体上に積層された第2積層体は、電界効果型トランジスタとは異なる素子(バイポーラトランジスタ)を構成し、電界効果型トランジスタを構成する第1積層体は、第1積層体に形成されるリセスの停止位置を規定し、かつInGaPから成るエッチング停止層10と、リセス内に配置されるゲート電極25の下方に配置され、かつAlGaAsから成る下部化合物半導体層8と、エッチング停止層10と下部化合物半導体層8との間に挿入され、エッチング停止層に含まれるリンが下部化合物半導体層まで熱拡散し、下部化合物半導体層を構成する元素と化合することを抑止するスペーサ層9とを含む。

(もっと読む)

化合物半導体装置

【課題】プレーナドープの高性能性を保持したまま特性変動を抑制できる化合物半導体装置を提供する。

【解決手段】化合物半導体からなるHEMT構造の化合物半導体装置において、チャネル層へ電子を供給する電子供給層14,16,18が、n型不純物のプレーナドープ層で形成されており、同一の電子供給層におけるプレーナドープ層15,17が2分割以上に分割されている。

(もっと読む)

保護素子およびそれを備えた半導体装置

【課題】被保護素子に接続されることにより、被保護素子の破壊を未然に防止できる保護素子を提供すること。

【解決手段】アノード電極15とカソード電極16との間に主たる電流を流す被保護素子に対して、電気的に並列に接続される保護素子1であって、GaN層13よりもバンドギャップの大きなAlGaN層14が形成され、AlGaN層14の表面に離間してアノード電極15とカソード電極16とが形成され、アノード電極15とカソード電極と16の間の2次元電子ガス層13Aを流れる電流のオンオフを制御する制御電極19を備えたオンオフ可能領域21を備え、制御電極19が所定の抵抗体20を介してアノード電極15に接続されてなり、アノード電極15が被保護素子のアノード電極15と接続され、カソード電極16が被保護素子のカソード電極16と接続され、被保護素子より耐圧が低く設定されている。

(もっと読む)

窒化物半導体装置

【課題】窒化物半導体装置において、高温且つ高電圧下のスイッチング時においても電流コラプスによるオン抵抗の増大が生じないようにする。

【解決手段】基板1上には、バッファ層2、GaNからなるチャネル層3及びアンドープAlGaNからなるバリア層4が順次形成されている。チャネル層3は、該チャネル層3の下部にp型不純物層3aを有し、その上にアンドープ層3bを有している。バリア層4及びチャネル層3の端部が除去されており、露出したバリア層4及びチャネル層3の側面と接するように、それぞれソース電極5及びドレイン電極6が設けられている。バリア層4上におけるソース電極5とドレイン電極6との間の領域にはゲート電極7が設けられている。

(もっと読む)

電界効果トランジスタ

【課題】 本発明は、低消費電力で動作する論理回路に応用できる電界効果トランジスタを提供することを目的とするものである。

【解決手段】 ソース電極とソース電極が接する半導体の伝導帯又は価電子帯との間に障壁を有しており、ソース電極から障壁を通して流れ込む電子又はホールをゲート電圧により調整できる構成を有することを特徴とするnチャンネル又はpチャンネルの電界効果トランジスタ。

(もっと読む)

化合物半導体装置

【課題】窒化物化合物半導体装置において、ゲートリーク電流を抑制する。

【解決手段】化合物半導体装置20は、基板21と、前記基板上方に形成された窒化物半導体よりなるキャリア走行層22を含む半導体積層構造と、前記半導体積層構造上方に形成されたゲート電極26、ソース電極27A、ドレイン電極27Bと、前記半導体積層構造上方であって、ゲート電極とソース電極の間、及び、ゲート電極とドレイン電極との間に形成された絶縁膜28と、前記絶縁膜のうち、ゲート電極とソース電極の間、及びゲート電極とドレイン電極の間に形成された開口と、前記開口に埋め込まれたアルミナ膜29と、を備える。

(もっと読む)

半導体装置

【課題】オフ時のリーク電流を低減し、パワースイッチング素子に適用可能なノーマリーオフ型の半導体装置を提供する。

【解決手段】基板101と、基板101の上に形成されたアンドープGaN層103と、アンドープGaN層103の上に形成されたアンドープAlGaN層104と、アンドープGaN層103又はアンドープAlGaN層104の上に形成されたソース電極107及びドレイン電極108と、アンドープAlGaN層104の上に形成され、ソース電極107とドレイン電極108との間に配置されたp型GaN層105と、p型GaN層105の上に形成されたゲート電極106とを備え、アンドープGaN層103は、チャネルを含む活性領域113と、チャネルを含まない不活性領域112とを有し、p型GaN層105は、ソース電極107を囲むように配置されている。

(もっと読む)

III−V族化合物半導体エピタキシャルウェハ及びその製造方法

【課題】コンタクト層に不純物として供給するTe、Seのメモリーの影響を小さくしつつ、コンタクト抵抗を低減し、かつ、特性変動や信頼性低下を抑制しつつ、電子供給層の不純物濃度を高め、オン抵抗を低減したIII−V族化合物半導体エピタキシャルウェハを提供する。

【解決手段】単結晶基板11上に、GaAs層、AlGaAs層からなるバッファ層12a,12b、n型不純物を含有するAlGaAs層13,17又はInGaP層若しくはSiプレナードープ層からなる電子供給層、InxGa(1-x)As層からなるチャネル層15、アンドープ又は低濃度n型不純物を含有するAlGaAs層からなるショットキー層18、n型不純物を含有するInxGa(1-x)As層からなるコンタクト層20a、20bを積層したHEMT構造を有し、チャネル層のxを0.3≦x≦0.35とし、コンタクト層のxを0.55≦x≦0.60としたものである。

(もっと読む)

半導体装置

【課題】本発明は、外部ノイズ等の過大電流に起因するHEMTの損傷、破壊若しくは発火を防止することができる半導体装置を提供する。

【解決手段】半導体装置1は、第1の半導体層31と、第2の半導体層32と、二次元キャリアガス層33と、ソース電極41と、ドレイン電極42と、ゲート電極5と、二次元キャリアガス層33上においてゲート電極5とドレイン電極42との間に配設された補助電極6と、を備え、二次元キャリアガス層33のゲート電極5とソース電極6との間のチャネル抵抗R1に比べて、二次元キャリアガス層33のゲート電極5と補助電極6との間のチャネル抵抗R2が高く設定されている。

(もっと読む)

半導体装置

【課題】円弧状の部分を有する電極と先端部分を有する電極での円弧状の部分と先端部分との間で流れる電流密度を均一化するために、電極の先端部分における電流集中を緩和させ、電流集中に起因する半導体装置の破壊を防止できる半導体装置を提供する。

【解決手段】半導体装置は、基板と、基板上に形成され、かつヘテロ接合に基づくキャリア走行層を有する化合物半導体層と、化合物半導体層上に形成される第1の主電極14と、化合物半導体層上において平面的に見て第1の主電極14を包囲するように形成され、かつ直線領域と円弧領域とを有する第2の主電極15と、化合物半導体層上において第1の主電極及び第2の主電極に対向するように形成された制御電極16と、を備え、第1の主電極及び第2の主電極の間に電流が流れる半導体装置であって、第1の主電極と第2の主電極の円弧領域との間に電流制限部19を設けた。

(もっと読む)

III族窒化物半導体電子デバイス、III族窒化物半導体電子デバイスを作製する方法

【課題】Id―max特性低下を低減可能なIII族窒化物半導体電子デバイスが提供される。

【解決手段】III族窒化物半導体電子デバイス11では、チャネル層21はAlGaNからなると共に、バリア層23はチャネル層21より大きなバンドギャップのAlGaNからなる。チャネル層21が、GaNではなく、AlGaNからなるので、III族窒化物半導体電子デバイス11においてId―max特性低下を低減可能である。また、第1及び第2の電極17、19は、それぞれ、チャネル層21の第1及び第2の部分21a、21b上に設けられる。チャネル層21において第1の部分21aの不純物濃度が第2の部分21bの不純物濃度と同じであるから、チャネル層21における第1の部分にイオン注入が行われていない。半導体積層15に部分的にイオン注入を行っていない。このイオン注入の使用回避により、Id―max特性低下を更に低減可能である。

(もっと読む)

1 - 20 / 60

[ Back to top ]