Fターム[5F102GT06]の内容

接合型電界効果トランジスタ (42,929) | ショットキ接触材料(ゲート電極最下層)(M) (2,043) | ナイトライド (125)

Fターム[5F102GT06]に分類される特許

1 - 20 / 125

電界効果トランジスタ

ヘテロ接合電界効果型トランジスタおよびその製造方法

電界効果トランジスタ

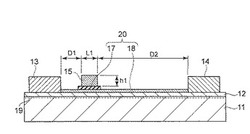

【課題】耐圧および電流コラプス抑制性能をさらに向上できる電界効果トランジスタを提供する。

【解決手段】この電界効果トランジスタによれば、ゲート絶縁膜20を、ストイキオメトリなシリコン窒化膜よりもシリコンの比率が高いシリコン窒化膜で作製されたコラプス抑制膜18と上記コラプス抑制膜18上に形成されたSiO2絶縁膜17とを有する複層構造とすることにより、耐圧を向上できるだけでなく、電流コラプスも抑制できる。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】耐圧を向上できる電界効果トランジスタを提供する。

【解決手段】GaN系HFETは、ゲート絶縁膜17をなす半絶縁膜の抵抗率ρが、電流密度が6.25×10−4(A/cm2)であるとき、3.9×109Ωcmであった。抵抗率ρ=3.9×109Ωcmの半絶縁膜によるゲート絶縁膜15を備えたことで、1000Vの耐圧が得られた。ゲート絶縁膜の抵抗率が、1×1011Ωcmを超えると耐圧が急減し、ゲート絶縁膜の抵抗率が、1×107Ωcmを下回るとゲートリーク電流が増大する。

(もっと読む)

半導体装置

【課題】複数のチャネルを有する窒化物半導体装置において、ノーマリオフかつ低オン抵抗を実現する技術を提供する。

【解決手段】第1の窒化物半導体層3,5,7と、第1の窒化物半導体層よりも禁制帯幅が大きい第2の窒化物半導体層5,6,8とが積層されたヘテロ接合体を少なくとも2つ以上有する窒化物半導体積層体10を備え、窒化物半導体積層体10に設けられたドレイン電極14と、ソース電極13と、ドレイン電極14とソース電極13の両者に対向して設けられたゲート電極15,16とを有し、ドレイン電極14とソース電極13は、窒化物半導体積層体10の表面または側面に配置され、ゲート電極15,16は、窒化物半導体積層体10の深さ方向に設けられた第1ゲート電極15と、該第1ゲート電極15と窒化物半導体積層体10の深さ方向の配置深さが異なる第2ゲート電極16とを有する。

(もっと読む)

半導体装置の製造方法

【課題】GaN系半導体を用い耐圧の異なるトランジスタを作り分ける。

【解決手段】基板1上方に第1、第2GaN系半導体層3,4、電極層5、第1絶縁膜6を積層し、電極層5及び第1絶縁膜6をパターニングして、第1ゲート電極5と第1絶縁膜6が積層された第1構造と、第2ゲート電極5と第1絶縁膜6が積層された第2構造を形成し、第1、第2構造を覆って第2絶縁膜7を形成し、第1ゲート電極5とその両側領域を露出する第1開口8SD、第2ゲート電極5を挟んでそれぞれ一方側、他方側に配置された第2、第3開口8S,8Dを有する第1マスクを用いて、第2絶縁膜7を異方性エッチングし、第1開口内8SDにおいて、第1構造の側面上にサイドウォール絶縁膜7SWを残しつつ、第1ゲート電極を挟んでコンタクトホール9S,9Dを形成し、第2、第3開口内に、それぞれコンタクトホール9S,9Dを形成し、各コンタクトホールに電極を形成する。

(もっと読む)

しきい電圧の変動を減らした高電子移動度トランジスタ及びその製造方法

【課題】しきい電圧の変動を減らした高電子移動度トランジスタ及びその製造方法を提供する。

【解決手段】化合物半導体を含む基板上に形成され、二次元電子ガスチャネルとデプリーション領域とを備えるチャネル層と、二次元電子ガスチャネルに対応するように、チャネル層上に形成された第1チャネル供給層と、チャネル層のデプリーション領域及び第1チャネル供給層の一部の領域上に形成されたデプリーション層と、第1チャネル供給層上に形成され、デプリーション領域を挟んで対向するソース及びドレイン電極と、デプリーション層上に形成されたゲート電極と、を備え、第1チャネル供給層より分極率が小さい第2チャネル供給層を、チャネル層のデプリーション領域及び第1チャネル供給層の一部の領域上に備え、デプリーション層が第2チャネル供給層上に備えられる、高電子移動度トランジスタである。

(もっと読む)

高電子移動度トランジスタ

【課題】電子移動度を低下させることなく、電子密度を高くできる高電子移動度トランジスタを提供する。

【解決手段】Si基板100上に形成されたバッファ層10と、バッファ層10上に形成されたGaN層11と、GaN層11上に形成されたAlGaN層12と、AlGaN層12内に形成されると共に、互いに間隔をあけて形成されたソース電極13とドレイン電極14と、AlGaN層12上かつソース電極13とドレイン電極14との間に形成されたゲート電極15と、ソース電極13とドレイン電極14およびゲート電極15が形成されたAlGaN層12の一部を覆うように形成された絶縁膜16とを備える。上記絶縁膜16中にCsの原子が2×1013cm−2以上存在する。

(もっと読む)

窒化物半導体装置およびその製造方法

【課題】窒化物半導体層とオーミック電極とのコンタクト抵抗を低減できる窒化物半導体装置を提供する。

【解決手段】Si基板10上に形成されたアンドープGaN層1,アンドープAlGaN層2と、アンドープGaN層1,アンドープAlGaN層2上に形成されたTi/Al/TiNからなるオーミック電極(ソース電極11,ドレイン電極12)とを備える。上記オーミック電極中の窒素濃度を1×1016cm−3以上かつ1×1020cm−3以下とする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】窒化物半導体層をチャネルとして用いたトランジスタにおいて、オン抵抗を低くしつつ、閾値電圧を高くする。

【解決手段】キャップ層400と障壁層300の界面、及びチャネル層200とバッファ層100の界面には圧縮歪が生じており、障壁層300とチャネル層200の界面には引張り歪が生じている。このため、キャップ層400と障壁層300の界面、並びにチャネル層200とバッファ層100の界面において、負の電荷が正の電荷よりも多くなっており、障壁層300とチャネル層200の界面において、正の電荷が負の電荷よりも多くなっている。チャネル層200は、第1層、第2層、及び第3層の積層構造を有している。第2層は、第1層及び第3層よりも電子親和力が大きい。

(もっと読む)

支持されたゲート電極を備えるトランジスタの作製方法およびそれに関連するデバイス

【課題】貫通する開口を備える保護層を基板上に形成し、さらにこの開口の中にゲート電極を形成することによって、トランジスタを作製する。

【解決手段】ゲート電極の第1の部分は、開口の外側に存在する保護層の表面部分で横方向に延在し、ゲート電極の第2の部分は、保護層から間隔を空けて配置され、第1の部分を越えて横方向に延在する。関連したデバイスおよび作製方法も述べられる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置について、小型化を図りつつ、ドレイン耐圧を向上する。

【解決手段】ゲート電極20と、ゲート電極20と離間するソース電極24と、平面視でゲート電極20からみてソース電極24の反対側に位置し、かつゲート電極20と離間するドレイン電極22と、平面視でゲート電極20とドレイン電極22の間に位置し、絶縁膜26を介して半導体基板10上に設けられ、かつゲート電極20、ソース電極24およびドレイン電極22と離間する少なくとも一つのフィールドプレート電極30と、絶縁膜26中に設けられ、かつフィールドプレート電極30と半導体基板10を接続する少なくとも一つのフィールドプレートコンタクト40と、を備え、平面視でフィールドプレート電極30は、フィールドプレートコンタクト40からソース電極24側またはドレイン電極22側の少なくとも一方に延伸している。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極に臨む領域の半導体層へのダメージ層の形成を抑制して、ノーマリオフ動作を実現することができるヘテロ接合電界効果型トランジスタを備える半導体装置およびその製造方法を提供する。

【解決手段】チャネル層23とヘテロ接合を形成するバリア層24のうち、ゲート電極29に臨む領域を除く他の領域に、バリア層24の伝導帯から、チャネル層23とバリア層24とのヘテロ界面のバンド不連続量ΔEcと、バリア層24に発生する分極によるバリア層24のゲート電極29側とヘテロ界面側とのエネルギー差ΔEpとを足し合わせたエネルギー(ΔEc+ΔEp)までのエネルギー深さのバンドギャップ中に準位を形成する不純物をドーピングして、不純物ドーピング領域26を形成する。

(もっと読む)

電界効果トランジスタ

【課題】ゲート電極とソース電極との間に印加される電圧がソース電極パッドの電気抵抗による電圧降下で低下することを防止でき、安定した動作を実現できる電界効果トランジスタを提供する。

【解決手段】このGaN HFETによれば、ボンディング部16Bの第2のパッド部16B‐2は、電極接続部16Aが含有する複数の接続部分19のうちの第2の方向(ソース電極12とドレイン電極11が対向している方向)の一端に配置された接続部分19の上記第2の方向の外端を電極延在方向へ延長した仮想延長線L1に関して第1のパッド部16B‐1とは反対側に位置している。第2のパッド部16B‐2に接続された第2のソース配線24のボンディング箇所の第2の方向の位置を電極接続部16Aのソース電極12との接続部分19の第2の方向の位置と重ならないようにして、ソース電極12からの電流が第2のソース配線24に流れにくくできる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】窒化物半導体層をチャネルとして用いたトランジスタにおいて、閾値電圧を高くする。

【解決手段】第2窒化物半導体層200は、Alの組成比が互いに異なる複数の窒化物半導体層を順次積層した構造を有するため、Al組成が階段状に変化している。第2窒化物半導体層200を形成する複数の半導体層は、それぞれが同一方向に分極している。そしてゲート電極420に近い半導体層は、ゲート電極420から遠い半導体層よりも、分極の強度が強く(又は弱く)なっている。すなわち複数の半導体層は、ゲート電極420に近づくにつれて、分極の強度が一方向に変化している。この分極の方向は、複数の半導体層内の界面において負の電荷が正の電荷よりも多くなる方向である。

(もっと読む)

GaN系化合物半導体装置

【課題】ゲート電極へのリーク電流を大幅に低減できるGaN系化合物半導体装置を提供する。

【解決手段】このGaN系HFETによれば、ゲート電極をなすTiN膜の抵抗率(Ω・μm)を24.7(Ω・μm)とした。このように、ゲート電極のショットキー電極層としてのTiN膜の抵抗率が10Ωμm以上であることによって、ゲート電極をなす金属材料TiNの抵抗率(ゲートメタル抵抗率)が10Ωμm未満である場合に比べて、ゲートリーク電流を著しく低減できる。

(もっと読む)

高電子移動度トランジスタ及びその製造方法

【課題】高電子移動度トランジスタ及びその製造方法を提供する。

【解決手段】基板と、基板上に形成されたHEMT積層物と、を備え、HEMT積層物は、2DEGを含む化合物半導体層と、化合物半導体層より分極率の大きい上部化合物半導体層と、上部化合物半導体層上に備えられたソース電極、ドレイン電極及びゲートと、を備え、基板は、シリコン基板より誘電率及び熱伝導度の高い窒化物基板であるHEMT。該基板は、シリコン基板より誘電率及び熱伝導度の高い絶縁層、この絶縁層に蒸着された金属層及びこの金属層に付着されたプレートを備える。

(もっと読む)

GaN系半導体素子の製造方法

【課題】電極メタルがSiN絶縁膜に拡散することを抑制でき、電流コラプスの抑制とリーク電流の低減とを両立できるGaN系半導体素子の製造方法を提供する。

【解決手段】このGaN系HFETの製造方法によれば、GaN系積層体5上に形成したSiN保護膜7を熱処理により改質してから、Ti/Al電極15,16をGaN系積層体5上に形成し、Ti/Al電極15,16を熱処理してオーミック電極としてのソース電極15,ドレイン電極16とする。SiN保護膜7を熱処理した後に、Ti/Al電極15,16を熱処理(オーミックアニール)し、オーミック電極としてソース電極15,ドレイン電極16を形成することによって、電極メタルがSiN保護膜7に拡散することを抑制できる。

(もっと読む)

電界効果トランジスタ

【課題】動的な耐圧であるダイナミック耐圧の低下を抑制できるGaN系のHFETを提供する。

【解決手段】このGaN系のHFETでは、各ソース電極12の長手方向の長さL2が各ドレイン電極11の長手方向の長さL1よりも短く、ソース電極12の長手方向の両端12A,12Bがドレイン電極11の長手方向の両端11A,11Bよりも長手方向外方へ突出していない構成により、ソース電極12の端12A,12Bからドレイン電極11の端11A,11Bへ向かって電子流が集中することを回避できる。

(もっと読む)

HEMT装置を製造するCMOSコンパチブルな方法とそのHEMT装置

【課題】Si−CMOSプロセス時術とコンパチブルなHEMT装置の製造法を提供する。

【解決手段】基板101を提供するステップと、III族窒化物層のスタックを基板上に形成するステップと、窒化シリコンからなり、スタックの上方層に対して上に位置すると共に当接する第1パッシベーション層301を形成し、第1パッシベーション層が、現場でスタックに堆積されるステップと、第1パッシベーション層に対して上に位置すると共に当接する誘電体層を形成するステップと、窒化シリコンからなり、誘電体層に対して上に位置すると共に当接する第2パッシベーション層303を形成し、第2パッシベーション層が、LPCVD、MOCVD又は同等の手法によって450℃より高い温度で堆積されるステップと、ソースドレイン・オーミック接触とゲート電極601を形成するステップとを備える。

(もっと読む)

1 - 20 / 125

[ Back to top ]