Fターム[5F102GV09]の内容

接合型電界効果トランジスタ (42,929) | その他の構造 (2,409) | 表面保護膜を形成したもの (2,097) | ネイティブオキサイド(表面酸化膜) (143)

Fターム[5F102GV09]に分類される特許

81 - 100 / 143

半導体装置およびその製造方法

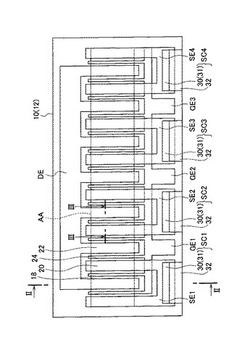

【課題】ソース抵抗を低減できる半導体装置およびその製造方法を提供する。

【解決手段】

基板10上に配置された窒化物系化合物半導体層12と、窒化物系化合物半導体層12上に配置され、アルミニウム窒化ガリウム層18からなる活性領域AAと、活性領域上に配置されたゲート電極24、ソース電極20およびドレイン電極22と、ゲート電極、ソース電極およびドレイン電極が延伸する方向の窒化物系化合物半導体層上に配置され、それぞれゲート電極、ソース電極およびドレイン電極に接続されたゲート端子電極GE1〜GE3、ソース端子電極SE1〜SE4およびドレイン端子電極DEと、ソース端子電極が配置される側の基板の端面に配置され、ソース端子電極と接続され、最外層のエッジが下地金属層よりも後退する3層以上の異なる多層金属を有する端面電極SC1〜SC4とを備え、ダイボンディング半田層がソース端子電極に到達するのを防止する。

(もっと読む)

半導体装置及びその製造方法

【課題】GaN/AlGaN−HEMTをE−mode動作させるに当たり、Vf及び最大ドレイン電流を向上させ、かつ良好なゲート−ドレイン間耐圧を有し、さらに、ゲートリーク電流を抑制する。

【解決手段】基板15と、この基板上に形成されており、GaN層17及びAlGaN層19が順次積層されてなる積層構造体21とを含む下地13と、AlGaN層に開口形成されているゲート形成用凹部27と、このゲート形成用凹部の内側底面27a、ゲート形成用凹部の内側壁面27b、及びゲート形成用凹部外の下地面13aを一体的に被覆して形成されているSiN膜29と、SiN膜の表面を被覆して形成されているアモルファスAlN膜31と、SiN膜及びアモルファスAlN膜が形成されているゲート形成用凹部を埋め込むゲート電極33とを具える。

(もっと読む)

逆拡散抑制構造

エンハンスメントモードGaNトランジスタが提供される。当該トランジスタは、基板と、遷移層と、III族窒化物材料を有するバッファ層と、III族窒化物材料を有するバリア層と、ドレイン及びソースのコンタクトと、アクセプタ型ドーパント元素を含有するゲートと、前記ゲートと前記バッファ層との間の、III族窒化物材料を有する拡散バリアとを有する。  (もっと読む)

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲート電極が微細化されても電流コラプスを抑制することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】表面保護膜10を形成する際に、化合物半導体積層構造上に第1の絶縁膜10aを形成し、第1の絶縁膜10aの表面に、酸素原子又は窒素原子の少なくとも一方を第1の絶縁膜10aよりも多く含む第2の絶縁膜10bを形成し、第2の絶縁膜10bの上方に、第1の絶縁膜10aよりもSi−H結合を少なく含み、第1の絶縁膜10aよりも高い絶縁性を示す第3の絶縁膜10cを形成する。

(もっと読む)

GaN系電界効果トランジスタの製造方法

【課題】低抵抗・高耐圧で電流コラプス現象の影響の小さいGaN系電界効果トランジスタの製造方法を提供する。

【解決手段】 GaN系電界効果トランジスタの製造方法は、基板101上にAlN層102、バッファ層103、チャネル層104、ドリフト層105および電子供給層106をエピタキシャル成長させる工程と、リセス部108を形成する工程と、アロイ工程におけるアニール時に電子供給層106を保護する保護膜113を、リセス部108の内表面、電子供給層106、ソース電極109、ドレイン電極110および素子分離部分130上に形成する工程と、オーミック接触を得るためのアニールを行なうアロイ工程と、保護膜113を除去し、ゲート絶縁膜を、リセス部108の内表面、電子供給層106、ソース電極109、ドレイン電極110および素子分離部分130上に形成する工程と、リセス部108のゲート絶縁膜上にゲート電極を形成する工程とを備える。

(もっと読む)

半導体装置

【課題】電力密度の集中を抑制して発熱の分散を図り、かつ電気位相差を低減した高性能な半導体装置を提供する。

【解決手段】基板上に配置された窒化物系化合物半導体層と、窒化物系化合物半導体層上に配置され、アルミニウム窒化ガリウム層(AlxGa1-xN)(0.1≦x≦1)からなる活性領域と、活性領域を互いに素子分離する素子分離領域と、素子分離領域によって囲まれた活性領域上に配置されたゲート電極24、ソース電極20およびドレイン電極22と、素子分離領域14上に配置され、それぞれゲート電極24,ソース電極20およびドレイン電極22に接続されたゲート端子電極240,ソース端子電極200およびドレイン端子電極220とを備え、ゲート電極24の分岐を再帰的な自己相似のフラクタル図形で構成する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】高い信頼性を得ることができる化合物半導体装置及びその製造方法を提供する。

【解決手段】基板1上に形成されたi−GaN層2(キャリア走行層)と、i−GaN層2上に形成されたn−AlGaN層4(キャリア供給層)と、が設けられている。また、n−AlGaN層4上に形成されたTa膜11s及び11dと、夫々Ta膜11s及び11d上に形成されたAl膜12s及び12dと、が設けられている。更に、夫々Ta膜11s及び11dにAl膜12s及び12dを介さずに電気的に接続されたAu膜14s及び14dと、n−AlGaN層4上においてTa膜11s及び11dの間に位置するゲート電極13gと、が設けられている。

(もっと読む)

GaN系電界効果トランジスタおよびその製造方法

【課題】低抵抗・高耐圧で電流コラプス現象の影響の小さいGaN系電界効果トランジスタおよびその製造方法を提供する。

【解決手段】GaN系電界効果トランジスタ100は、基板101と、基板の上に形成されたp型GaN系半導体材料からなるチャネル層104と、チャネル層上に形成され、チャネル層よりもバンドギャップエネルギーが大きいGaN系半導体材料からなる電子供給層106と、電子供給層の一部が除去されて表出したチャネル層104の表面に形成されたゲート絶縁膜111と、ゲート絶縁膜上に形成されたゲート電極112と、ゲート電極を挟んで形成されたソース電極109及びドレイン電極110と、電子供給層106上に形成されたゲート絶縁膜111とは別の絶縁膜であって、電流コラプス低減効果のある第2の絶縁膜113と、を備える。

(もっと読む)

エピタキシャル基板、エピタキシャル基板の製造方法、及び、半導体装置の製造方法

【課題】エピタキシャル基板の経時変化を抑制し、この経時変化により半導体装置の特性を低下することがない、エピタキシャル基板、その製造方法、及び、半導体装置の製造方法を提供する。

【解決手段】基板の上に、III族元素と少なくとも窒素を含むV族元素で構成されたIII−V族窒化物半導体層からなり、半導体装置を構成するための半導体機能層を形成する工程と、半導体機能層の上に、半導体機能層より低い成長温度で形成され、アルミニウムを除くIII族元素と少なくとも窒素を含むV族元素で構成されたIII−V族窒化物半導体層からなり、半導体機能層を保護する半導体保護層を形成する工程とによりエピタキシャル基板を製造する。そして、エピタキシャル基板の半導体保護層を、窒化物半導体機能層に対するエッチングレートの差により選択的に除去する工程により半導体装置を製造する。

(もっと読む)

電界効果トランジスタ

【課題】低オン抵抗のFETを提供する。

【解決手段】本発明のFETは、第1の窒化物半導体層103と、第1の窒化物半導体層103の上に形成され、第1の窒化物半導体層103よりもバンドギャップエネルギーが大きい第2の窒化物半導体層104と、第2の窒化物半導体層104の上に形成された第3の窒化物半導体層105と、第3の窒化物半導体層105の上に形成され、第3の窒化物半導体層105よりもバンドギャップエネルギーが大きい第4の窒化物半導体層106とを備え、第1の窒化物半導体層103及び第2の窒化物半導体層104のヘテロ接合界面には、チャネルが形成される。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】耐圧特性の向上とオン抵抗の低減とが可能な半導体装置および半導体装置の製造方法を提供する。

【解決手段】MIS型HEMT1は、支持基板10上に形成されたIII族窒化物半導体よりなるキャリア走行層12と、キャリア走行層12上に形成されたIII族窒化物半導体よりなるキャリア供給層13と、キャリア供給層13上に形成されたソース電極22sおよびドレイン電極22dと、キャリア供給層13上に形成された絶縁膜(14、15)と、絶縁膜(14、15)上に形成されたゲート電極21と、を備え、絶縁膜(14、15)は、ソース電極22sとドレイン電極22dとで挟まれた領域に形成され、溝t15の断面形状は、上部開口が底面よりも幅広な断面形状が逆台形状の部分を有しており、ゲート電極21は、少なくとも溝t15の底面からドレイン電極22d側の絶縁膜(14、15)上にかけて形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】 窒化アルミニウムあるいは窒化アルミニウムガリウムを含む窒化物半導体層を用い、緩やかに傾斜したフィールドプレートの形成が容易に形成ができ、電界集中を緩和して高耐圧化が実現できる窒化物半導体装置及びその製造方法を提供する。

【解決手段】 窒化アルミニウムあるいは窒化アルミニウムガリウムを含む窒化物半導体層に形成した側壁が斜めに傾斜した凹部内に、ゲート電極を形成する。側壁が斜めの凹部は、アルミニウムを含む窒化物半導体層の結晶性を劣化させながら成長させ、その後、結晶性の違いに応じてエッチングレートが異なるエッチング液を使用してエッチングして形成する。あるいはアルミニウムの組成比を変化させて形成することも可能である。

(もっと読む)

半導体積層体を含む半導体装置の製造方法

【課題】 半導体下層と半導体上層が積層された半導体積層体において、半導体下層の表面に損傷を与えることなく、半導体下層の一部を露出させる技術を提供する

【解決手段】 半導体下層18の表面の一部に、半導体上層15とは格子定数の異なる格子不整合層30を形成する工程と、格子不整合層30の表面と格子不整合層30で被覆されていない半導体下層18の表面に、半導体上層15を結晶成長させる工程と、格子不整合層30上の半導体上層15に形成された転位40を介してウェットエッチング液を導入し、格子不整合層30とその格子不整合層30上の半導体上層15を除去して半導体下層18の一部を露出させる工程を備える。ドライエッチングにより半導体下層18に損傷を与えることなく、半導体下層18の一部を露出させることができる。

(もっと読む)

窒化物半導体装置およびその製造方法

【課題】応答特性が良く電流コラプスの問題を改善できると同時に、デバイス設計値どおりのゲートリセス部を再現性よく形成しうる窒化物半導体装置を得ること。

【解決手段】基板1上に形成された第1の窒化物半導体からなるチャネル層2と、チャネル層2の上部に形成され、第1の窒化物半導体よりも大きなバンドギャップを有する第2の窒化物半導体からなる第1の電子供給層3aと、第1の電子供給層の上部で離隔した2つの領域として形成され、第1の窒化物半導体と同じか、又はこれよりも大きなバンドギャップを有する第3の窒化物半導体からなる第2の電子供給層3bとを備えている。

第1と第2の電子供給層3a、3bの間には、第2の電子供給層3bよりもドライエッチング速度が小さい材料からなるエッチングストッパ層4が形成されており、この層4の上部で2つの領域に挟まれたゲートリセス部を、ゲート電極5が充填するように形成されている。

(もっと読む)

化合物半導体装置およびその製造方法

【課題】本発明は、RFデバイスの低抵抗化による高効率化を図り、高い生産性を得ることが可能な化合物半導体装置とその製造方法を提供する。

【解決手段】GaN層11上にAlGaN層12が形成されたAlGaN/GaN基板と、それぞれGaN層11とAlGaN層12の界面に形成される二次元キャリア層13を貫通してGaN層に到達し、その側面とAlGaN/GaN基板の基板面との角度が90±10°となる開口部に形成されるメタル層からなるソース電極14およびドレイン電極15とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】ノーマリオフとなり、かつリーク電流の発生を抑制できる半導体装置を提供することである。

【解決手段】半導体装置10は、基板17上に電子走行層16をエピタキシャル成長により形成し、さらに電子走行層16上に電子供給層12をエピタキシャル成長により形成する。電子走行層16と電子供給層12とはヘテロ接合構造とし、接合界面に二次元電子ガスチャネル13を形成可能とする。電子供給層12上は絶縁膜11で覆う。電子供給層12は、Al組成比率を10〜18[%]とし、膜厚を5〜15[nm]として形成する。絶縁膜11は700℃前後の低温下で成長させて形成する。作製された半導体装置10は、クラック等の発生が防止され、ノーマリオフになる。また、700℃前後の低温下で絶縁膜11を形成するので、リーク電流の発生を抑制することができる。

(もっと読む)

トランジスタ

【課題】トラッピングを少なくするためにAlGaN層を薄くし、またゲート漏洩を減少させるために層を追加して最大駆動電流を増加させるようにする。

【解決手段】高比抵抗半導体層20と、この高比抵抗半導体層20上に設けられたバリア半導体層18と、このバリア半導体層18に接触するするとともに、バリア半導体層18の表面部を被覆していないソースおよびドレインコンタクト13,14と、バリア半導体層18の被覆されていない表面上に設けられた絶縁層24と、この絶縁層24上に設けられ、ゲート漏洩のバリアを形成するゲートコンタクト16とを備えている。

(もっと読む)

半導体装置およびその製造方法

【課題】電子供給層について膜厚とAl組成比率の最適化を図り、ノーマリオフとなる半導体装置を提供することである。

【解決手段】半導体装置10は、基板18上に電子走行層17をエピタキシャル成長により形成し、さらに電子走行層17上に電子供給層15をエピタキシャル成長により形成する。電子走行層17と電子供給層15とはヘテロ接合構造とし、接合界面に二次元電子ガスチャネル16を形成可能なHEMTとする。電子供給層15上は絶縁膜14で覆い、ソース電極11,ゲート電極12およびドレイン電極13を設ける。電子供給層15は、Al組成比率を10〜18[%]とし、膜厚を5〜15[nm]として形成する。作製された半導体装置10は、クラック等の発生が防止され、ノーマリオフになる。よって、この半導体装置10はパワーデバイスとして利用することができる。

(もっと読む)

GaN系電界効果トランジスタ及びその製造方法

【課題】 オーミックコンタクト抵抗やシート抵抗を低減した,電界効果トランジスタ及びその簡易な製造方法を提供する。

【解決手段】 障壁層を有する電界効果トランジスタであって,前記電界効果トランジスタは,障壁層表面に,シリコンなどの堆積物層を有する,トランジスタにより解決される。この堆積物層により,オーミックコンタクト抵抗やシート抵抗を低減できる。また,シリコンなどは容易に堆積させることができるので,特性に優れた電界効果トランジスタを簡易に製造できることとなる。

(もっと読む)

GaN系半導体素子

【課題】小さいオン抵抗を維持しながら閾値を確実にプラスに引き上げ、実効的にノーマ

リオフになるGaN系半導体素子を提供する。

【解決手段】電界効果トランジスタ20では、サファイア基板1上に、バッファ層2と、チャネル層(アンドープGaN層)3と、電子供給層(アンドープAlGaN層)4とを順に積層している。電子供給層4上のソース部分にnpn積層構造9が形成され、積層構造9上にソース電極Sが形成されている。電子供給層4のドレイン部分にドレイン電極Dが形成され、そのゲート部分に形成された開口部11に絶縁膜8が形成されている。ゲート電極Gに順方向に閾値以上の電圧を印加すると、反転層Aと反転層Bが形成されてドレイン電流が流れる。p型(In)GaN層6の厚さやその不純物濃度を変えることで、閾値電圧を制御することができる。ドリフト層12によりゲート電極Gとドレイン電極D間の電界集中が緩和され、耐圧が向上する。

(もっと読む)

81 - 100 / 143

[ Back to top ]