Fターム[5F102GV09]の内容

接合型電界効果トランジスタ (42,929) | その他の構造 (2,409) | 表面保護膜を形成したもの (2,097) | ネイティブオキサイド(表面酸化膜) (143)

Fターム[5F102GV09]に分類される特許

121 - 140 / 143

AlGaN/GaNHEMTの表面処理およびパッシベーション

好適に具体例では、ゲートリークと散乱を低減した、薄いその場SiN層により覆われたIII族窒化物電界効果デバイスが提供される。これは、ゲート堆積の前と、第2パッシベーション層の堆積前の、その場SiNの洗浄と組み合わせて、その場SiN層の上に第2のパッシベーション層を導入して得られる。  (もっと読む)

(もっと読む)

半導体装置

【課題】半導体装置の表面からの放熱性を向上し、高出力動作を実現できるようにする。

【解決手段】半導体装置は、障壁層104の上に該障壁層104と接して形成されたソース電極105、ドレイン電極及びゲート電極107と、障壁層104の上に各電極の上面の少なくとも一部を覆うように形成され、障壁層104を保護する、複数の膜からなるパッシべーション膜108とを有している。パッシベーション膜108は、少なくとも窒化アルミニウムからなる膜を含む。

(もっと読む)

窒化物半導体トランジスタ及びその製造方法

【課題】動作電流が大きく且つスイッチング特性に優れたノーマリオフ型の窒化物半導体トランジスタを実現できるようにする。

【解決手段】窒化物半導体トランジスタは、第1の窒化物半導体層13と、第1の窒化物半導体層13の上に形成され、第1の窒化物半導体層13と比べてバンドギャップが大きい第2の窒化物半導体層14と、第2の窒化物半導体層14の上に形成された第3の窒化物半導体層15とを備えている。第3の窒化物半導体層15におけるゲート電極20の下側の領域には、p型の導電性を有するコントロール領域15aが形成され、第3の窒化物半導体層におけるゲート電極15とソース電極18及びドレイン電極19との間の領域には、コントロール領域15aよりも抵抗値が高い高抵抗領域15bが形成されている。

(もっと読む)

半導体エピタキシャル結晶基板の製造方法

【課題】高性能の窒化ガリウム系トランジスタを製造するための、誘電体膜付の半導体エピタキシャル結晶基板を提供すること。

【解決手段】下地基板1上にエピタキシャル法によって、バッファ層2、チャネル層3、及び電子供給層4から成る窒化ガリウム半導体結晶層を形成した後、エピタキシャル成長炉内で連続してAlNを電子供給層4上に誘電体膜の前駆体として積層し、しかる後、積層した前駆体に対して酸化処理を施すことによって誘電体膜5を形成する。

(もっと読む)

窒化物半導体発光素子、窒化物半導体発光素子の製造方法および窒化物半導体トランジスタ素子

【課題】高温かつ高出力の駆動においても十分な信頼性を得ることができる窒化物半導体発光素子およびその窒化物半導体発光素子を製造するための窒化物半導体発光素子の製造方法、ならびに信頼性を向上することができる窒化物半導体トランジスタ素子を提供する。

【解決手段】光出射部にコート膜が形成されており、コート膜はアルミニウムの窒化物結晶またはアルミニウムの酸窒化物結晶を含む窒化物半導体発光素子と、その窒化物半導体発光素子の製造方法である。また、窒化物半導体層と窒化物半導体層に接するゲート絶縁膜とを含み、ゲート絶縁膜がアルミニウムの窒化物結晶またはアルミニウムの酸窒化物結晶を含む窒化物半導体トランジスタ素子である。

(もっと読む)

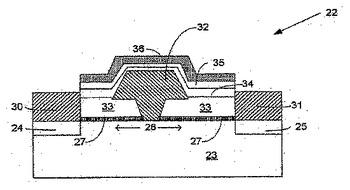

支持されたゲート電極を備えるトランジスタの作製方法およびそれに関連するデバイス

貫通する開口を備える保護層を基板上に形成し、さらにこの開口の中にゲート電極を形成することによって、トランジスタは作製される。ゲート電極の第1の部分は、開口の外側に存在する保護層の表面部分で横方向に延在し、ゲート電極の第2の部分は、保護層から間隔を空けて配置され、第1の部分を越えて横方向に延在する。関連したデバイスおよび作製方法も述べられる。  (もっと読む)

(もっと読む)

III族窒化物半導体基板

【課題】III族窒化物半導体系HJFETを作製する際、ゲート電極を形成する電子供給層の表面を清浄状態に保つこと、同時に、ゲート電極とドレイン電極間に存在する電子供給層の表面を被覆する表面保護膜との界面の状態を制御することに有効な構造を持つIII族窒化物半導体基板の提供。

【解決手段】III族窒化物半導体系HJFETに利用される、ヘテロ接合を含むIII族窒化物半導体層構造の形成後、大気に曝すことなく、引き続き、表面保護膜として利用可能な窒化物の絶縁膜を形成し、

この窒化物の絶縁膜とIII族窒化物半導体層構造との界面における不純物濃度を、1×1017 atoms/cm3以下に抑えているIII族窒化物半導体基板とする。

(もっと読む)

III族窒化物半導体素子の製造

電源電極を受け入れる部分の上に保護本体を設ける間に、ゲート構造を形成する工程を有する、III族窒化物電力半導体素子を製造する方法。 (もっと読む)

窒化物系半導体装置

【課題】閾値電圧を容易に制御することができるとともに低いオン抵抗を有する窒化物系半導体装置を歩留まりよく提供すること。

【解決手段】ノンドープのAlXGa1-XN(0≦X<1)からなるキャリア走行層1と、キャリア走行層1よりも格子定数の小さいノンドープまたはn型のAlYGa1-YN(0<Y≦1、X<Y)からなる障壁層2と、キャリア走行層1と格子定数の等しいノンドープの半導体からなる閾値制御層3と、キャリア走行層1よりも格子定数の小さいノンドープまたはn型の半導体からなるキャリア誘起層4とが順に積層され、ゲート電極形成領域におけるキャリア誘起層4の全部またはキャリア誘起層4の全部と閾値制御層3の一部を除去したリセス構造30中に形成したゲート電極5と、ゲート電極5を挟んだ障壁層2、閾値制御層3およびキャリア誘起層4のいずれかに形成されるソース電極6およびドレイン電極7と、を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】 T字型電極を有する半導体装置において、隣接ゲート間の素子容量を低減させる。

【解決手段】 半導体基板1の上に活性層2が設けられ、その表面にリセス溝3が形成されている。リセス溝3の底面上に、T字型のAl電極4が設けられている。Al電極4の支持部分に接触するように、ライナー膜として、第1絶縁膜5が設けられている。この膜として、多孔質系の有機膜、または有機系の高分子材料、またはボラジン系の高分子材料からなる低誘電率膜を用いるようにした。

上記構造とすることにより、隣接するゲート間の素子容量を低減させ、ばらつきを抑えることができる。

(もっと読む)

ヘテロ構造電界効果トランジスタ用エピタキシャルウェハ、ヘテロ構造電界効果トランジスタおよびヘテロ構造電界効果トランジスタ作製法

【課題】HFET構造のデバイス作製工程におけるトランジスタ特性の劣化を抑制可能なヘテロ構造電界効果トランジスタ用エピタキシャルウェハを提供する。

【解決手段】あらかじめ定めた材質の基板1A上に、GaN緩衝層2A、アンドープAlxGa1−xN(0<x<1)第一障壁層3A,ドナードープAlxGa1−xN第二障壁層4A、アンドープAlxGa1−xN第三障壁層5Aを順次エピタキシャル成長させ、さらに、アンドープAlxGa1−xN第三障壁層5A上にAlyGa1−yN(0<y≦1)表面保護層6Aを形成する。さらに、好ましくは、アンドープAlxGa1−xN第三障壁層5AのAlN組成yは、0.7≦y≦1の範囲であり、その膜厚は、0.3nmから5nmまでの範囲とする。

(もっと読む)

半導体素子の製造方法及び半導体素子

【課題】GaN系高移動度トランジスタの電流コラプスを低減する。

【解決手段】先ず、下地基板10上に、AlGaN/GaNのヘテロ構造層20を形成する。次に、リフトオフ法を用いて、へテロ構造層20の上側表面21上に、ゲート電極52、オーミック電極54を形成する。次に、へテロ構造層の上側表面に対してNH3プラズマ照射することにより、表面クリーニングを行う。NH3プラズマ照射に換えて、N2Oプラズマ、O2プラズマ、又はSiH4プラズマの各プラズマ照射を行っても良い。

(もっと読む)

水素のないスパッタされた窒化物を用いた、広いバンドギャップに基づいた半導体デバイスの不動態化

不動態化された半導体構造と関連する方法が開示される。該構造は、炭化珪素基板または層と、炭化珪素基板と熱酸化層との間のインターフェース密度を下げる、炭化珪素基板の上の酸化層と、寄生容量を減少し、デバイスのトラッピングを最小化する、熱酸化層の上の第1のスパッタされた非化学量論的な窒化珪素層と、構造をカプセル化することなく基板(およびその上のデバイス)からさらに遠くに次の不動態化層を配置する、該第1の層の上の第2のスパッタされた非化学量論的な窒化珪素層と、構造をカプセル化し、不動態化層の水素障壁特性を高める、第2のスパッタされた層の上のスパッタされた化学量論的な窒化珪素層と、カプセル化層の上の、ステップカバレージおよび亀裂防止のための、化学量論的な窒化珪素層の化学蒸着された環境障壁層とを含む不動態化された半導体構造である。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】半導体層の表面準位によって生じる逆方向バイアス時のリーク電流を低減する半導体装置を実現できるようにする。

【解決手段】半導体装置は、基板1の上に形成された第1の半導体層4と、第1の半導体層4の上に互いに間隔をおいて形成されたショットキー電極7及びオーミック電極8と、ショットキー電極7及びオーミック電極8を露出し且つ第1の半導体層4の上を覆うように形成された第2の半導体層5とを備えている。第2の半導体層5は、第1の半導体層4と比べてバンドギャップが大きい半導体層である。

(もっと読む)

半導体装置の製造方法

【課題】 初期特性のばらつきと通電劣化とを抑制したGaN系およびSiC系半導体装置を提供すること。

【解決手段】 プラズマエッチングに用いられるエッチングガスはマスク材13の開口部からイオン化した状態で半導体結晶12表面に入射し、所定の深さだけ半導体結晶12をエッチングする。エッチングガスに混合された窒素ガスは高いエネルギが付与されて活性化し、エッチング面および側壁面の半導体結晶12原子と反応してその結合手を窒素終端固定する。窒素終端固定された表面層の組成は、例えば、半導体結晶12がGaN系結晶の場合にはGaxNy、SiC系結晶の場合にはSixNy、となり極薄の窒化膜が形成されて化学的な安定化が図られる。このような窒素終端固定された結晶面は、デバイスに通電を行った場合にも水分や酸素による腐食(酸化)が進行せず、半導体装置の初期特性のばらつきと通電劣化とが抑制されて信頼性が向上する。

(もっと読む)

半導体装置の製造方法

【課題】AlGaN層の表面を平坦とし、かつ、AlGaN/GaN界面に存在する二次元電子ガスにダメージを与えない半導体装置の製造方法を提供する。

【解決手段】先ず、サファイア又は炭化珪素で形成される支持基板12を用意して、支持基板上にバッファ層14を堆積させる。次に、支持基板及びバッファ層を900℃以上1100℃以下に設定された成長温度に保持した状態で、バッファ層上に、GaN層16及びAlGaN層20を順次に積層してGaN半導体基板10を形成する。GaN半導体基板を形成する工程に引き続いて、GaN半導体基板を500℃以上成長温度以下の温度に保持した状態で、AlGaN層の上側表面28上に、表面保護膜としてAlN層30を形成する。

(もっと読む)

窒化物半導体装置及びその製造方法

【課題】 リーク電流を低減した窒化物半導体装置及びその製造方法を提供する。

【解決手段】 ガリウム、アルミニウム、ホウ素及びインジウムからなる群のうち少なくとも1つからなるIII族元素と、窒素、リン及び砒素からなる群のうちの少なくとも窒素を含むV族元素で構成されたIII−V族窒化物半導体層からなる窒化物半導体装置において、基板上に積層した前記III−V族窒化物半導体層からなる第1の窒化物半導体層と、該第1の窒化物半導体層の上に積層したアルミニウムを含まない前記III−V族窒化物半導体層からなり、不純物として鉄、炭素、亜鉛あるいはマグネシウムの少なくとも1つをドーピングした第2の窒化物半導体層と、該第2の窒化物半導体層にショットキ接触する制御電極とを備える。

(もっと読む)

電流検出電極を有するIII族窒化物半導体装置

【課題】電流の状態に関する情報を提供する能力を有するように配置されたIII族窒化物ベースの電力半導体装置を提供することである。

【解決手段】本発明の電力半導体装置は、III族窒化物ヘテロ接合領域と、該III族窒化物ヘテロ接合領域及び第1給電パッドに電気的に接続される第1電力電極と、前記III族窒化物ヘテロ接合領域及び第2給電パッドに電気的に接続される前記第1電力電極に対向して離隔される第2電力電極と、前記III族窒化物ヘテロ接合領域及び第3給電パッドに電気的に接続される前記第1電力電極に対向して離隔される第3電力電極と、を有する電力半導体装置。

(もっと読む)

半導体装置の製造方法

【課題】窒化物半導体装置のコンタクト抵抗並びにショットキー特性の向上を図る。

【解決手段】サファイアからなる基板11の上に、窒化アルミニウム(AlN)からなるバッファ層12と、i型GaNからなる第1の窒化物半導体層13と、i型AlGaNからなる第2の窒化物半導体層14が順次形成されている。第2の窒化物半導体層14の表面に、プラズマを電離することにより生成した窒素イオンガス18を、プラズマを発生させる陰極と被処理基板の距離を十分離して照射する。その後、ソース電極15及びドレイン電極16、ゲート電極17を形成する。この構成により、半導体表面にダメージを与えることなく、窒素空孔を含む基板表面の窒素不足を補完してから電極を作製することが可能となる。そのため、コンタクト抵抗の低減やショットキー特性の改善が実現できる。

(もっと読む)

相補型金属−酸化膜−半導体電界効果トランジスタ構造

相補型金属−酸化膜−半導体電界効果トランジスタ構造(100)はイオン注入領域(126,128)を2つの相補型素子の内の一方のみに含む。トランジスタ構造(100)は通常、化合物半導体基板(102)と、そしてエピタキシャル層構造(104)と、を含み、エピタキシャル層構造は、エピタキシャル層構造の導電型を決定する一つ以上のドナー層を含む。イオン注入領域は、これらの相補型素子の内の一方に位置するエピタキシャル層構造(104)の導電型を「反転する」または「逆にする」ように作用する。例示として実施形態では、p型アクセプターをドープしたイオン注入領域がpチャネル素子(122)において使用され、nチャネル素子(120)はイオン注入されない状態のままである。  (もっと読む)

(もっと読む)

121 - 140 / 143

[ Back to top ]