Fターム[5F102GV09]の内容

接合型電界効果トランジスタ (42,929) | その他の構造 (2,409) | 表面保護膜を形成したもの (2,097) | ネイティブオキサイド(表面酸化膜) (143)

Fターム[5F102GV09]に分類される特許

61 - 80 / 143

電界効果トランジスタ

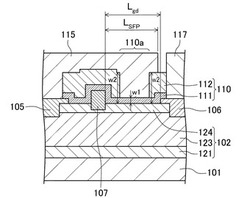

【課題】電流コラプスが小さく且つ良好な高周波特性を有する電界効果トランジスタを実現できるようにする。

【解決手段】電界効果トランジスタは、基板101の上に形成された窒化物半導体積層体102と、ソース電極105、ドレイン電極106及びゲート電極107と、窒化物半導体積層体102の上に形成された絶縁膜110と、絶縁膜110の上に接して形成され、端部がゲート電極107とドレイン電極106との間に位置するフィールドプレート115とを備えている。絶縁膜110は、第1の膜111と、第1の膜111よりも絶縁耐圧が低い第2の膜112とを含み、ゲート電極117とドレイン電極116との間に形成された薄膜部110aを有している。フィールドプレート115は、薄膜部110aを覆い且つ開口部においてソース電極と接続されている。

(もっと読む)

化合物半導体装置の製造方法及び化合物半導体装置

【課題】リフトオフ法を用いずに、簡易な手法で化合物半導体装置のゲート電極、ソース電極、及びドレイン電極を各種パターンに欠陥を生ぜしめることなく形成する。

【解決手段】AlGaN/GaN・HEMTを製造する際に、化合物半導体層上に保護絶縁膜8を形成し、保護絶縁膜8に開口を形成し、開口を埋め込む導電材料を保護絶縁膜8上に形成し、導電材料上の開口上方に相当する部位にマスクを形成し、マスクを用いて導電材料をエッチングしてゲート電極15(又はソース電極45及びドレイン46)を形成し、その後、保護絶縁膜8上に保護絶縁膜16を形成し、保護絶縁膜8,16に開口を形成し、開口を埋め込む導電材料を保護絶縁膜16上に形成し、導電材料上の開口上方に相当する部位にマスクを形成し、マスクを用いて導電材料をエッチングしてソース電極22及びドレイン23(又はゲート電極53)を形成する。

(もっと読む)

電界効果トランジスタ、電界効果トランジスタの製造方法および電子装置

【課題】ゲートリーク電流の増加が抑制された信頼性の高い電界効果トランジスタを提供する。

【解決手段】 ゲート電極は、第1金属層16および第2金属層17を含み、

第2金属層17は、第1金属層16よりも導電率が高く、

第1金属層16の上方に、第2金属層17が積層され、

ソース電極18およびドレイン電極19は、半導体層12〜14上にオーム性接触し、

ゲート電極は、ソース電極18およびドレイン電極19の間に配置され、かつ、第1金属層16により半導体層上にショットキー性接触し、

半導体層上におけるソース電極18およびゲート電極の間、ならびに、ゲート電極およびドレイン電極19の間は、絶縁膜15Aにより覆われ、

かつ、

第2金属層17下面の全体が第1金属層16上面の上方に重なっているか、または、第1金属層16の厚みが絶縁膜15Aの厚み以上であることを特徴とする電界効果トランジスタ。

(もっと読む)

III族窒化物半導体からなる半導体装置およびその製造方法、電力変換装置

【課題】主面をm面とするIII 族窒化物半導体で構成されたHFETにおいて、正のしきい値電圧を高めること。

【解決手段】HFET100は、凹凸加工されたa面サファイア基板101上に、m面を主面とするGaNからなるバッファ層102、ノンドープのGaNからなるチャネル層103、ノンドープのAlGaNからなる障壁層104、酸素ドープのn−AlGaNからなるキャリア供給層105を有している。キャリア供給層105は2つの領域に分離して形成されている。キャリア供給層105は、障壁層104上に選択的に再成長させて形成した層である。ゲート電極109にバイアスを印加しない状態では、ゲート電極109直下に2DEGが形成されないため、正のしきい値電圧を高めることができる。

(もっと読む)

電界効果トランジスタ、電界効果トランジスタの製造方法、および電子装置

【課題】 高い閾値電圧と、低いオン抵抗とを両立可能であり、かつ、パラレル伝導を抑制できる電界効果トランジスタを提供する。

【解決手段】

基板601上に、III族窒化物のバッファ層602、チャネル層603、障壁層605、およびキャップ層606が、前記順序で積層され、

各半導体層の上面は、(0001)結晶軸に垂直なIII族原子面であり、

バッファ層602は、格子緩和され、

障壁層605は、引っ張り歪みを有し、

チャネル層603およびキャップ層606が圧縮歪みを有するか、または、チャネル層603が格子緩和され、キャップ層606が引っ張り歪みを有し、

障壁層605上の一部の領域に、キャップ層606、ゲート絶縁膜607、およびゲート電極608が、前記順序で積層され、他の領域に、ソース電極609とドレイン電極610が形成されていることを特徴とする電界効果トランジスタ。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】初期故障や偶発故障の発生を低減する。

【解決手段】HFET1は、下層のGaN層13およびGaN層13の一部を露出させるトレンチT1が形成された上層のAlGaN層14よりなるIII族窒化物半導体層と、III族窒化物半導体層上に形成されたゲート絶縁膜15と、ゲート絶縁膜15上に形成されたゲート電極16と、を備える。少なくともゲート絶縁膜15と接触するトレンチT1底部のGaN層13上面には、原子層ステップが形成されている。原子層ステップのテラス幅の平均値は、0.2μm以上1μm未満である。

(もっと読む)

窒化物半導体装置

【課題】GaN系の窒化物半導体を用いたデバイスのゲートリセス量の制御性を向上することで、閾値電圧の面内均一性を向上することができる窒化物半導体装置を実現できるようにする。

【解決手段】窒化物半導体装置は、基板101上に形成された第1のGaN系半導体からなるバッファ層102と、第2のGaN系半導体からなるキャリア走行層103と、第3のGaN系半導体からなるキャリア供給層104とを備えている。キャリア供給層104の上には第1の絶縁膜105と、アルミニウムを含む第2の絶縁膜106と、第1の絶縁膜105より膜厚が厚い第3の絶縁膜107とが形成されている。ソース電極108及びドレイン電極109は第1の絶縁膜105上に形成されている。ゲート電極110は、リセス構造を含む第2の絶縁膜106及び第3の絶縁膜107上に形成されている。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】化合物半導体装置のソース電極、ドレイン電極及びゲート電極を形成するいずれの領域においても、残渣のない良好な半導体/金属界面が得られるようにする。

【解決手段】化合物半導体装置の製造方法を、基板1上に化合物半導体積層構造4を形成する工程と、化合物半導体積層構造上に金属膜5A〜5Cを形成する工程と、金属膜上にソース電極7及びドレイン電極8を形成する工程と、金属膜の一部を酸化又は窒化して、金属酸化物膜又は金属窒化物膜5CXを形成する工程と、金属酸化物膜又は金属窒化物膜上にゲート電極9を形成する工程とを含むものとする。

(もっと読む)

電子デバイス及びオーミック電極形成方法

【課題】製造工程において高温で短時間のアニールを可能にすることにより、イオン注入の工程が不要なAlxGa1−xN/AlyGa1−yNヘテロ接合のオーミック電極を備える電子デバイスを提供する。

【解決手段】

電子デバイスは、ワイドバンドギャップ化合物半導体層と、前記ワイドバンドギャップ化合物半導体層上に形成されるオーミック電極とを含む電子デバイスであって、前記ワイドバンドギャップ化合物半導体層は、IniAljGakN(i+j+k=1,0≦i≦1,0<j≦1,0≦k<1)からなる化合物半導体バリア層とAlyGa1−yN(0<y≦1)からなる化合物半導体チャネル層からなり、前記オーミック電極は、前記化合物半導体バリア層上に密着層が積層され、前記密着層上にオーミック層が積層されて形成された電極であり、前記密着層はZrからなるようにする。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】デバイス特性を維持し、ゲートリーク電流を低減できる電界効果トランジスタ及びその製造方法を提供する。

【解決手段】本発明に係る電界効果トランジスタ100は、III−V族窒化物半導体層構造と、半導体層構造上に離間して形成されたソース電極105及びドレイン電極106と、ソース電極105及びドレイン電極106の間に形成されたゲート電極108と、ソース電極105上及びドレイン電極106上に形成された電極保護膜107と、半導体層構造上に、ソース電極105、ドレイン電極106、ゲート電極108及び電極保護膜107の上面の少なくとも一部を覆うように形成され、半導体層構造を保護する第1のパッシベーション膜109を備え、第1のパッシベーション膜109は、所定の材料に対して化学的に活性であり、電極保護膜107は、所定の材料に対して化学的に不活性な金属である。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ゲート−ソース間およびゲート−ドレイン間のキャパシタンスの低減と、JFETをオンさせる際に必要なゲート印加電圧が高電圧になることを抑制する。

【解決手段】凹部4c内に形成されたi型(イントリンシック半導体)側壁層5を介してp+型ゲート領域6を形成する。このような構成とすれば、n+型層4とp+型ゲート領域6との間にさらにp+型ゲート領域6よりも低濃度のp-型層が必要とされない。このため、n-型チャネル層3に直接接触している高濃度のp+型ゲート領域6によって、n-型チャネル層3内に伸びる空乏層幅を制御できる。したがって、n+型層4とp+型ゲート領域6との間にさらにp-型層が備えられる場合と比較して、ゲート印加電圧が高電圧になることを抑制できる。また、p+型ゲート領域6の側面がi型側壁層5によってn+型層4と分離されるため、ゲート−ソース間およびゲート−ドレイン間のキャパシタンスを低減できる。

(もっと読む)

金属及びシリコンの交互層を含むコンタクト構造体並びに関連デバイスの形成方法

半導体デバイスを形成する方法であって、この方法は、半導体層を準備するステップと、半導体層上に第1の金属の第1の層を準備するステップとを含む。第1の金属の第1の層上に第2の層を準備することができる。第2の層は、シリコン層及び第2の金属の層を含むことができ、第1の金属及び第2の金属は異なり得る。第1の金属はチタンとすることができ、第2の金属はニッケルとすることができる。関連するデバイス、構造体、及び他の方法もまた説明される。 (もっと読む)

電界効果トランジスタ

【課題】高電圧を印加しても壊れにくい電界効果トランジスタを提供すること。

【解決手段】この電界効果トランジスタは、略同一の第1、第2トランジスタ部11,12を備える。第1のトランジスタ部11は、ヘテロ接合を含むIII族窒化物半導体層構造、III族窒化物半導体層構造上に間隔をおいて配置されたソース電極5およびドレイン電極7、フィールドプレート91を有するゲート電極6、ドレイン電極7を被覆するように配置された絶縁体層8を有する。フィールドプレート91は、ドレイン電極7を覆うようにひさし状に延在する。第2のトランジスタ部12は、第1のトランジスタ部11と略面対称に配置されている。第1のトランジスタ部11のIII族窒化物半導体層構造、絶縁体層8およびドレイン電極7は、第2のトランジスタ部12において対応する構造または層と一体化されている。

(もっと読む)

電界効果トランジスタ

【課題】蛇行した形状に形成されたリセス部を備えることにより、オン抵抗を低減することができる電界効果トランジスタを提供することを目的とする。

【解決手段】電界効果トランジスタ1は、チャネル層11と、チャネル層11とヘテロ接合を構成するキャリア供給層12と、キャリア供給層12の表面から掘り下げて形成されたリセス部13と、リセス部13に沿って形成された第1絶縁層31と、第1絶縁層31の上に形成された第1ゲート電極23と、リセス部13に対してチャネル長方向の一方側に形成されたソース電極21と、リセス部13に対してチャネル長方向の他方側に形成されたドレイン電極22とを備える。リセス部13は、ソース電極21とドレイン電極22とが平面視で平行に対向するチャネル長の範囲内において、蛇行しながらチャネル長方向と交差する方向に延長されている。

(もっと読む)

ヘテロ接合電界効果型トランジスタ及びその製造方法

【課題】ゲートリーク電流を抑制する、窒化物半導体からなるリセスゲート構造のヘテロ接合FET及びその製造方法を提供することを目的とする。

【解決手段】本発明のヘテロ接合電界効果トランジスタは、窒化物半導体からなるヘテロ接合電界効果トランジスタであって、バリア層4とバリア層4の上に形成されたキャップ層5を含む半導体層と、半導体層に下部を埋没するようにして半導体層上に設けられたゲート電極9と、ゲート電極9の側面と半導体層の間に設けられた絶縁膜10と、を備え、ゲート電極9は、下面のみが半導体層と接触することを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネルにおけるキャリア移動度が高く、ノーマリオフを実現する半導体装置を提供する。

【解決手段】 n型GaNキャップ層18の開口部28との界面(開口部境界面)は、複数のほぼ鉛直な面S1と、各面S1の間を補完するように形成された傾斜した面S3により構成されている。傾斜面はドライエッチングにより形成し、異方性エッチングによりダメージ層を除去する。縦型FET1では、GaN基板10上に、六方晶のGaN、AlGaNを、{ 0 0 0 1}面を成長面として、エピタキシャル成長させており、n型GaNキャップ層18における鉛直な面S1は、{ 1-1 0 0}面(m面)となる。m面は、C面とは異なり無極性面であるので、m面を成長面として、GaN電子走行層22、AlGaN電子供給層26を再成長させると、ピエゾ電荷等の分極電荷がAlGaN/GaNヘテロ界面に生じない。よって、縦型FET1においては、よりノーマリオフに近づけることが可能となる。

(もっと読む)

III族窒化物系電界効果トランジスタおよびその製造方法

【課題】オン抵抗が低いIII族窒化物系電界効果トランジスタおよびその製造方法を提供する。

【解決手段】本発明のIII族窒化物系電界効果トランジスタは、下地半導体層と、下地半導体層上に第1窒化物半導体層、第2窒化物半導体層、および第3窒化物半導体層が順次積層された窒化物半導体積層体と、ソース電極およびドレイン電極と、第2窒化物半導体層および第3窒化物半導体層が形成されていない領域であるリセス領域と、リセス領域の内面および窒化物半導体積層体の上面に形成された絶縁膜と、絶縁膜上に形成されたゲート電極とを含み、絶縁膜に接する第1窒化物半導体層の上面と、第2窒化物半導体層に接する第1窒化物半導体層の上面とに段差がないことを特徴とする。

(もっと読む)

半導体装置

【課題】ゲート漏れ電流と電流コラプスとをコマーシャルレベルの高い特性要求を満足するレベルまで抑制した半導体装置の製造方法を提供する。

【解決手段】基板上にGaN電子走行層120と、前記GaN電子走行層上にAlGaN電子供給層130と、前記AlGaN電子供給層上にGaN薄膜層140と、前記GaN薄膜層上にゲート電極160と、前記GaN薄膜層上に前記ゲート電極を挟むソース電極150およびドレイン電極170とを備え、前記ソース電極と前記ゲート電極との間および前記ゲート電極と前記ドレイン電極との間の前記GaN薄膜層の結晶表面上に、水素含有量が15%以下の窒化珪素膜180を有することを特徴とする半導体装置。

(もっと読む)

横型HEMTおよび横型HEMTの製造方法

【課題】高いアバランシュブレークダイン強度を有する横型HEMTと、その製造方法を提供する。

【解決手段】基板10と、基板上に配置された、第1導電型のチヤネルとなる第1層11、少なくとも部分的に上記第1層11の上に配置された電子供給層となる第2層12を有する。さらに、上記横型HEMTは、上記第1導電型に対して相補的な第2導電型の半導体物質を有し、少なくとも部分的に上記第1層11の中に配置された第3層13を有する。このためPNダイオードが上記第1層および第3層の間で形成され、PNダイオードは横型HEMTより低いブレークダウン電圧を有することにより、HEMTを高い電界から保護することができ、HEMTの劣化を防止できる。

(もっと読む)

半導体装置及びその製造方法

【課題】高い高周波利得と高出力密度とを兼ね備える半導体装置及びその製造方法を提供すること。

【解決手段】本発明は、基板1上に、バッファ層2、チャネル層3、電子供給層4が順に形成されている。電子供給層4は表面保護膜21で覆われている。また、電子供給層4に接するソース電極6及びドレイン電極7が形成されている。ゲート電極8は、ソース電極6とドレイン電極7の間で、電子供給層4に接して形成されている。さらに、電子供給層4に形成された凹部5に充填された絶縁体からなる電界緩和層11が形成されている。

(もっと読む)

61 - 80 / 143

[ Back to top ]