Fターム[5F102GV09]の内容

接合型電界効果トランジスタ (42,929) | その他の構造 (2,409) | 表面保護膜を形成したもの (2,097) | ネイティブオキサイド(表面酸化膜) (143)

Fターム[5F102GV09]に分類される特許

21 - 40 / 143

半導体装置及び半導体装置の製造方法

【課題】窒化物半導体層をチャネルとして用いたトランジスタにおいて、閾値電圧を高くする。

【解決手段】第2窒化物半導体層200は、Alの組成比が互いに異なる複数の窒化物半導体層を順次積層した構造を有するため、Al組成が階段状に変化している。第2窒化物半導体層200を形成する複数の半導体層は、それぞれが同一方向に分極している。そしてゲート電極420に近い半導体層は、ゲート電極420から遠い半導体層よりも、分極の強度が強く(又は弱く)なっている。すなわち複数の半導体層は、ゲート電極420に近づくにつれて、分極の強度が一方向に変化している。この分極の方向は、複数の半導体層内の界面において負の電荷が正の電荷よりも多くなる方向である。

(もっと読む)

窒化物系半導体素子

【課題】本実施形態は、窒化物半導体層のクラックがほとんどなく、表面の粗度が極めて優秀であるので、全体的な安定性の向上された窒化物系半導体素子を提供する。

【解決手段】本実施形態の窒化物系半導体素子は、基板と、前記基板上に形成されるアルミニウムシリコンカーバイド(AlSixC1−x)前処理層と、前記前処理層上に形成されるAlがドーピングされたGaN層と、前記AlがドーピングされたGaN層上に形成されるAlGaN層とを含む。

(もっと読む)

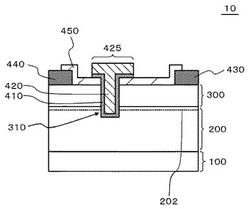

半導体装置及び半導体装置の製造方法

【課題】装置面積を増大させることなく、保護素子を有する半導体装置を提供する。

【解決手段】P型のIII族窒化物半導体からなる第1P型層200と、第1P型層200の一部上には、ゲート絶縁膜420およびゲート電極440とが設けられている。第1P型層200内のうち、ゲート電極440の両脇には、N型のソース領域340およびドレイン領域320が設けられている。また、第1P型層200の下には、N型のIII族窒化物半導体からなる第1N型層100が設けられている。基板内には、N型のIII族窒化物半導体とオーミック接続する材料からなるオーミック接続部(たとえばN型GaN層520)が、ソース領域340および第1N型層100と接するように設けられている。また、ドレイン電極600は、ドレイン領域320および第1P型層200と接するように設けられている。

(もっと読む)

電界効果トランジスタ

【課題】動的な耐圧であるダイナミック耐圧の低下を抑制できるGaN系のHFETを提供する。

【解決手段】このGaN系のHFETでは、各ソース電極12の長手方向の長さL2と各ドレイン電極11の長手方向の長さL1とが同じ長さである。また、ソース電極12の長手方向の端12A,12Bの長手方向の位置は、ドレイン電極11の長手方向の端11A,11Bの長手方向の位置と一致している。ソース電極12の長手方向の両端12A,12Bがドレイン電極11の長手方向の両端11A,11Bよりも長手方向外方へ突出していない構成により、ソース電極12の端12A,12Bからドレイン電極11の端11A,11Bへ向かって電子流が集中することを回避できる。

(もっと読む)

電界効果トランジスタ

【課題】動的な耐圧であるダイナミック耐圧の低下を抑制できるGaN系のHFETを提供する。

【解決手段】このGaN系のHFETでは、ドレイン電極12の長手方向の端12A,12Bから長手方向と直交する短手方向に伸ばした仮想線M1,M2よりも長手方向外方に位置すると共にソース電極11に隣接する領域の下のGaN系積層体5、およびドレイン電極12の長手方向の端12A,12Bに長手方向外側に隣接する領域の下のGaN系積層体5に2次元電子ガスが存在しない2次元電子ガス除去領域31が形成されている。2次元電子ガス除去領域31の存在によって、スイッチング時の動的な電界変動によってソース電極11の端部からドレイン電極12の端部へ向かって電子流が集中することを回避できる。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】半導体素子、例えばFETのソース領域にショットキー電極を形成し、ゲート電極をソース電極の一部領域と窒化物半導体領域の一部に形成することによって、ノーマリ−オフまたはエンハンスメントモード動作する半導体素子及び製造方法を提供する。

【解決手段】基板10上に配設され、内部に2次元電子ガス(2DEG)チャネルを形成する窒化物半導体層30と、該窒化物半導体層30にオミック接合されたドレイン電極50と、該ドレイン電極50と離間して配設され、該窒化物半導体層30にショットキー接合されたソース電極60と、該ドレイン電極50と該ソース電極60との間の窒化物半導体層30上及び該ソース電極60の少なくとも一部上にかけて形成された誘電層40と、該ドレイン電極50と離間して誘電層40上に配設され、一部が誘電層40を挟んでソース電極60のドレイン方向のエッジ部分上に形成されたゲート電極70とを含む。

(もっと読む)

半導体装置

【課題】オン抵抗が低く、かつ、Vthが高い半導体装置を提供する。

【解決手段】基板102の上方に、III−V族化合物半導体で形成されたバックバリア層106と、バックバリア層106上に、バックバリア層106よりバンドギャップエネルギーが小さいIII−V族化合物半導体で形成され、バックバリア層106の上方の少なくとも一部に設けられたリセス部122において、他の部分より膜厚が薄いチャネル層108と、チャネル層108にオーミック接合された第1の電極116,118と、少なくともリセス部においてチャネル層の上方に形成された第2の電極120と、を備える半導体装置を提供する。

(もっと読む)

半導体装置

【課題】電流コラプスが抑制され、耐圧の高い半導体装置を提供する。

【解決手段】基板110と、基板110の上方に形成された窒化物系化合物半導体からなるバッファ層120と、バッファ層120上に形成された窒化物系化合物半導体からなるチャネル層130と、チャネル層130の上方に形成された窒化物系化合物半導体からなる電子供給層132と、電子供給層132の上方に形成された第1の電極136と、電子供給層132の上方に形成された第2の電極138と、を備え、第2の電極138の電位に対して、基板110の電位および第1の電極136の電位が同じ側であり、第2の電極138の下の領域のバッファ層120の厚さおよびチャネル層130の厚さの合計が、第1の電極136の下の領域のバッファ層120の厚さおよびチャネル層130の厚さの合計より、大きい半導体装置。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】FETのソース領域にショットキー電極を形成し、内部にオミックパターン電極を備え、ゲート電極をソース電極の一部領域と窒化物半導体領域の一部に形成することによって、ノーマリ−オフ動作すると共に高耐圧及び高電流で動作可能な、半導体素子及び製造方法を提供する。

【解決手段】内部に2次元電子ガス(2DEG)チャネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ドレイン電極50と離間され、窒化物半導体層30にショットキー接合されるソース電極60と、ドレイン電極50とソース電極60との間の窒化物半導体層30上及びソース電極60の少なくとも一部上にかけて形成された誘電層40と、ドレイン電極50と離間されるように誘電層40上に配設され、一部が誘電層40を挟んでソース電極60のドレイン方向のエッジ部分上部に形成されたゲート電極70とを含む。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】オン抵抗を低め、高電流で動作する半導体素子及び製造方法を提供する。

【解決手段】基板10上部に配設され、内部に2次元電子ガスチャネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ドレイン電極50と離間して配設され、窒化物半導体層30にショットキー接合されたソース電極60と、ドレイン電極50とソース電極60との間の窒化物半導体層30上及びソース電極60の少なくとも一部上にかけて形成され、ドレイン電極50とソース電極60との間にリセスを形成する誘電層40と、ドレイン電極50と離間して誘電層40上及びリセスに配設され、一部が誘電層40を挟んでソース電極60のドレイン方向へのエッジ部分上部に形成されたゲート電極70とを含む。

(もっと読む)

半導体装置

【課題】オン抵抗が低く、かつ、耐圧が高いノーマリーオフの半導体装置を提供する。

【解決手段】基板102の上方に形成された、III−V族化合物半導体からなるバックバリア層106と、バックバリア層106上に形成され、バックバリア層よりバンドギャップエネルギーが小さいIII−V族化合物半導体からなるチャネル層と108、チャネル層108にオーミック接続された第1の電極116,118と、チャネル層の上方に形成された第2の電極120と、を備え、バックバリア層106は第2の電極120の下方に設けられ、かつ、第2の電極120の下方から第1の電極の116,118下方まで連続して設けられていない半導体装置を提供する。

(もっと読む)

半導体装置とその製造方法

【課題】 エッチングによるダメージを抑制しながら、ヘテロ接合面の近傍に負イオンを導入する技術を提供する。

【解決手段】 導入領域8上に保護膜30を形成する保護膜形成工程と、保護膜形成工程の後に、導入領域8を負イオンを含むプラズマに曝すプラズマ工程を備えている。保護膜30は、プラズマに対するエッチング速度が導入領域8よりも小さい。保護膜30には、負イオンを通過させることが可能な材料が用いられている。プラズマ中の負イオンは、保護膜30を通過し、導入領域8に導入される。

(もっと読む)

窒化物半導体装置及びその製造方法

【課題】低オン抵抗、高耐圧及び高信頼性を達成する。

【解決手段】窒化物半導体装置110は、第1半導体層3、第2半導体層4、第1電極10、第2電極7、第3電極8、第1絶縁膜6及び第2絶縁膜5を備える。第1半導体層3は、窒化物半導体を含む。第2半導体層4は、第1半導体層3上に設けられ、孔部4aを有する。第2半導体層4は、第1半導体層3よりも広い禁制帯幅を有する窒化物半導体を含む。第1電極10は、孔部4a内に設けられる。第1電極10の一方側に第2電極7、他方側に第3電極8が設けられ、それぞれ第2半導体層4と電気的に接続される。第1絶縁膜6は、酸素を含有する膜であって、第1電極10と孔部4aの内壁とのあいだ、及び第1電極10と第2電極7とのあいだに設けられ、第3電極8と離間して設けられる。第2絶縁膜5は、窒素を含有する膜であって、第1電極10と第3電極8とのあいだで第2半導体層4に接して設けられる。

(もっと読む)

窒化物半導体装置

【課題】定電流動作が可能な窒化物半導体装置を提供する。

【解決手段】窒化物半導体を含む半導体層30と、ソース電極40と、ドレイ電極50と、第1ゲート電極10と、第2ゲート電極20と、を備えた窒化物半導体装置111が提供される。ソース電極40とドレイン電極50は、主面上に設けられ、半導体層とオーミック性接触を形成し、互いに離間する。第1ゲート電極10は、主面上においてソース電極40とドレイン電極50との間に設けられる。第2ゲート電極20は、主面上においてソース電極40と第1ゲート電極10との間に設けられる。ソース電極40と第1ゲート電極10との間の電位差が0ボルトのときに、半導体層30のうちの第1ゲート電極に対向する部分は導通する。第1ゲート電極10は、第2ゲート電極20に印加される電圧に応じた定電流をスイッチングする。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】バッファ層の結晶成長時に高抵抗化の不純物をドーピングすることなく上層の化合物半導体の結晶品質を保持するも、バッファ層を高抵抗化してオフリーク電流を確実に抑制し、信頼性の高い高耐圧の化合物半導体装置を実現する。

【解決手段】化合物半導体積層構造2の裏面から、化合物半導体積層構造2の少なくともバッファ層2aに不純物、例えばFe,C,B,Ti,Crのうちから選ばれた少なくとも1種類を導入し、バッファ層2aの抵抗値を高くする。

(もっと読む)

化合物半導体装置の製造方法及び洗浄剤

【課題】リセス等の形成に伴う処理で生じる残渣を適切に除去することができる化合物半導体装置の製造方法及び洗浄剤を提供する。

【解決手段】化合物半導体積層構造1を形成し、化合物半導体積層構造1の一部を除去して凹部4を形成し、洗浄剤を用いて凹部4内の洗浄を行う。洗浄剤は、凹部4内に存在する残渣と相溶する基材樹脂と溶媒とを含む。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】絶縁膜を有する窒化物半導体を低コストで製造する。

【解決手段】基板10の上方に形成された半導体層22,23,24と、前記半導体層の一部を酸化することにより形成された絶縁膜30と、前記絶縁膜上に形成された電極41と、を有し、前記絶縁膜は、酸化ガリウムを含むもの、または、酸化ガリウム及び酸化インジウムを含むものにより形成されているものであることを特徴とする半導体装置。

(もっと読む)

半導体装置、電源装置、増幅器及び半導体装置の製造方法

【課題】半導体装置に形成される絶縁膜の付着力を高め歩留りを向上させる。

【解決手段】基板10の上方に形成された半導体層20〜23と、前記半導体層20〜23上に形成された絶縁膜31,32と、前記絶縁膜上31,32に形成された電極41と、を有し、前記絶縁膜31,32は、前記電極41の側における膜応力よりも、前記半導体層20〜23の側における膜応力が低いことを特徴とする半導体装置により上記課題を解決する。

(もっと読む)

キャップ層および埋込みゲートを有する窒化物ベースのトランジスタを作製する方法

【課題】埋込み部を形成する際のエッチングにより埋込みゲートが損傷をきたし、ゲート領域劣化が生じ得る。

【解決手段】ショットキーコンタクトなどのゲートコンタクトを形成する前にゲート埋込み部のアニーリングを行うことにより、ゲートリークが低減され、かつ/またはトランジスタなどの半導体デバイス内に高品質のゲートコンタクトを提供することができる。アニーリング中に封入層を使用することで、トランジスタのゲート埋込み部内の半導体への損傷がさらに低減される。アニーリングを、例えばデバイスのオーミックコンタクトのアニーリングによって提供することができる。

(もっと読む)

半導体装置

【課題】電流コラプスの発生を抑制できるIII族窒化物半導体トランジスタおよびその製造方法を提供する。

【解決手段】FET1では、第1窒化物半導体層103の上に第2窒化物半導体層104が設けられ、少なくとも一部が第2窒化物半導体層104に接するようにソース電極106およびドレイン電極107が設けられている。第2窒化物半導体層104の上面においてソース電極106とドレイン電極107との間に位置するように凹部110aが形成されており、ゲート電極108が凹部110aの開口を覆うように凹部110aの上方に設けられている。

(もっと読む)

21 - 40 / 143

[ Back to top ]