Fターム[5F103LL13]の内容

半導体装置を構成する物質の物理的析出 (6,900) | 適用デバイス・適用構造 (785) | SOI構造 (230) | 薄膜トランジスタ(TFT) (229)

Fターム[5F103LL13]に分類される特許

201 - 220 / 229

窒素ガスを用いた亜鉛ターゲットの反応性スパッタにより形成される薄膜半導体材料

本発明は概して、半導体膜及びこの半導体膜の堆積に使用する反応性スパッタ法を含む。スパッタリングターゲットは純粋な亜鉛(すなわち、99.995原子百分率以上)を含み、アルミニウム(約1原子百分率〜約20原子百分率)又はその他のドープ金属でドープしてもよい。亜鉛ターゲットは、窒素及び酸素をチャンバに導入することにより反応的にスパッタされる。窒素の量は、酸素及びアルゴンガスの量よりはるかに多い。酸素の量は、窒素含有ガスを使用しない堆積で得られた測定値に基づく膜構造の転換点、膜透過率、DC電圧変化又は膜導電性を踏まえたものである。反応性スパッタは、室温前後から数百度にのぼる温度で行われる。堆積後、半導体膜をアニールすることにより、膜の移動度を更に改善してもよい。  (もっと読む)

(もっと読む)

薄膜トランジスタおよびその製造方法

本発明は、薄膜トランジスタおよびその製造方法に関する。具体的に、本発明は、薄膜トランジスタにおいて、半導体層のチャネル物質としてSiを含む酸化亜鉛系物質を用いる薄膜トランジスタおよびその製造方法に関する。また、本発明は、チャネル物質の蒸着後にプラズマ窒化工程および酸素熱処理工程を経る薄膜トランジスタの製造方法に関する。さらに、本発明は、基板、ゲート電極、絶縁層、半導体層、ソース電極、およびドレイン電極を含む薄膜トランジスタにおいて、前記半導体層が、Siを含む酸化亜鉛系半導体チャネル物質を含む薄膜トランジスタに関する。  (もっと読む)

(もっと読む)

非晶質酸化物半導体薄膜、その製造方法、薄膜トランジスタの製造方法、電界効果型トランジスタ、発光装置、表示装置及びスパッタリングターゲット

【課題】インジウム、錫、亜鉛の量を適正化することにより、リン酸系エッチング液に不溶であり、かつ、蓚酸系エッチング液に可溶な非晶質酸化物半導体薄膜や、その製造方法などの提供を目的とする。

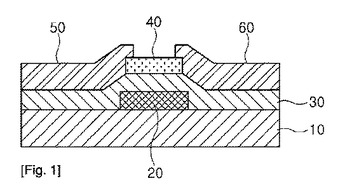

【解決手段】画像表示装置1は、ガラス基板10、光制御素子としての液晶40、この液晶40を駆動するためのボトムゲート型薄膜トランジスタ1、画素電極30及び対向電極50を備えており、ボトムゲート型薄膜トランジスタ1の非晶質酸化物半導体薄膜2は、キャリア密度が10+18cm−3未満であり、さらに、リン酸系エッチング液に対して不溶であり、かつ、蓚酸系エッチング液に対して可溶である。

(もっと読む)

Si結晶薄膜の形成方法

【課題】ガラスなどの絶縁基板やその他半導体、金属などの基板上にSi結晶半導体薄膜をSiの融点以下の温度で形成する方法を提供する。

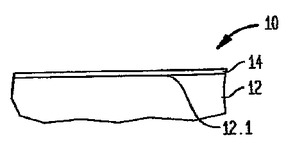

【解決手段】基板1上に形成されたZn−Si二元合金系を出発材料とし、その液体もしくは過冷却液体の状態から熱平衡状態でのSiの析出、残存Znの冷却固化、そしてエッチング等による該Znの除去を経て基板に支持されたSi薄膜4−1が形成される。

(もっと読む)

低電圧有機薄膜トランジスタ及びその製造方法

【課題】プラスチック基板やガラス基板などに低温工程で形成するものの、数nmの厚みでゲート絶縁膜を形成することにより、低電圧動作、且つ商用化が容易な有機薄膜トランジスタ及びその製造方法を提供する。

【解決手段】基板上に金属をパターニングし、蒸着してゲート電極12を形成した後、常温乃至100℃以下でO2プラズマ工程によりゲート電極12を直接酸化して10nm以下の厚みで金属酸化膜を成長させることで、ゲート電極の表面に沿ってゲート絶縁膜13を形成する。次いで、ゲート絶縁膜13の上に有機半導体膜14を蒸着し、有機半導体膜14上にソース/ドレイン電極15/16を互いに一定の距離をもって離隔するように形成する。二重ゲート絶縁膜とする場合には、有機絶縁膜を、自己組立工程またはスピンコーティング工程で金属酸化膜の上に形成する。

(もっと読む)

半導体素子の製法

【課題】 熱的安定性の高い酸化物半導体薄膜層を有する半導体素子の製法を提供することを解決課題とする。

【解決手段】 基板上に、スパッタリング法により成膜された酸化亜鉛を主成分とする酸化物半導体薄膜層を有する半導体素子の製法であって、前記スパッタリング法による前記酸化物半導体薄膜層の成膜において、酸素を含有したスパッタリングガスを用い、且つ、成膜時に前記基板にバイアス電力を印加することを特徴とする半導体素子の製法である。

(もっと読む)

ドナーシート、ドナーシートの製造方法、有機薄膜トランジスタの製造方法

【課題】高精度な転写が可能なドナーシート、ドナーシートの製造方法、小型の有機薄膜トランジスタの製造方法を提供することを課題とする。

【解決手段】被転写基板に所定の形状の転写層を転写するためのドナーシートであって、基材シート上に光熱変換層と有機半導体材料を含む転写層とがこの順で積層されてなるドナーシートにおいて、光熱変換層は、所定の形状と同一の形状に予めパターニングされていることを特徴とするドナーシート。

(もっと読む)

薄膜素子の製造方法

【課題】2回の蒸着作業で薄膜素子を製造し、かつマスク層の直下ではなくマスク層の開口部にギャップを配することも可能な薄膜素子の製造方法を提供する。

【解決手段】開口部を有するマスク層を用いた、半導体または半金属の薄膜を有する薄膜素子の製造方法であり、前記マスク層面に垂直な軸に対して第1の角度方向から、前記開口部を介して基板上に電極材料を蒸着する第1の蒸着工程と、前記軸と前記第1の角度方向とがなす2次元平面において、第2の角度方向から前記開口部を介して薄膜材料を前記基板上に蒸着する第2の蒸着工程とを有する。

(もっと読む)

酸化物半導体素子およびその製造方法

【課題】良好なpn接合を容易に形成することが可能なZnO系の酸化物半導体素子を提供する。

【解決手段】この酸化物半導体素子では、ZnOからなるn型の単結晶基板1の上面に、ZnOからなるp型の多結晶薄膜2が形成されている。また、n型の単結晶基板1の下面には、Alからなる電極8が形成されており、p型の多結晶薄膜2の上面には、Auからなる電極9が形成されている。

(もっと読む)

真空成膜装置

【課題】加熱チャンバーにより加熱された基板の温度を均一に保持しつつ大気圧から真空に移行させることができるロードロックチャンバーを備えた真空成膜装置を提供する。

【解決手段】真空成膜装置1におけるロードロックチャンバー20は、その内部空間を所定温度に保持するための保熱手段23を備える。この保熱手段23は、基板が収容される内部空間を形成し且つ該内部空間における対流の発生を実質的に防止又は抑制するように配置された複数のヒータパネル23a〜23cからなる。このような構成により、上記の内部空間Sにおいて対流が発生しにくくなるので、ロードロックチャンバー20内に搬入されてきた基板2の温度を均一に保持しつつ大気圧から真空に移行させることができる。

(もっと読む)

単結晶基板上にエピタキシャル成長したグラフェン層を含むデバイス

電子デバイスは、物質の主表面に単結晶領域を含む物質を含む。単結晶領域は、グラフェンと実質的に格子整合している六方晶格子を有し、グラフェンの少なくとも1つのエピタキシャル層がこの単結晶領域に配置される。現在好ましい実施形態では、単結晶領域は多層の六方晶BNを含む。このような電子デバイスの作製方法は、物質の主表面に単結晶領域を含む物質を提供し、単結晶領域は、グラフェンと実質的に格子整合している六方晶格子を有するステップ(a)と、この領域に少なくとも1つのグラフェン層をエピタキシャル形成するステップ(b)を含む。現在好ましい実施形態では、ステップ(a)は、グラファイトの単結晶基板を提供するステップ(a1)と、基板に多層の単結晶六方晶BNをエピタキシャル形成するステップ(a2)とをさらに含む。六方晶BN層はグラフェンと実質的に格子整合した表面領域を有し、ステップ(b)は六方晶BN層の表面領域に少なくとも1つのグラフェン層をエピタキシャル形成するステップを含む。FETへの応用が説明されている。  (もっと読む)

(もっと読む)

薄膜成膜装置

【課題】 製造プロセスを簡単化することができ、TATの短縮や製造コストの低減に寄与し得る薄膜成膜装置を提供する。

【解決手段】 本発明の薄膜成膜装置は、基板上に多結晶シリコン膜を成膜する第1の成膜室33と、前記多結晶シリコン膜上に絶縁膜を成膜する第2の成膜室34と、前記絶縁膜上に導電膜を成膜する第3の成膜室35とを有して構成され、これら3つの成膜室が基板搬送室32を介して大気に対して気密保持可能に連設される。

(もっと読む)

薄膜トランジスタ及びその製造方法及び成膜装置

【課題】支持基材上に、ゲート電極、ゲート絶縁膜、酸化物からなる半導体活性層、ソース電極、ドレイン電極が形成されて成るボトムゲート型薄膜トランジスタの製造方法において、ゲート絶縁膜と、半導体活性層間で汚れ付着等による汚染のない清浄な界面を実現と、生産性が高く、安価かつ大量に生産できる上、特性の優れたフレキシブル薄膜トランジスタを提供することを課題とする。

【解決手段】ゲート電極を形成した可撓性プラスチックの基材2上に、ゲート絶縁膜、酸化物からなる半導体活性層を形成するボトムゲート型薄膜トランジスタの製造方法であって、ロール状の基材2を連続巻取方式の成膜装置12の真空成膜室内で、ゲート絶縁膜と酸化物からなる半導体活性層とを大気開放することなく連続してスパッタ法により形成することを特徴とする薄膜トランジスタの製造方法。

(もっと読む)

半導体薄膜、及びその製造方法、並びに薄膜トランジスタ、アクティブマトリックス駆動表示パネル

【課題】比較的低温で作製でき、屈曲性のある樹脂基板上にも形成可能な半導体薄膜であって、可視光に対して安定で、かつ、トランジスタ特性などの素子特性が高く、表示装置を駆動するスイッチング素子として用いた際に、画素部と重なっても表示パネルの輝度を低下させない半導体薄膜、及びそのような半導体薄膜の製造方法、並びにそのような半導体薄膜を用いた、電界効果移動度とon−off比が高いとともに、漏れ電流の発生などの照射光による影響を小さくして、素子特性を向上させた薄膜トランジスタ、そのような薄膜トランジスタを適用したアクティブマトリックス駆動表示パネルを提供する。

【解決手段】キャリア密度が10+17cm−3以下、ホール移動度が2cm2/V・sec以上、エネルギーバンドギャップが2.4EV以上となるように、酸化亜鉛と酸化インジウムを含有する非晶質膜を成膜した後に、酸化処理して透明半導体薄膜40を形成する。

(もっと読む)

酸化物薄膜の成膜方法

【課題】

チャンバーに導入される被成膜物から放出される酸素原子を含むガスの放出量に関わらず、チャンバー内の酸素分圧を常に一定に保って成膜することを可能にし、製品間での品質のばらつきを最小限に抑えることを目的とする。

【解決手段】

真空中に放置するとガスを放出する被成膜物へ、酸素を含むガス雰囲気で酸化物薄膜を成膜するにあたって、該放出ガス成分に酸素原子が含まれるチャンバー内の酸素割合を、プラズマ中の酸素の発光強度を監視して、前記酸素割合が設定したある一定の値になるようにチャンバーへ導入する酸素流量を制御して成膜を行うことにより解決した。

(もっと読む)

半導体薄膜及びその製造方法

【課題】酸化インジウムを主成分とし、酸化セリウムを添加した酸化物により、光による誤作動がなく、加熱等による薄膜の比抵抗の変化がなく、移動度が高い透明酸化物半導体及びその製造方法を提供することである。

【解決手段】酸化インジウムと酸化セリウムとを含有し、結晶質からなる半導体薄膜であって、比抵抗が10+1〜10+8Ωcmであることを特徴とする半導体薄膜を用いる。この半導体薄膜は、比抵抗の変化が少なく、また、移動度が高い。したがって、この半導体薄膜を用いてスイッチング素子を構成すれば、スイッチング性能が向上した素子が得られる。

(もっと読む)

結晶性シリコン薄膜の形成方法及び装置

【課題】比較的低温下で、安価に、安全に結晶性シリコン薄膜を得て、該結晶性シリコン薄膜から容易に終端処理された結晶性シリコン薄膜を得ることができる結晶性シリコン薄膜の形成方法及び装置を提供する。

【解決手段】シリコンスパッタターゲットTと被成膜物品Sを設置した成膜室1内に水素ガスを導入し、高周波電力を印加して、プラズマ発光における波長656nmでの水素原子ラジカルの発光スペクトル強度Hα及び波長414nmでのシランラジカルの発光スペクトル強度SiH* との比(Hα/SiH* )が0.3〜1.3であるプラズマを発生させ、該プラズマにてシリコンスパッタターゲットTをケミカルスパッタリングして被成膜物品S上に結晶性シリコン薄膜を形成し、次いで、終端処理室10において、終端処理用ガスに高周波電力を印加することで発生させた終端処理用プラズマのもとで該結晶性シリコン薄膜の表面を終端処理する。

(もっと読む)

半導体薄膜

【課題】 多元系の酸化物薄膜を作製する場合に、面内方向に組成分布が生じ難い酸化物半導体薄膜、及びその製造方法を提供する。

【解決手段】 組成又は構成元素が互いに異なる複数の酸化物層による積層構造からなる半導体薄膜において、前記酸化物層の一部又は全部がアモルファスである。前記酸化物層の厚さが0.05〜10nmである。前記酸化物層の一部又は全部が、In、Ga、Zn、Sn、Sb、Ge、又はAsのいずれかの元素を含有する。前記組成の異なる複数種以上の酸化物層の積層構造は、1積層単位が繰り返し成膜された複数の積層単位としてもよい。

(もっと読む)

スパッタリングターゲットおよび該ターゲットを用いた薄膜の形成方法

【課題】アモルファス酸化物膜をスパッタリング成膜する際に高い再現性と歩留まりを得るためのスパッタリングターゲットを提供する。

【解決手段】酸化物スパッタリングターゲットは、少なくともIn、Zn、Gaを含むアモルファス酸化物膜をスパッタリング成膜する際に用いられる焼結体ターゲットである。このターゲットは、その組成にIn、Zn、Gaを含み、相対密度が75%以上、且つ抵抗値ρが50Ωcm以下である。このターゲットは、ホモロガス相の結晶構造を示す多結晶酸化物焼結体である。このターゲットを用いて、電子キャリア濃度が1018/cm3未満のアモルファス酸化物膜を室温以上450℃以下の成膜温度でスパッタリング法により形成する。

(もっと読む)

薄膜トランジスタの製法

【課題】 酸化亜鉛(ZnO)を主成分とする酸化物を半導体薄膜層(活性層)として有する薄膜トランジスタにおいて、製造工程を大幅に低温化するとともに、半導体薄膜層と、該半導体薄膜層上に形成した界面制御型ゲート絶縁膜との界面の清浄化を達成することによって、プラスティック基板上に形成した液晶表示装置や有機エレクトロルミネッセンス素子(OLED)への応用を可能とした高性能薄膜トランジスタの製法の提供。

【解決手段】 酸化亜鉛ZnOを主成分とする酸化物からなる半導体薄膜と、シリコン系絶縁膜からなり該半導体薄膜に接するゲート絶縁膜を有する薄膜トランジスタの製法において、前記半導体薄膜の形成と前記ゲート絶縁膜の形成が真空中にて連続した工程で行われ、前記ゲート絶縁膜が、誘導結合方式プラズマ化学気相成長(ICP−CVD)法又は電子サイクロトロン共鳴化学気相成長(ECR−CVD)法により形成され、全製造工程が200℃以下の温度条件下にて行われることを特徴とする薄膜トランジスタの製法。

(もっと読む)

201 - 220 / 229

[ Back to top ]