Fターム[5F110CC06]の内容

Fターム[5F110CC06]に分類される特許

61 - 80 / 105

半導体装置

【課題】微細化による電気特性の変動が生じにくい半導体装置を提供する。

【解決手段】第1の領域と、第1の領域の側面に接した一対の第2の領域と、一対の第2の領域の側面に接した一対の第3の領域と、を含む酸化物半導体膜と、酸化物半導体膜上に設けられたゲート絶縁膜と、ゲート絶縁膜上に第1の領域と重畳した第1の電極と、を有し、第1の領域は、CAAC酸化物半導体領域であり、一対の第2の領域及び一対の第3の領域は、ドーパントを含む非晶質な酸化物半導体領域であり、一対の第3の領域のドーパント濃度は、一対の第2の領域のドーパント濃度より高い半導体装置である。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】高速動作可能な半導体装置を提供する。また、短チャネル効果による電気特性の変動が生じにくい半導体装置を提供する。

【解決手段】トランジスタの半導体層に結晶性を有する酸化物半導体を用い、該半導体層にチャネル形成領域とソース領域とドレイン領域を形成する。ソース領域及びドレイン領域は、ゲート電極をマスクとして、半導体層に第15族元素のうち一種類または複数種類の元素を添加する自己整合プロセスにより形成する。ソース領域及びドレイン領域に、ウルツ鉱型の結晶構造を付与することができる。

(もっと読む)

半導体装置およびその作製方法

【課題】短チャネル効果による電気特性の変動が生じにくい、チャネル領域に酸化物半導体を含むトランジスタを用いた半導体装置を作製する。

【解決手段】窒素を含む一対の酸窒化物半導体領域、および該一対の酸窒化物半導体領域に挟まれる酸化物半導体領域を有する酸化物半導体膜と、ゲート絶縁膜と、ゲート絶縁膜を介して酸化物半導体領域上に設けられるゲート電極とを有する半導体装置。ここで、一対の酸窒化物半導体領域はトランジスタのソース領域およびドレイン領域となり、酸化物半導体領域はトランジスタのチャネル領域となる。

(もっと読む)

半導体装置

【課題】トランジスタのしきい値電圧の変動を抑制し、表示パネルに実装するドライバICの接点数を削減し、表示装置の低消費電力化を達成し、表示装置の大型化又は高精細化を達成することを目的とする。

【解決手段】劣化しやすいトランジスタのゲート電極を、第1のスイッチングトランジスタを介して高電位が供給される配線、及び第2のスイッチングトランジスタを介して低電位が供給される配線に接続し、第1のスイッチングトランジスタのゲート電極にクロック信号を入力し、第2のスイッチングトランジスタのゲート電極に反転クロック信号を入力することで、劣化しやすいトランジスタのゲート電極に高電位、又は低電位を交互に供給する。

(もっと読む)

電界効果トランジスタ

【課題】インジウムを主要成分とし、金属半導体接合を用いた電界効果トランジスタのオフ電流を低減せしめる構造を提供する。

【解決手段】インジウムを主要成分とする、厚さ0.1〜100nmの第1の酸化物半導体(例えば、酸化インジウム)よりなる第1の半導体層1の一方の面に絶縁膜4を設け、他の面に接して、I型の第2の酸化物半導体(例えば、酸化ガリウム)よりなる第2の半導体層2を設ける。第2の酸化物半導体の真空準位からフェルミレベルまでのエネルギー差は第1の酸化物半導体のものよりも大きい。上記の条件を満たす第2の酸化物半導体との接触面近傍においては、極めてキャリア濃度の低い領域(準I型領域)となるので、その部分をチャネルとすることにより、オフ電流が低減できる。また、FETのドレイン電流は移動度の高い第1の酸化物半導体を流れるので、大電流を取り出せる。

(もっと読む)

半導体メモリ装置

【課題】オフ状態のソース、ドレイン間のリーク電流の低いトランジスタを書き込みトランジスタに用いて、データを保存する半導体メモリ装置を提供する。

【解決手段】書き込みトランジスタのドレインと読み出しトランジスタのゲート、および、前記ドレインとキャパシタの一方の電極を接続した記憶セルを2つ用いて形成された記憶ユニットのマトリクスにおいて、第1の記憶セルの書き込みトランジスタのゲートを第1のワード線に、キャパシタの他方の電極を第2のワード線に接続する。また、第2の記憶セルの書き込みトランジスタのゲートを第2のワード線に、キャパシタの他方の電極を第1のワード線に接続する。さらに、集積度を高めるために、各記憶セルの読み出しトランジスタのゲートを互い違いに配置する。

(もっと読む)

半導体膜の作製方法

【課題】量産性に優れた薄膜トランジスタを提供する。また半導体装置の作製において有

用な半導体薄膜を提供する。

【解決手段】プラズマCVD法により作製された希ガス元素を1×1020/cm3〜1

×1021/cm3で含む半導体膜を形成し、前記半導体膜の一部を除去して、活性層を

形成し、トップゲート型薄膜トランジスタまたはボトムゲート型薄膜トランジスタを作製

する。また、プラズマCVD法により作製された希ガス元素を1×1020/cm3〜1

×1021/cm3で含む半導体膜を剥離層として用いた半導体装置を作製する。また、

プラズマCVD法により作製された希ガス元素を1×1020/cm3〜1×1021/

cm3で含む半導体膜をゲッタリングサイトとして用いた半導体装置を作製する。

(もっと読む)

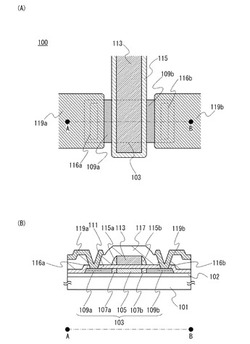

半導体装置およびその作製方法

【課題】トランジスタの微細化を達成し、電界緩和がなされた、酸化物半導体を用いた半導体装置を提供することを課題の一とする。

【解決手段】ゲート電極の線幅を微細化し、ソース電極層とドレイン電極層の間隔を短縮する。ゲート電極をマスクとして自己整合的に希ガスを添加し、チャネル形成領域に接する低抵抗領域を酸化物半導体層に設けることができるため、ゲート電極の幅、即ちゲート配線の線幅を小さく加工しても位置精度よく低抵抗領域を設けることができ、トランジスタの微細化を実現できる。

(もっと読む)

電界効果トランジスタ

【課題】導体半導体接合を用いた電界効果トランジスタのオフ電流を低減せしめる構造を提供する。

【解決手段】半導体層1に、半導体層1の電子親和力と同程度かそれ以下の仕事関数の材料よりなる第1の導体電極3a、第2の導体電極3bを接して設け、さらに、半導体層1のゲートの形成された面と逆の面に接して、半導体層1の電子親和力より大きな仕事関数の材料で、半導体層を横切るようにして、第3の導体電極2を形成することにより、半導体層中にショットキーバリヤ型の接合を形成し、この部分のキャリア濃度が極めて低いことから、オフ電流を低減できる。

(もっと読む)

半導体装置

【課題】様々な基材に被剥離層を貼りつけ、軽量された半導体装置およびその作製方法を提供する。

【解決手段】強磁性材料からなるシートを支持体とし、前記強磁性材料からなるシートに接する接着材と、該接着材に接する絶縁膜上に素子とを備える。上記構成において、前記素子は、薄膜トランジスタ、有機化合物を含む層を有する発光素子、液晶を有する素子、メモリー素子、薄膜ダイオード、シリコンのPIN接合からなる光電変換素子、またはシリコン抵抗素子であってもよい。また、上記各構成において、前記強磁性材料からなるシートは、軟質磁性粉体と合成樹脂とを混合して形成され、着磁されたものであってもよい。

(もっと読む)

半導体装置用基板及びその製造方法、半導体装置並びに電子機器

【課題】半導体装置用基板において、基板上に形成される各種絶縁膜に要求される各種仕様に対して個別に対応しつつ、省資源及び低コストの要請への対応を図る。

【解決手段】半導体装置用基板は、基板(10)上に、半導体層(30a)、半導体層に少なくとも部分的に重なるように島状に形成された第1絶縁膜(30c)、及び第1絶縁膜を介して半導体層に対向配置されたゲート電極(30b)を含んでなるトランジスター(30)と、第1絶縁膜と同一層に配置され、材料及び膜厚の少なくとも一方が第1絶縁膜と互いに異なるように島状に形成された第2絶縁膜(31)とを備える。

(もっと読む)

半導体デバイス及びその形成方法

【課題】応力ライナによるコンタクト形成の問題が起きない、相補型金属酸化膜半導体(CMOS)デバイスの製造方法を提供する。

【解決手段】シリコン基板層上の二酸化シリコン層102と、凹んだソース/ドレイン・トレンチを有する相補型金属酸化膜半導体(CMOS)デバイスを準備し、凹んだソース/ドレイン・トレンチ内に窒化物応力ライナ104を堆積し、その上に酸化物層106を堆積する。CMOSデバイスをハンドリング・ウェハ上に置きシリコン基板層を除去し二酸化シリコン層102をエッチングしてソース/ドレイン領域170の一部に当接する開口部を形成しコンタクト180を形成する。

(もっと読む)

半導体装置

【課題】非接触でデータの送受信が可能な安価な半導体装置及びその作製方法の提供する。

【解決手段】基板32に、メモリセルの有機化合物層20bに流れる電流を制御する素子であるTFT、ビット線である第1の電極層18a〜18c、ソース線17a〜17c、第2の電極層21、第1の電極層18a〜18cと第2の電極層21の間に有機化合物を含む積層(第1層(バッファ層20a)と第2層(有機化合物層20b)の積層)を設けている。有機化合物層20bは、導電性を有する有機化合物材料からなる層を単層または積層構造で設ける。導電性を有する有機化合物材料の具体例としては、キャリア輸送性を有する材料を用いることができる。集積回路部の接続電極28、電極29上にアンテナ30を形成する。

(もっと読む)

表示装置

【課題】光源側にゲート電極膜を有するTFTを複数個直列に設ける場合、光リーク電流の発生を抑えつつ、容量増加をも抑制することができる表示装置を提供することにある。

【解決手段】直列に設けれた複数個のチャネル領域のチャネル端のうち、映像信号線側及び画素電極側の最も近くに位置するチャネル端の外側に、対向するゲート端が位置し、当該チャネル端以外のチャネル端のうち少なくとも一つにおいて、チャネル端がゲート端のより近くに位置している。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタアレイ及び画像表示装置

【課題】絶縁層の上部と下部との導電体の間の導通をバンプにより十分に確保することができる薄膜トランジスタ、薄膜トランジスタアレイ及び画像表示装置を提供する。

【解決方法】バンプと、バンプにより貫通される絶縁層とを含む薄膜トランジスタにおいて、バンプがフッ素化合物を含み、絶縁層が塗布法で形成され、バンプのフッ素含有量が、0.01wt%以上5wt%以下であり、バンプが凹版印刷法またはスクリーン印刷法で形成されていることを特徴とする薄膜トランジスタ。

(もっと読む)

絶縁膜層分離IC製造

【課題】二酸化ケイ素や窒化ケイ素など非常に薄い低応力誘電体材料と半導体層とで形成された可とう性の膜で集積回路(24、26、28、...30)を製造する汎用手法を提供する。

【解決手段】膜(36)の半導体層中に半導体デバイス(24、26、28...30)を形成する。最初に、標準厚さの基板(18)から半導体膜層(36)を形成し、次いで、基板の薄い表面層をエッチングまたは研磨する。他のバージョンでは、ボンディングされた従来の集積回路ダイ用の支持および電気的相互接続として可とう性膜を使用し、膜中の複数の層に相互接続部を形成する。1つのそのような膜に複数のダイを接続することができ、膜は次いでマルチチップ・モジュールとしてパッケージされる。

(もっと読む)

薄膜トランジスタと、その製造方法と、薄膜トランジスタを用いた電子機器

【課題】本発明は薄膜トランジスタとその製造方法と、それを用いた電子機器に関するもので、薄膜トランジスタの生産性を向上することを目的とするものである。

【解決手段】そしてこの目的を達成するために本発明は、基板1と、この基板1上に所定間隔を置いて配置した複数のソース/ドレイン電極2と、これら複数のソース/ドレイン電極2を覆うごとく前記基板1上に設けた半導体層3と、この半導体層3を覆った絶縁層4と、この絶縁層4上で、前記半導体層3のチャネル領域対応部分に設けたゲート電極6とを備え、前記ソース/ドレイン電極2上面と、前記半導体層3のチャネル領域5両側のソース/ドレイン領域8との間には、結晶化誘導金属のシリサイド層9を介在させたものである。

(もっと読む)

電子素子および電子素子の製造方法

電子素子、特にTFT、蓄積コンデンサまたはスタック装置の導電層間の交差部等を備えるものが開示されている。電子素子は、電極を形成する第1の導電層を基板上に備える。第2の導電層により形成された第2の電極は第1の電極から少なくとも誘電体層により隔てられている。この誘電体層は電気絶縁材料の中間層、好ましくは絶縁破壊に対して高い耐性を有する中間層と、光パターニング可能な電気絶縁材料のさらなる層とを包含する。 (もっと読む)

絶縁膜層分離IC製造

【課題】二酸化ケイ素や窒化ケイ素など非常に薄い低応力誘電体材料と半導体層とで

形成された可とう性の膜で集積回路(24、26、28、...30)を製造する汎用手

法を提供する。

【解決手段】膜(36)の半導体層中に半導体デバイス(24、26、28...3

0)を形成する。最初に、標準厚さの基板(18)から半導体膜層(36)を形成し、次

いで、基板の薄い表面層をエッチングまたは研磨する。他のバージョンでは、ボンディン

グされた従来の集積回路ダイ用の支持および電気的相互接続として可とう性膜を使用し、

膜中の複数の層に相互接続部を形成する。1つのそのような膜に複数のダイを接続するこ

とができ、膜は次いでマルチチップ・モジュールとしてパッケージされる。

(もっと読む)

半導体装置

【課題】信頼性の向上した半導体装置及びその作製方法を提供する。

【解決手段】ゲート電極と重畳し、該重畳領域の外側に不純物領域が形成された半導体層と、半導体層のゲート電極が設けられた側と同じ側の面に設けられ、不純物領域と一部が接する第1導電層と、ゲート電極及び第1導電層の上に設けられた絶縁層と、該絶縁層に形成され、第1導電層と少なくとも一部が重畳する開口を介して第1導電層と接する第2導電層と、を有する。

(もっと読む)

61 - 80 / 105

[ Back to top ]