Fターム[5F110DD01]の内容

Fターム[5F110DD01]の下位に属するFターム

ガラス (10,277)

単結晶絶縁物(例;サファイア) (1,234)

シリコン基板 (5,290)

材料の特性が規定 (701)

Fターム[5F110DD01]に分類される特許

2,001 - 2,020 / 5,759

有機トランジスタ

【課題】無機半導体デバイスに比べて簡便なプロセスで素子を作製することが可能であり、かつ長時間安定したトランジスタ特性を示す有機トランジスタを提供する。

【解決手段】有機半導体層が、下式で表される化合物の重合体を含有する有機トランジスタ。

(R1〜R18は、それぞれ独立に、水素原子もしくは1価の有機残基を表し、R1〜R5のうち少なくとも一つは水素原子であり、かつR6〜R10のうち少なくとも一つは水素原子である。)

(もっと読む)

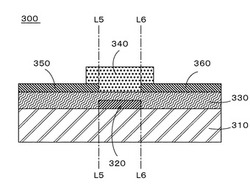

トランジスタ素子の製造方法

【課題】 ゲート電極に対して、ソース・ドレイン電極を正確に位置合わせし、寄生容量の発生を抑制する。

【解決手段】 透明ガラス基板310上に金属からなるゲート電極320を形成し、その上に、透明なゲート絶縁層330を形成し、更に、ソース・ドレイン電極350・360の元になるITOからなる導電層を形成し、その上面をネガ型レジスト層で覆う。ソース・ドレイン形成領域を含む所定領域が透光性を有するマスクを、基板の下面側に配置する。下方から光を照射し、マスクの遮光領域によって生じる影とゲート電極320によって生じる影とが、レジスト層の非露光領域となるような背面露光を行い、パターニングしてソース電極350およびドレイン電極360を形成する。その上に、InGaZnO4からなる酸化物半導体のチャネル層340を直接形成して、高濃度不純物拡散層を省略しつつ、良好なオーミック接触を得る。

(もっと読む)

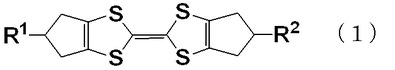

有機半導体および有機薄膜トランジスタ

【課題】安定な薄膜を形成し得るとともに、低しきい電圧駆動の高移動度有機薄膜トランジスタを与え得るテトラチアフルバレン誘導体からなる有機半導体およびこれを用いた有機薄膜トランジスタを提供すること。

【解決手段】式(1)で示されるヘキサメチレンテトラチアフルバレン化合物からなる有機半導体、およびこれから得られる薄膜を備える有機薄膜トランジスタ。

(式中、R1およびR2は、それぞれ独立して、炭素数1〜10の分岐構造を有していてもよいアルキル基を表す。)

(もっと読む)

有機TFTアレイの製造方法

【課題】不要な領域へのインクの漏れ込みを抑えるとともに、インクの密着性を高めることで、優れた特性と高い信頼性を安定して得ることができる有機TFTアレイの製造方法を提供する。

【解決手段】マトリクス状に配列された複数の有機TFTを有する有機TFTアレイの製造方法において、表面が撥液性を有する第1の基板を作成する工程と、下地層の上に複数のソース電極・ドレイン電極がマトリクス状に形成された第2の基板を作成する工程と、第2の基板に形成された複数のソース電極・ドレイン電極で形成される複数のチャネルの間隔と等しい間隔で、第1の基板の表面に有機半導体前駆体溶液を塗布し乾燥させる工程と、有機半導体前駆体溶液が塗布・乾燥された第1の基板と第2の基板とを重ね合わせて、有機半導体前駆体溶液を第2の基板の前記チャネルに転写する工程と、を有する。

(もっと読む)

薄膜トランジスタ基板ならびに液晶表示素子およびその製造方法

【課題】配線や電極等による段差に起因する配向処理むらを抑制し、配向不良の発生を低減でき、充電時間を短くできるTFT基板の提供。

【解決手段】基材2と、基材上に形成されたゲート線と、ゲート絶縁層4と、オーバーコート層6と、ソース線と、画素電極8と、基材2上に形成されゲート線に接続されたゲート電極13、TFT用ゲート絶縁層14、TFT用ゲート絶縁層上に形成された半導体層15、TFT用ゲート絶縁層および半導体層の上に上記オーバーコート層と連続して形成されたTFT用オーバーコート層16、TFT用オーバーコート層上に形成され、ソース線に接続され、半導体層にソース電極用コンタクトホールh1を介して接続されたソース電極17、および、TFT用オーバーコート層上に形成され、画素電極に接続され、半導体層に透明電極用コンタクトホールh2を介して接続された透明電極18を有するTFT10とを有する。

(もっと読む)

透過型液晶表示装置、プロジェクター及びデジタルカメラ

【課題】シフトレジスタ、バッファ回路など駆動回路を同一基板上に組込んだアクティブマトリクス型液晶表示装置において、画素部の開口率を向上させると共に最適なTFTの構成を提供する。

【解決手段】バッファ回路にはゲート電極とオーバーラップするLDDを設けたnチャネル型TFTを形成し、画素部のnチャネル型TFTにはゲート電極とオーバーラップしないLDDを設けた構造とする。画素部に設ける保持容量は、遮光膜と遮光膜上に形成される誘電体膜と画素電極で形成し、特に遮光膜にAlを用い、誘電体膜を陽極酸化法で形成し、酸化Al膜を用いる。

(もっと読む)

配線材料、TFT回路基板、及びターゲット材

【課題】ガラス基板への密着性が高いと共に、Siを含んだ層へのCuの拡散を抑制し、配線とSiを含んだ層とのコンタクト抵抗を低くすることができる配線を提供することができ、また、当該配線材料を用いた回路基板と、当該配線材料用のターゲット材とを提供する。

【解決手段】本発明に係る回路基板用の配線材料は、Cuよりも優先的にSiとの間でシリサイドを形成するシリサイド形成材と、Siの酸化物生成自由エネルギーよりも酸化物生成自由エネルギーが低い少なくとも1種類の添加物とが添加され、残部がCu及び不可避的不純物からなる。

(もっと読む)

薄膜トランジスタ及び画像表示装置

【課題】カラーフィルタ表面の凹凸に起因する、ゲートリーク電流や素子の絶縁破壊を抑制することができる薄膜トランジスタおよび画像表示装置を提供すること。

【解決手段】透明な基板上に形成されたカラーフィルタと、前記カラーフィルタ上に形成されたゲート配線と、前記ゲート配線に離間して形成されたキャパシタ配線と、前記ゲート配線およびキャパシタ配線上に形成された透明なゲート絶縁膜と、前記ゲート絶縁膜上に形成された半導体活性層と、前記ゲート絶縁膜上及び前記半導体活性層上に一部重なって形成されたソース配線と、前記ゲート絶縁膜上及び前記半導体活性層上に一部重なり、前記ソース配線と離間して形成されたドレイン電極とを備え、前記オーバーコート層がくぼみを有し、前記ゲート配線がくぼみ部分に配置されていることを特徴とする薄膜トランジスタとする。

(もっと読む)

炭素ナノチューブ薄膜を利用したSRAM

【課題】炭素ナノチューブ(CNT:Carbon NanoTube)薄膜を利用したSRAMを提供する。

【解決手段】少なくとも第1CNTトランジスタを備える第1CNTインバータと、少なくとも第2CNTトランジスタを備え、第1CNTインバータに連結された第2CNTインバータと、少なくとも第1CNTインバータに連結された第1スイッチングトランジスタと、少なくとも第2CNTインバータに連結された第2スイッチングトランジスタと、を備えるSRAMである。

(もっと読む)

有機トランジスタ

【課題】高い移動度、大きな電流オン/オフ比を有し、保存安定性に優れた有機トランジスタを提供する。

【解決手段】有機半導体層を有する有機トランジスタにおいて、該有機半導体層にポルフィセン誘導体を少なくとも1種含有してなる有機トランジスタ。

(もっと読む)

薄膜トランジスタの作製方法

【課題】絶縁層上に結晶性の高い微結晶半導体層を形成することを課題とする。また、電気特性が良好な薄膜トランジスタを、生産性高く作製する方法を提供することを課題とする。

【解決手段】基板上にゲート電極を形成し、ゲート電極上に、窒素を含む絶縁層を形成する。次に、窒素を含む絶縁層上に、シリコンを含む堆積性気体と、窒素を含む酸化気体と、水素とを用い、プラズマを発生させて、酸化珪素層を形成する。次に、酸化珪素層上に、シリコンまたはゲルマニウムを含む堆積性気体と、水素とを用い、プラズマを発生させて、微結晶半導体層を形成する。

(もっと読む)

縦型論理素子

【課題】狭い面積で高速応答性の縦型半導体装置を提供する。

【解決手段】基板上に形成された第1の電極と、絶縁膜と、絶縁膜を介し第1の電極の側面の一方に形成された第1の導電型の第1の半導体層と、絶縁膜を介し第1の電極の側面の他方に形成された第2の導電型の第2の半導体層と、一部領域における第1の半導体層上に形成された第2の電極と、他の一部領域における第2の半導体層上に形成された第3の電極と、第1の電極の上層の第1の半導体層及び第2の半導体層上に形成された第4の電極とを有し、第2の電極と前記第4の電極間における第1の半導体層に第1のチャネル領域が形成され、第3の電極と前記第4の電極間における第2の半導体層に第2のチャネル領域が形成されるものであることを特徴とする縦型半導体装置を提供することにより上記課題を解決する。

(もっと読む)

トランジスタ素子

【課題】簡易な構成で、ソース電極及びドレイン電極に流れる電流を増大させたトランジスタ素子を提供することを課題とする。

【解決手段】トランジスタ素子10において、波状に凹凸した平面形状を持つ端辺18Aを有するソース電極18と、波状に凹凸した平面形状を持つ端辺20Aを有するドレイン電極20とが、間隔を持って隔てられ、且つ互いの波状に凹凸した平面形状を持つ端辺18A,20Aを対向させて配設させている。

(もっと読む)

アクティブ素子基板の製造方法、アクティブ素子基板、アクティブ型表示装置

【課題】工数の増加を伴うことなく、寄生容量を抑制できるとともに、高開口率および高透過率を示すアクティブ素子基板の製造方法を実現する。

【解決手段】画素TFT7および信号配線上に、コンタクトホール9a・10aを有する透明な絶縁層9・10を形成する工程を備え、該工程は、画素TFT7および信号配線を覆うように、感光性を有さない第1の絶縁層9を形成する工程と、第1の絶縁層9を覆うように、感光性を有する第2の絶縁層10を形成する工程と、第2の絶縁層10を露光および現像により、パターニングする工程と、第2の絶縁層10をマスクとして上記第1の絶縁層9をエッチングする工程とを含む。

(もっと読む)

酸化物半導体を有する電界効果トランジスタの製造方法

【課題】ゲート電極とソース・ドレイン電極の合わせ精度がよく、安価に透明デバイスを実現できる電界効果トランジスタの製造方法を提供する。

【解決手段】パターニングされた遮光膜102を基板101裏面側に形成し、基板表面側に形成されるゲート電極103およびソース・ドレイン電極108のパターン形成用のフォトマスクとして共用することにより、フォトマスク数が低減されると共に、ゲート電極とソース・ドレイン電極の位置合わせが自己整合的に行われるため互いの合わせ精度が向上する。これにより、高精度で低コストな電界効果トランジスタの製造方法が提供できる。

(もっと読む)

液晶表示装置及びその製造方法

【課題】表示欠陥を完全にリペアすることができ、開口率の低下を伴わない液晶表示装置の製造方法を提供する。

【解決手段】紫外線の照射によって高導電率化されたIn、Ga及びZnを含むアモルファス酸化物のソース領域及びドレイン領域を有する主TFT及び冗長TFTを備え、冗長TFTの透明なドレイン領域を画素電極と重なり合うようにして信号線に設けられたリペア領域にまで延ばして形成する。リペア領域と冗長TFTのドレイン領域の端部とは絶縁層によって絶縁されている。表示欠陥の生じた画素部に対して、主TFTを画素電極から切り離すとともに、冗長TFTのドレイン領域の端部と信号線とをリペア領域において溶着させる。これにより、冗長TFTがスイッチング素子として機能し表示欠陥が完全にリペアされる。

(もっと読む)

半導体装置の作製方法

【課題】 レジスト材料の利用効率を向上させて、作製コストの削減を目的としたレジス

トパターンの作製方法、レジストパターンの除去方法、半導体装置の作製方法を提供する

ことを課題とする。

【解決手段】 本発明は、減圧下で、被加工物上に、感光剤を含む組成物を吐出してレジ

ストパターンを形成するステップを有することを特徴とする。また、前記レジストパター

ンをマスクとして前記被加工物をエッチングするステップ、若しくは、前記レジストパタ

ーンに、フォトマスクを介して前記感光剤の感光波長域の光を照射するステップ、前記レ

ジストパターンをマスクとして前記被加工物をエッチングするステップ、前記被加工物上

の前記レジストパターンを除去するステップを有することを特徴とする。

(もっと読む)

半導体素子の製造方法

【課題】欠陥が低減され膜質が良好なゲート酸化膜を有する半導体素子を製造する。

【解決手段】基板2のフィールド領域の表面にフィールド酸化膜4を形成する工程と、フィールド酸化膜4を形成した基板2の第1アクティブ領域および第2アクティブ領域の表面に第1ゲート酸化膜11A,11Bを形成する工程と、第1ゲート酸化膜11A,11Bに第1純水ヒーリングを施す工程と、第2アクティブ領域における第1ゲート酸化膜11Bを除去する工程と、第1アクティブ領域および第2アクティブ領域の表面に第2ゲート酸化膜12A,12Bを形成する工程と、第2ゲート酸化膜12A,12Bに第2純水ヒーリングを施す工程と、第1アクティブ領域および第2アクティブ領域における第2ゲート酸化膜12A,12B上にゲート電極8を形成する工程と、をこの順に有する半導体素子の製造方法。

(もっと読む)

SOI基板の作製方法及び半導体装置の作製方法

【課題】ガラス基板など耐熱温度が低い基板を用いた場合にも、実用に耐えうる単結晶半導体層を備えた半導体基板の製造方法を提供する。

【解決手段】単結晶半導体基板上に酸化膜を形成し、酸化膜を介して半導体基板に加速されたイオンを照射することにより、半導体基板中に脆化領域を形成し、酸化膜を間に挟んで単結晶半導体基板と向かい合うように支持基板を貼り合わせ、単結晶半導体基板を加熱することにより、脆化領域において、単結晶半導体層が貼り合わされた支持基板と単結晶半導体基板の一部とに分離し、支持基板に貼り合わされた単結晶半導体層の表面に対して、基板バイアスを印加して第1のエッチングを行い、単結晶半導体層に対してレーザビームを照射して、単結晶半導体層の少なくとも表面の一部を溶融した後、凝固させ、単結晶半導体層の表面に対して、基板バイアスを印加することなく第2のエッチングを行う。

(もっと読む)

スイッチング素子の製造方法

【課題】逆スタガ型TFT素子のゲート電極に含有される水素の量は、当該金属を用いたTFT素子のゲート絶縁層の特性に影響を与える。例えばゲート電極中の水素量を増加させるとTFT素子の絶縁抵抗値を高くでき好適である。反面水素が過剰量入るとTFT素子外に水素が時間と共に飛散し、TFT素子の電気特性が不安定になる。そして、水素量はゲート酸化に伴い掃き寄せられるようにゲート電極内の水素濃度を上昇させるため、絶縁層の層厚により、TFT素子の性能が変わってしまうという課題がある。

【解決手段】ゲート電極102を酸化して得られるゲート絶縁層103の厚みを補正してゲート電極102の水素量を調整する。ゲート電極102中の水素濃度はゲート絶縁層103の厚みによらず一定に保たれることから、絶縁抵抗値が高く、かつ水素の飛散を抑えた信頼性が高いTFT素子を得ることが可能となった。

(もっと読む)

2,001 - 2,020 / 5,759

[ Back to top ]