Fターム[5F110DD14]の内容

Fターム[5F110DD14]に分類される特許

2,001 - 2,020 / 2,817

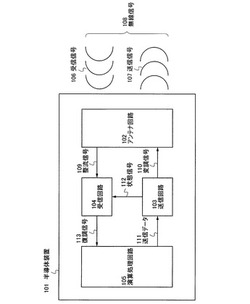

半導体装置

【課題】半導体装置とリーダ/ライタとの通信方式にASK方式を用いる場合、リーダ/ライタから半導体装置へデータを送信していない場合に、半導体装置からリーダ/ライタへ送信したデータにより、無線信号の振幅が変化する。したがって、半導体装置が送信したデータを、リーダ/ライタから送信されたデータと誤って認識する場合がある。

【解決手段】半導体装置を、アンテナ回路と、送信回路と、受信回路と、演算処理回路と、から構成する。アンテナ回路において、無線信号を送受信する。また、送信回路は、アンテナ回路が無線信号を送信中か否かを示す信号を受信回路に出力する

(もっと読む)

表示装置及び表示装置の作製方法

【課題】視認性の優れた高画質な表示機能を有する信頼性の高い表示装置を提供することを目的とする。またそのような表示装置を工程、装置を複雑化することなく、高い信頼性を付与して作製することができる技術を提供することを目的とする。

【解決手段】発光素子と電気的に接続し、発光素子を駆動させる薄膜トランジスタとして、pチャネル型薄膜トランジスタを用いる場合、そのpチャネル型薄膜トランジスタのカットオフ電流を駆動回路のpチャネル型薄膜トランジスタより低くする。具体的には表示装置の構成する薄膜トランジスタの半導体層に対して選択的にチャネルドープを行う。

(もっと読む)

半導体装置とその作製方法

【課題】無線通信により交信可能な半導体装置において、個体識別子を容易に付けることができるようにする。また信頼性の高い半導体装置を提供する。

【解決手段】チャネル形成領域と、ソース領域またはドレイン領域を有する島状半導体膜131〜134と、ゲート絶縁膜と、ゲート電極103〜106とを有する薄膜トランジスタ118〜121と、層間絶縁膜と、層間絶縁膜中に形成され、ソース領域またはドレイン領域の一方に達する複数のコンタクトホール142を含む第1のコンタクトホールと、ソース領域またはドレイン領域の他方に達する第2のコンタクトホール141とを有し、第2のコンタクトホール141の径は、第1のコンタクトホールに含まれる複数のコンタクトホール142のそれぞれの径より大きく、第1のコンタクトホール142の底面積の合計と、第2のコンタクトホール141の底面積は等しい半導体装置に関するものである。

(もっと読む)

クロック同期回路及びそれを備えた半導体装置

【課題】複数の回路間で異なるクロックを使用した場合であっても、安定した通信が可能であるクロック同期回路及びそれを備えた半導体装置の提供を課題とする。

【解決手段】受信したデータの変化点を検出し、リセット信号を出力する手段と、クロック信号を出力する基準クロック発生回路と、クロック信号をカウントする基準クロックカウンター回路と、基準クロックカウンター回路から出力された信号を分周する分周回路と、分周回路から出力された信号により回路動作用基準クロック信号を出力する手段とを設ける。

(もっと読む)

表示装置とその製造方法

【課題】シリコンなどの半導体膜に連続発振レーザを走査しながら照射して帯状の擬似単結晶を連続かつ方向制御して成長させる際の溶融半導体の凝集を抑制して、高性能の薄膜トランジスタを用いたシステムインパネル方式の表示装置を得る。

【解決手段】絶縁基板101の上に形成されたシリコン窒化膜102と、シリコン窒化膜の上に形成されたシリコン酸化膜103と、シリコン酸化膜103の上に形成された半導体膜104と、半導体膜104を用いた薄膜トランジスタとを有する。シリコン酸化膜103を、SiH4とN2Oとを原料ガスとして成膜した第1のシリコン酸化膜と、TEOSガスを原料ガスとして成膜した第2のシリコン酸化膜とで構成し、前記半導体膜を、結晶粒が帯状の形状を有する擬似単結晶とする。

(もっと読む)

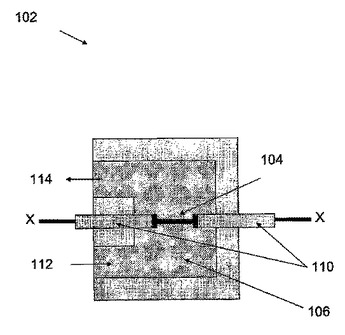

ナノワイヤセンサ、ナノワイヤセンサアレイ、及び当該センサ及びセンサアレイを形成する方法

支持基板の上にナノワイヤを含むセンサであって、第1半導体層が該支持基板上に配置されたセンサ、を形成する方法が開示されている。該方法は、第1半導体層からなり、かつ少なくとも2つの支持部と、該支持部の間に配置されるフィン部と、を含むフィン構造を形成する工程と;フィン構造の少なくともフィン部を酸化することにより第1酸化膜層によって取り囲まれるナノワイヤを形成する工程と;絶縁層を該支持部の上に形成する工程と、を含み、支持部及び第1絶縁層はマイクロ流体チャネルを構成する。ナノワイヤセンサも開示されている。ナノワイヤセンサは、支持基板と;支持基板の上に配置され、かつ少なくとも2つの半導体支持部と、該支持部の間に配置されるフィン部と、を含む半導体フィン構造と;支持部のコンタクト表面の上の第1絶縁層と、を備え、支持部及び第1絶縁層はマイクロ流体チャネルを構成する。  (もっと読む)

(もっと読む)

半導体装置

【課題】 本発明は、同一基板上に同時に異なるLDD構造を有する生産性の高いTFTの作製方法およびその構造を提供することを目的としている。即ち、本発明はTFTの新規な構造と生産性の高い製造工程を提供するものである。

【解決手段】 耐熱性の高いTa膜またはTaを主成分とする膜を配線材料に用い、さらに保護層で覆うことで、高温(400〜700℃)での加熱処理を施すことが可能となり、且つ保護層をエッチングストッパーとして用いることで周辺駆動回路部においては、サイドウォール126を用いた自己整合プロセス(セルフアライン)によるLDD構造を備えたTFTを配置する一方、画素マトリクス部においては、絶縁物125を用いた非自己整合プロセス(ノンセルフアライン)によるLDD構造を備えたTFTを配置する

(もっと読む)

半導体装置を内包する用紙およびその作製方法

【課題】無線で通信可能な半導体装置を抄き込んだ用紙であり、半導体装置を内包する部分の凹凸が目立たなく、しかも厚さ130μm以下の薄い紙を実現する。

【解決手段】半導体装置1は回路部12とアンテナ11を具備し、回路部12は薄膜トランジスタで構成される。回路部12とアンテナ11は製造時に使用した基板から分離され、可撓性基材13と封止層14とで挟まれ保護されている。半導体装置1は撓ませることが可能であり、半導体装置1自体の厚みは30μm以下である。半導体装置1は紙2の抄紙工程で抄き込まれる。

(もっと読む)

表示装置の作製方法

【課題】材料の利用効率を向上させ、かつ、作製工程を簡略化して作製可能な表示装置及びその作製技術を提供することを目的とする。また、それらの表示装置を構成する配線等のパターンを、所望の形状で制御性よく形成できる技術を提供することも目的とする。

【解決手段】マスク層を形成する際、形成したいパターンの外側(パターンの輪郭、端部に相当する)に液状のマスク層形成材料を含む組成物を付着させ、枠状の第1のマスク層を形成する。枠状の第1のマスク層の内側の空間を充填するように、液状の第2のマスク層形成材料を含む組成物を付着させ第2のマスク層を形成する。第1のマスク層及び第2のマスク層は接して形成され、第2のマスク層の周囲を囲むように第1のマスク層が形成されるので、第1のマスク層及び第2のマスク層は連続した一つのマスク層として用いることができる。

(もっと読む)

表示装置の作製方法

【課題】材料の利用効率を向上させ、かつ、作製工程を簡略化して作製可能な表示装置及びその作製技術を提供することを目的とする。また、それらの表示装置を構成する配線等のパターンを、所望の形状で制御性よく形成できる技術を提供することも目的とする。

【解決手段】導電層を形成する際、形成したいパターンの外側(パターンの輪郭、端部に相当する)に液状の導電性材料を含む組成物を付着させ、枠状の第1の導電層(又は絶縁層)を形成する。枠状の第1の導電層の内側の空間を充填するように、液状の第2の導電性材料を含む組成物を付着させ第2の導電層を形成する。第1の導電層及び第2の導電層は接して形成され、第2の導電層の周囲を囲むように第1の導電層が形成されるので、第1の導電層及び第2の導電層は連続した一つの導電層として用いることができる。

(もっと読む)

薄膜半導体装置、ラテラルバイポーラ薄膜トランジスタ、ハイブリッド薄膜トランジスタ、MOS薄膜トランジス、及び薄膜トランジスタの製造方法

【課題】ガラス基板上にMOSトランジスタと、バイポーラトランジスタを同時に集積できる素子構造および製法を提供する。

【解決手段】絶縁基板(101)上に形成された半導体薄膜(105)に形成されたエミッタ(102)、ベース(103)、およびコレクタ(104)を有するラテラルバイポーラトランジスタ(100)において、半導体薄膜(105)が所定の方向に結晶化された半導体薄膜であるラテラルバイポーラトランジスタ。また、絶縁基板上に形成された半導体薄膜に形成されたMOS−バイポーラハイブリッドトランジスタ(200)において、半導体薄膜(205)は所定の方向に結晶化された半導体薄膜であるMOS−バイポーラハイブリッドトランジスタ。

(もっと読む)

薄膜トランジスタ基板及びその製造方法

【課題】基板としてプラスチック基板を用いた薄膜トランジスタ基板の製造工程中で用いられるレジスト膜を除去する際に、プラスチック基板に化学的なダメージを与えない層構成を有した薄膜トランジスタ基板及びその製造方法を提供する。

【解決手段】酸素プラズマ耐性のある無機層11が全面に形成されたプラスチック基板10を準備する工程と、無機層11上に半導体膜を形成する工程と、半導体膜上にレジスト膜をパターニングする工程とを有し、レジスト膜の除去工程がプラズマアッシング法により行われる方法により薄膜トランジスタ基板を製造する。このとき、無機層が、クロム、チタン、アルミニウム、シリコン、酸化クロム、酸化チタン、酸化アルミニウム、窒化アルミニウム、酸窒化アルミニウム、酸化シリコン、窒化シリコン、及び酸窒化シリコンの群から選択されるいずれかからなることが好ましい。

(もっと読む)

電気光学装置及びその製造方法、並びに電子機器

【課題】電気光学装置において、画素スイッチング用のTFTの性能を向上させると共に遮光性を高める。

【解決手段】電気光学装置は、基板(10)上に、データ線(6a)及び走査線(11a)と、データ線及び走査線の交差に対応して設けられた画素電極(9a)と、画素電極に接続されており、チャネル領域(1a´)とソース領域(1d)との間に形成された第1のLDD領域(1b)と、チャネル領域とドレイン領域(1e)との間に形成された第2のLDD領域(1c)とを有する半導体層(1a)、及びチャネル領域に重なるゲート電極(3a)を有するトランジスタ(30)とを備える。更に、ゲート電極と、絶縁膜(41a)を介して互いに異なる層に配置されており、第1及び第2のLDD領域と少なくとも部分的に重なるように形成されると共にゲート電極と電気的に接続された第1遮光部(11a)を備える。

(もっと読む)

画素と駆動領域の異なる電気特性を有する薄膜トランジスタデバイスを有するディスプレイ、およびその製造方法

【課題】 駆動領域と画素領域のTFTが異なる特性、特に、電子移動度と、または漏れ特性を有する駆動回路と画素領域の全体的なTFT構造を提供する。

【解決手段】 薄膜トランジスタデバイスを含む画像表示システムであって、駆動回路領域と画素領域を含む基板、駆動回路領域と画素領域の基板の上にそれぞれ設置され、チャネル領域、ソース/ドレイン領域と、その間に形成された軽ドープ領域を含む第1と第2活性層、および第1と第2活性層の上にそれぞれ設置され、堆積された第1と第2ゲート誘電体層とゲート長を有するゲート層を含み、第2ゲート誘電体層が第1ゲート誘電体層より短い長さを有するが、ゲート層の前記ゲート長より長い2つのゲート構造を含み、第1活性層の軽ドープ領域は、第2活性層と異なる長さを有するシステム。

(もっと読む)

薄膜トランジスタ基板、及びその製造方法

【課題】新たな工程を追加することなく、サブスレッショルド特性におけるハンプ特性を抑制する薄膜トランジスタを提供する。

【解決手段】第1の導電型の薄膜トランジスタを有する薄膜トランジスタ基板であって、ソース/ドレイン領域31間に配置された第1の導電型のチャネル領域32を有する半導体層3と、ゲート絶縁膜5を介して半導体層3の対面側に形成されるゲート電極6を有し、チャネル領域32のチャネル幅方向の両端部4に対応するゲート電極6に開口部61を有し、開口部61に対応するチャネル領域4では、ゲート電極6に対応するチャネル領域よりも第1の導電型の不純物濃度が高い高濃度不純物領域が形成されている薄膜トランジスタ基板。

(もっと読む)

電子デバイスが形成されたフレキシブル基板

電子デバイス(10)の製造方法は、プラスチック材料を有する基板(20)を用意する。微粒子材料(16)は基板の少なくとも1つの表面内に埋め込まれる。薄膜半導体材料の層は基板(20)上に堆積される。  (もっと読む)

(もっと読む)

薄膜トランジスタ、その製造方法、半導体装置及び表示装置

【課題】寄生トランジスタの発生を抑制することができ、高性能化を図ることができ、かつゲート絶縁耐圧劣化を抑制することで高信頼性を得ることができる薄膜トランジスタ、その製造方法、半導体装置及び表示装置を提供する。

【解決手段】ゲート絶縁膜を挟んで半導体層とゲート電極とが交差配置された構造を有する薄膜トランジスタであって、上記半導体層は、チャネル部の端部が傾斜しており、上記ゲート絶縁膜は、チャネル部の端部と重なる部分の酸化シリコン換算膜厚が、チャネル部の中央部と重なる部分の酸化シリコン換算膜厚よりも大きい薄膜トランジスタ。

(もっと読む)

液晶表示装置及びその製造方法

【課題】開口率を向上させると共に補助容量を大きくした液晶表示装置を提供する。

【解決手段】第1の基板10Aに有するアクティブ素子の上層に形成されたゲート絶縁膜12B、ゲート電極2、層間絶縁膜12C、映像線Dとソース電極4とをこの順で積層する。層間絶縁膜12Cは高誘電体微粒子またはゾルゲルを少なくとも含む比誘電率4.0以上の塗布型透明絶縁膜で形成される。ゲート絶縁膜12Bに第1のスルーホールSH3を有し、第1のスルーホールSH3内の層間絶縁膜12Cに第2のスルーホールSH4を形成し、ソース電極4を第2のスルーホールSH4を介してアクティブ素子に電気的に接続し、ゲート電極2と映像線Dとソース電極4および層間絶縁膜12Cで保持容量を構成する。

(もっと読む)

表示装置の製造方法

【課題】SELAX法による帯状シリコン結晶を形成する際のシリコン溶融時間を短縮して結晶性を向上させ、シリコン膜を用いた薄膜トランジスタの動作特性を改善して高精細な表示装置を得る。

【解決手段】薄膜トランジスタを構成するための半導体膜を成膜した絶縁基板505を冷却しながら、この半導体膜に連続発振レーザ501を走査しながら照射し、結晶粒の長手方向が走査方向に長い帯状半導体結晶503に成長させる。

(もっと読む)

薄膜トランジスタ装置およびその製造方法

【課題】P型薄膜トランジスタの閾値電圧の制御が容易なアレイ基板を提供する。

【解決手段】P型用ゲート電極27に用いる金属材料の抵抗値より抵抗値が小さな金属材料をN型用ゲート電極25およびゲート配線26に用いる。N型用ゲート電極25およびゲート配線26にアルミニウム系材料を用い、P型用ゲート電極27にモリブデン系やタングステン系の材料を用いる。ゲート配線26にアルミニウム系の比較的抵抗値が小さな低抵抗材料を用いることができる。P型用ゲート電極27にアルミニウム系の材料を用いなくて済む。P型薄膜トランジスタ6の閾値電圧が変動しにくくなる。

(もっと読む)

2,001 - 2,020 / 2,817

[ Back to top ]