Fターム[5F110FF36]の内容

Fターム[5F110FF36]に分類される特許

81 - 100 / 1,159

半導体装置

【課題】緻密で高耐圧な絶縁膜を提供することを目的とする。

【解決手段】基板上に半導体膜を有し、半導体膜上に第1の絶縁膜を有し、第1の絶縁膜上に導電膜を有し、導電膜上に第2の絶縁膜を有し、第1の絶縁膜は、第2の絶縁膜よりも緻密であり、第1の絶縁膜は、珪素と、酸素と、窒素とを有する。第1の絶縁膜は、希ガスを有し、その膜厚は、1nm以上100nm以下である。このような第1の絶縁膜はゲート絶縁膜として機能させる。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】酸化物半導体を用いたトランジスタにおいて、電気的特性の変動が小さく、信頼

性の高い半導体装置を作製することを課題とする。

【解決手段】チャネルを形成する酸化物半導体層に接する絶縁層に、シリコン過酸化ラジ

カルを含む絶縁層を用いる。絶縁層から酸素が放出されることにより、酸化物半導体層中

の酸素欠損及び絶縁層と酸化物半導体層の界面準位を低減することができ、電気的特性の

変動が小さく、信頼性の高い半導体装置を作製することができる。

(もっと読む)

半導体装置

【課題】高速動作、低消費電力である半導体装置の提供。

【解決手段】結晶性のシリコンをチャネル形成領域に有する第1のトランジスタを用いた記憶素子と、当該記憶素子のデータを記憶する容量素子と、当該容量素子における電荷の供給、保持、放出を制御するためのスイッチング素子である第2のトランジスタとを有する。第2のトランジスタは第1のトランジスタを覆う絶縁膜上に位置する。第1及び第2のトランジスタは、ソース電極又はドレイン電極を共有している。上記絶縁膜は、加熱により一部の酸素が脱離する第1の酸化絶縁膜と、酸素の拡散を防ぎ、なおかつ当該第1の酸化絶縁膜の周囲に設けられた第2の酸化絶縁膜とを有し、第2のトランジスタが有する酸化物半導体膜は、上記第1の酸化絶縁膜に接し、かつチャネル形成領域である第1の領域と、第1の領域を挟み、第1及び第2の酸化絶縁膜に接する一対の第2の領域とを有する半導体装置。

(もっと読む)

半導体装置

【課題】作製コストが低減され、かつ歩留まりが向上された半導体装置、および消費電力が低減された半導体装置を提供することである。

【解決手段】第1のトランジスタおよび第2のトランジスタと、第1のトランジスタ群および第2のトランジスタ群を具備し、第1のトランジスタ群は、第3のトランジスタ、第4のトランジスタおよび4の端子を有しており、第2のトランジスタ群は、第5乃至第8のトランジスタおよび4の端子を有しており、第1のトランジスタ、第3のトランジスタ、第6のトランジスタ、第8のトランジスタはnチャネル型トランジスタが用いられ、第2のトランジスタ、第4のトランジスタ、第5のトランジスタ、第7のトランジスタはpチャネル型トランジスタが用いられる半導体装置である。

(もっと読む)

有機電子デバイス用組成物、有機電子デバイスの作製方法、有機電子デバイス及び電界効果トランジスタ

【課題】電荷輸送性や移動度が高く、安定性に優れた有機半導体層、及びOn/Off比が高い有機電子デバイスを得る。また、この有機電子デバイスを低コストに製造する。

【解決手段】特定構造の有機半導体化合物と特定の有機化合物とを含有する有機電子デバイス用組成物を用いる。具体的には、有機半導体化合物として、アヌレン構造を有する有機化合物を用い、特定の有機化合物として、下記一般式(1)若しくは(2)で表わされる部分構造を有する有機化合物、又は、ウレア結合、チオウレア結合、ホスフィンオキシド結合、ホスフィンスルフィド結合、スルフォキシド結合若しくはスルホン結合を有する有機化合物を用いる。

(式(1)〜(2)中、Xは、酸素原子又は硫黄原子を示し、Zは硫黄原子又はリン原子を示す。nは、1又は2を示し、nが2である場合の2つのXは酸素原子を示す。X及びZがどちらも硫黄原子であることはない。)

(もっと読む)

信号処理回路及びその駆動方法

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる信号処理回路の提供する。

【解決手段】入力された信号の位相を反転させて出力する論理素子を2つ(第1の位相反転素子及び第2の位相反転素子)と、第1の選択トランジスタと、第2の選択トランジスタと、を有する記憶素子であって、酸化物半導体層にチャネルが形成されるトランジスタと容量素子との組を2つ(第1のトランジスタと第1の容量素子との組、及び第2のトランジスタと第2の容量素子との組)有する。そして、信号処理回路が有する記憶装置に上記記憶素子を用いる。例えば、信号処理回路が有するレジスタ、キャッシュメモリ等の記憶装置に上記記憶素子を用いる。

(もっと読む)

半導体装置

【課題】導体半導体接合を用いて、優れた特性を示す、あるいは、作製の簡単な、あるいは、より集積度の高い電界効果トランジスタを提供する。

【解決手段】半導体層の電子親和力よりも仕事関数の小さな導体との接合においては、導体より半導体層にキャリアが注入された領域が生じる。そのような領域を電界効果トランジスタ(FET)のオフセット領域、あるいは、インバータ等の半導体回路の抵抗として用いる。また、ひとつの半導体層中にこれらを設けることにより集積化した半導体装置を作製できる。

(もっと読む)

光及び熱エネルギー架橋性有機薄膜トランジスタ絶縁層材料

【課題】閾値電圧の絶対値及びヒステリシスが小さい有機薄膜トランジスタを製造しうる有機薄膜トランジスタ絶縁層材料を提供すること。

【解決手段】(A)分子内にビニルオキシ基を含有する低分子化合物及び/又は分子内にビニルオキシ基及び活性水素と反応しうる第2の官能基を電磁波の照射もしくは熱の作用により生成しうる第1の官能基を含有する高分子化合物と、(B)分子内にN−マレオイルアミノ基を含含有する低分子化合物及び/又は分子内にN−マレオイルアミノ基及び活性水素と反応しうる第2の官能基を電磁波の照射もしくは熱の作用により生成しうる第1の官能基を含有する高分子化合物とを、含有し、前記2種類の高分子化合物のうちの少なくとも一方の高分子化合物を含有する有機薄膜トランジスタ絶縁層材料。

(もっと読む)

半導体装置、表示装置

【課題】グローバルシャッタ方式で電荷の蓄積を行うイメージセンサにおいて、蓄積期間

終了時から最後の行を読み出すまでの期間、蓄積電荷保持部からの電荷の流出を極力抑制

することのできる半導体装置の提供を目的とする。

【解決手段】画素がマトリクス状に複数配置されたCMOSセンサ型のイメージセンサに

おいて、画素部の電荷蓄積制御トランジスタ及びリセットトランジスタにチャネル形成領

域が酸化物半導体で形成されたトランジスタを使用し、マトリクス状に配置された全ての

画素で信号電荷蓄積部のリセット動作を行った後、全ての画素でフォトダイオードによる

電荷の蓄積動作を行い、行毎に画素から信号の読み出し動作を行うことで歪みの無い撮像

を可能とする。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体を用いたトランジスタ(より広義には、十分にオフ電流が小さいトランジスタ)を用いた記憶回路と、酸化物半導体以外の材料を用いたトランジスタ(換言すると、十分な高速動作が可能なトランジスタ)を用いた駆動回路などの周辺回路と、を一体に備える半導体装置とする。また、周辺回路を下部に設け、記憶回路を上部に設けることで、半導体装置の面積の縮小化及び小型化を実現することができる。

(もっと読む)

記憶回路

【課題】短時間の電源停止により消費電力を抑えることができ、電源再開時において誤動作を引き起こすことなく初期化することのできる信号処理装置の記憶回路の提供を目的の一つとする。

【解決手段】記憶回路に電源が供給されない間は、揮発性記憶部に記憶していたデータ信号を、不揮発性記憶部に保持する。不揮発性記憶部では、オフ電流が極めて小さいトランジスタを用いることによって、容量素子に保持されたデータ信号は長期間にわたり保持する。こうして、不揮発性記憶部は電源の供給が停止した間も論理状態を保持する。また電源停止時に容量素子で保持されたデータ信号は、電源再開時にはリセット回路を導通状態とすることで、誤動作を引き起こすことのない電位にする。

(もっと読む)

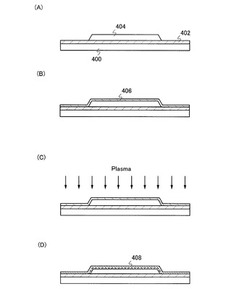

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化す

ることを目的の一とする。

【解決手段】第1の絶縁膜を形成し、第1の絶縁膜に酸素ドープ処理を行って、第1の絶

縁膜に酸素原子を供給し、第1の絶縁膜上に、ソース電極およびドレイン電極、ならびに

、ソース電極およびドレイン電極と電気的に接続する酸化物半導体膜を形成し、酸化物半

導体膜に熱処理を行って、酸化物半導体膜中の水素原子を除去し、水素原子が除去された

酸化物半導体膜上に、第2の絶縁膜を形成し、第2の絶縁膜上の酸化物半導体膜と重畳す

る領域にゲート電極を形成する半導体装置の作製方法である。

(もっと読む)

薄膜トランジスタ

【課題】高い電界効果移動度を有する薄膜トランジスタを提供する。

【解決手段】希ガス及び水分子を含有する混合気体雰囲気下で酸化物半導体材料を成膜してなるチャネル層を備える薄膜トランジスタであって、前記酸化物半導体材料がIn原子及びZn原子を含む酸化物であり、原子比Zn/(In+Zn)が10原子%以上20原子%未満である薄膜トランジスタ。

(もっと読む)

記憶回路、電子機器

【課題】新たな構成の不揮発性の記憶回路を提供する。

【解決手段】第1の記憶回路と、第2の記憶回路と、第1のスイッチと、第2のスイッチと、位相反転回路と、を有し、第1の記憶回路は、酸化物半導体膜により形成された第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、容量素子と、を有する。酸化物半導体膜により形成された第1のトランジスタと、容量素子と、を用い不揮発性の記憶回路を構成する。また、記憶回路に接続する電源線、及び信号線を少なくし、当該記憶回路に用いるトランジスタ数を減少させることで、回路規模の小さい不揮発性の記憶回路を実現することができる。

(もっと読む)

記憶装置及び半導体装置

【課題】データの保持期間を確保しつつ、単位面積あたりの記憶容量を高めることができる記憶装置を提供する。

【解決手段】複数のビット線を幾つかのグループに分割し、複数のワード線も幾つかのグループに分割する。そして、一のグループに属するビット線に接続されたメモリセルには、一のグループに属するワード線が接続されるようにする。さらに、複数のビット線は、複数のビット線駆動回路102a,102b,102cによってグループごとにその駆動が制御されるようにする。加えて、複数のビット線駆動回路102a,102b,102cと、ワード線駆動回路101とを含めた駆動回路上に、セルアレイ103a,103b,103cを形成する。駆動回路とセルアレイ103a,103b,103cが重なるように三次元化することで、ビット線駆動回路が複数設けられていても、記憶装置の占有面積を小さくすることができる。

(もっと読む)

記憶装置

【課題】回路面積を小さくする。

【解決手段】記憶データとしてデータを記憶するメモリセルと、出力信号線と、電圧が与えられる配線と、を具備し、メモリセルは、記憶データと検索データの比較演算を行い、演算結果に応じて導通状態又は非導通状態になる比較回路と、記憶データの書き込み及び保持を制御する電界効果トランジスタと、を備え、比較回路が導通状態のときに、出力信号線の電圧値が配線の電圧と同等の値になる記憶装置。

(もっと読む)

半導体記憶装置およびその作製方法

【課題】電力の供給がない状況でもデータの保持が可能、かつ書き込み回数にも制限がない、新たな構造の半導体記憶装置を提供する。また、単位面積あたりの記憶容量を増加させる。

【解決手段】一対の電極と、一対の電極の側壁と接して設けられた絶縁膜と、該絶縁膜を介して一対の電極間に設けられ、一対の電極の上面の高さよりも上面の高さの低い第1のゲート電極と、第1のゲート電極上に設けられた第1のゲート絶縁膜と、第1のゲート絶縁膜および一対の電極と接して設けられた酸化物半導体膜と、少なくとも酸化物半導体膜上に設けられた第2のゲート絶縁膜と、第2のゲート絶縁膜を介して酸化物半導体膜上に設けられた第2のゲート電極と、を有する第1のトランジスタと、一対の電極の一方を介して第1のトランジスタと接続されるキャパシタと、を有し、該キャパシタに保持される電位に応じてデータが記憶されるメモリセルからなる半導体記憶装置である。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。また、新たな構造の半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させる。

【解決手段】多値書き込みを行う半導体装置、及び半導体装置の駆動方法において、酸化物半導体層を含むトランジスタを用いたメモリセルに書き込みを行う書き込みトランジスタのオンオフを制御する信号線を、ビット線に沿うように配置し、読み出し動作時に容量素子に与える電圧を書き込み時にも利用して、多値書き込みを行う。トランジスタのオフ電流を十分に小さくすることができるワイドギャップ半導体である酸化物半導体材料を用いることで、長期間にわたって情報を保持することが可能である。

(もっと読む)

半導体装置

【課題】電源をオフしてもデータを保持することができ、退避動作と復帰動作が不要なレジスタ回路を提供する。

【解決手段】複数のレジスタ構成回路と、オフ電流が小さい第1のトランジスタと、オフ電流が小さい第2のトランジスタと、を有するレジスタ回路において、データ保持部を前記第1のトランジスタのソース及びドレインの一方に接続し、前記第2のトランジスタのソース及びドレインの一方に接続する。前記第1のトランジスタ及び前記第2のトランジスタはオフ電流が小さいので、データ保持部の電荷がリークせず、レジスタ回路の電源をオフしてもデータ保持部にデータが保持される。そのため、退避動作と復帰動作を行わなくてよい。

(もっと読む)

記憶素子、信号処理回路

【課題】新たな構成の不揮発性の記憶素子、それを用いた信号処理回路を提供する。

【解決手段】第1の回路と第2の回路とを有し、第1の回路は第1のトランジスタと第2のトランジスタとを有し、第2の回路は第3のトランジスタと第4のトランジスタとを有する。第1の信号に対応する信号電位は、オン状態とした第1のトランジスタを介して第2のトランジスタのゲートに入力され、第2の信号に対応する信号電位は、オン状態とした第3のトランジスタを介して第4のトランジスタのゲートに入力される。その後、第1のトランジスタ及び第3のトランジスタをオフ状態とする。第2のトランジスタの状態と第4のトランジスタの状態との両方を用いて、第1の信号を読み出す。第1のトランジスタ及び第3のトランジスタは、チャネルが酸化物半導体層に形成されるトランジスタとする。

(もっと読む)

81 - 100 / 1,159

[ Back to top ]