Fターム[5F110FF36]の内容

Fターム[5F110FF36]に分類される特許

121 - 140 / 1,159

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】ワイドギャップ半導体、例えば酸化物半導体を含むメモリセルを用いて構成された半導体装置であって、メモリセルからの読み出しのために基準電位より低い電位を出力する機能を有する電位切り替え回路を備えた半導体装置とする。ワイドギャップ半導体を用いることで、メモリセルを構成するトランジスタのオフ電流を十分に小さくすることができ、長期間にわたって情報を保持することが可能な半導体装置を提供することができる。

(もっと読む)

半導体記憶装置

【課題】電源電圧の供給の停止及び再開を行う構成において、揮発性の記憶装置と不揮発性の記憶装置との間のデータの退避及び復帰の必要のない半導体記憶装置を提供する。

【解決手段】不揮発性の半導体記憶装置とする際、揮発性の記憶装置と不揮発性の記憶装置を分離することなく構成する。具体的に半導体記憶装置には、酸化物半導体を半導体層に有するトランジスタ及び容量素子に接続されたデータ保持部にデータを保持する構成とする。そしてデータ保持部に保持される電位は、電荷をリークすることなくデータの出力が可能なデータ電位保持回路及び電荷をリークすることなくデータ保持部に保持した電位を容量素子を介した容量結合により制御可能なデータ電位制御回路で制御される。

(もっと読む)

半導体装置及びその駆動方法

【課題】消費電力を低減することが可能な新たな構造の半導体装置及びその駆動方法を提供する。

【解決手段】メモリセルは、容量素子と、第1のトランジスタと、第1のトランジスタよりオフ電流の小さな第2のトランジスタとを有する。第1のトランジスタは、第2のトランジスタよりもスイッチング速度が速い。第1のトランジスタと第2のトランジスタと容量素子とは直列に電気的に接続されている。容量素子への電荷の蓄積、及び容量素子からの電荷の放出は、第1のトランジスタと第2のトランジスタの両方を介して行われる。こうして、半導体装置の消費電力を少なく、且つ情報の書き込み及び読み出し速度を高速化することができる。

(もっと読む)

記憶装置

【課題】電力が供給されない状況でも記憶内容の保持が可能であり、記憶素子を構成するトランジスタをオンすることなく、記憶したデータを高速で読み出すことができる記憶装置を提供する。

【解決手段】記憶装置において、酸化物半導体層をチャネル領域として有するトランジスタ及び保持容量素子を有するメモリセルと、容量素子と、を電気的に接続させてノードを構成し、該ノードは保持容量素子を介した容量結合により保持データに応じて昇圧され、この電位を増幅回路によって読み出すことで、データの識別を行うことができる。

(もっと読む)

回路及び回路の駆動方法

【課題】消費電力を低減する。

【解決手段】入力信号を元に論理演算処理を行い、論理演算処理の結果に応じて設定される電位を記憶データとして保持し、記憶データに応じた値の信号を出力信号として出力する機能を有する演算回路を具備し、演算回路は、論理演算処理を行う演算部と、記憶データの電位を、論理演算処理の結果に応じた電位に設定するか否かを制御する第1の電界効果トランジスタと、記憶データの電位を、基準電位に設定するか否かを制御する第2の電界効果トランジスタと、記憶データに応じた値の信号を出力信号として出力するか否かを制御する第3の電界効果トランジスタと、を備える。

(もっと読む)

表示装置

【課題】信頼性の高い表示装置を提供する。

【解決手段】酸化物半導体を有するトランジスタを有し、酸化物半導体の下に設けられた絶縁膜と、酸化物半導体の上に設けられた絶縁膜とを有する。平坦性を持たせるため、有機材料を含む絶縁膜をさらに設ける。シール材は、有機材料を含む絶縁膜と重なることはなく、絶縁膜と接している。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化す

ることを目的の一とする。

【解決手段】酸化物半導体膜を有するボトムゲート構造のトランジスタの作製工程におい

て、熱処理による脱水化または脱水素化処理、及び酸素ドープ処理を行う。酸素ドープ処

理されたゲート絶縁膜、熱処理による脱水化または脱水素化処理された酸化物半導体膜を

有するトランジスタは、バイアス−熱ストレス試験(BT試験)前後においてもトランジ

スタのしきい値電圧の変化量が低減できており、信頼性の高いトランジスタとすることが

できる。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を提供する。

【解決手段】化学量論的組成比を超える酸素を含む領域を有する非晶質酸化物半導体層と、該非晶質酸化物半導体層上に設けられた酸化アルミニウム膜とを含んで構成される半導体装置を提供する。該非晶質酸化物半導体層は、脱水又は脱水素化処理を行った結晶性又は非晶質酸化物半導体層に対して、酸素注入処理を行い、その後、酸化アルミニウム膜を設けた状態で450℃以下の熱処理を行うことで形成される。

(もっと読む)

酸化物半導体薄膜層を有する積層構造及び薄膜トランジスタ

【課題】酸化物薄膜の結晶配置の方向を制御し、良質な酸化物薄膜を提供する。

【解決手段】酸化物層と絶縁層からなる積層構造であって、前記酸化物層のキャリア濃度が1018/cm3以下、平均結晶粒径が1μm以上であり、前記酸化物層の結晶が、前記絶縁層の表面に柱状に配置していることを特徴とする積層構造。

(もっと読む)

表示装置

【課題】酸化物半導体を用いた薄膜トランジスタを具備する画素において、開口率の向上

を図ることのできる発光表示装置を提供することを課題の一とする。

【解決手段】薄膜トランジスタ、及び発光素子を有する複数の画素を有し、画素は、走査

線として機能する第1の配線に電気的に接続されており、薄膜トランジスタは、第1の配

線上にゲート絶縁膜を介して設けられた酸化物半導体層を有し、酸化物半導体層は、第1

の配線が設けられた領域をはみ出て設けられており、発光素子と、酸化物半導体層とが重

畳して設けられる。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化することを目的の一とする。

【解決手段】第1の絶縁膜を形成し、第1の絶縁膜上に、ソース電極およびドレイン電極、ならびに、ソース電極およびドレイン電極と電気的に接続する酸化物半導体膜を形成し、酸化物半導体膜に熱処理を行って、酸化物半導体膜中の水素原子を除去し、水素原子が除去された酸化物半導体膜に酸素ドープ処理を行って、酸化物半導体膜中に酸素原子を供給し、酸素原子が供給された酸化物半導体膜上に、第2の絶縁膜を形成し、第2の絶縁膜上の酸化物半導体膜と重畳する領域にゲート電極を形成する半導体装置の作製方法である。

(もっと読む)

半導体装置およびその作製方法

【課題】短チャネル効果を抑制しつつ微細化を達成した半導体装置およびその作製方法を提供することを目的の一とする。

【解決手段】絶縁層にトレンチを形成し、トレンチの上端コーナー部と接する酸化物半導体膜に不純物を添加し、ソース領域およびドレイン領域を形成する。上記構造にすることで微細化することが可能である。また、トレンチを有することで、ソース電極層とドレイン電極層との距離を狭くしても該トレンチの深さを適宜設定することで、短チャネル効果を抑制することができる。

(もっと読む)

半導体装置、記憶装置および半導体装置の作製方法

【課題】書き込み回数に制限がなく、消費電力が低く、記憶内容(電荷)の保持特性が改善され、かつ小型化に適した構造の半導体装置および、当該半導体装置を備える、消費電力が低く、記憶内容(電荷)の保持特性が改善された記憶装置を提供する。

【解決手段】半導体装置の有するトランジスタの半導体層として酸化物半導体を用いることで、ソースとドレイン間のリーク電流を低減できるため、半導体装置および当該半導体装置を備える記憶装置の消費電力低減、保持特性の改善を達成できる。また、トランジスタのドレイン電極、半導体層およびドレイン電極と重なる第1の電極により容量素子を形成し、容量素子と重なる位置でゲート電極を上層へ取り出す構造とした。これにより、半導体装置および当該半導体装置を備える記憶装置を小型化できる。

(もっと読む)

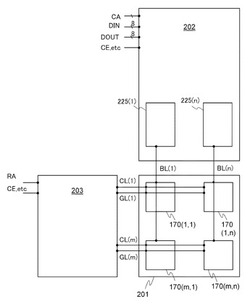

半導体装置

【課題】ワード線の負荷を増大させることなく、ワード線に生じるノイズを低減する。

【解決手段】少なくとも一のスイッチング素子を有する複数の記憶素子がマトリクス状に配置され、前記記憶素子のそれぞれにはワード線とビット線がそれぞれ接続され、前記ワード線には少数キャリアが実質的に存在しないトランジスタのゲート(またはソース及びドレイン)が接続され、前記少数キャリアが実質的に存在しないトランジスタのソース及びドレイン(またはゲート)の電位が制御されることで前記少数キャリアが実質的に存在しないトランジスタの容量値の制御を行う半導体装置とする。前記少数キャリアが実質的に存在しないトランジスタは、ワイドギャップ半導体により設けられていればよい。

(もっと読む)

論理回路および半導体装置

【課題】微細化に適し、且つ演算処理を行う各種論理回路において、演算処理を実行中に電源をオフする場合でも、電源をオフする直前に入力された電位を保持できる論理回路を提供することである。また、該論理回路を有する半導体装置を提供することである。

【解決手段】入力端子および出力端子と、入力端子および出力端子に電気的に接続された主要論理回路部と、入力端子および主要論理回路部に電気的に接続されたスイッチング素子を有し、スイッチング素子の第1端子は入力端子と電気的に接続されており、スイッチング素子の第2端子は主要論理回路を構成する1以上のトランジスタのゲートと電気的に接続されており、スイッチング素子は、オフ状態におけるリーク電流がチャネル幅1μmあたり1×10−17A以下のトランジスタとする論理回路である。また、このような論理回路を有する半導体装置である。

(もっと読む)

低温ポリシリコンTFTのための多層高品質ゲート誘電体

【課題】TFTデバイスにおける高品質ゲート誘電体層を形成するのに有用な方法及び装置を提供する。

【解決手段】高密度プラズマ酸化(HDPO)処理層がチャネル、ソース、及びドレイン領域上に形成されて誘電体インターフェースを構成し、次に、1つ以上の誘電体層をHDPO層上に堆積して高品質ゲート誘電体層を形成する。HDPO処理は、一般的に、誘導及び/又は容量結合RF伝達デバイスを用いてプラズマを発生し、基板上で発生したプラズマを制御し、また酸化源を含有するガスを注入して界面層を成長させる。次に、第2誘電体層をCVD又はPECVD堆積処理を用いて基板上に堆積する。

(もっと読む)

半導体装置

【課題】新たな構造の酸化物半導体層を用いた新たな構造の半導体装置を提供することを

目的の一とする。

【解決手段】絶縁表面を有する基板上の、第1の酸化物半導体層の表面から内部に向かっ

て成長させた結晶領域を有する第1の酸化物半導体層と、第1の酸化物半導体層上の第2

の酸化物半導体層と、第2の酸化物半導体層と接するソース電極層およびドレイン電極層

と、第2の酸化物半導体層、ソース電極層、およびドレイン電極層を覆うゲート絶縁層と

、ゲート絶縁層上の、第2の酸化物半導体層と重畳する領域のゲート電極層と、を有し、

第2の酸化物半導体層は、結晶領域から成長させた結晶を有する層である半導体装置であ

る。

(もっと読む)

半導体装置の作製方法

【課題】チャネル形成領域が形成される半導体層のチャネル形成領域と逆側近傍の加工方法を工夫した半導体装置の作製方法を提供する。

【解決手段】少なくとも結晶性半導体膜上に非晶質半導体膜が設けられた積層半導体膜の一部に対して、少なくとも第1のエッチングと第2のエッチングを行い、第1のエッチングは非晶質半導体膜の一部を残存させつつ行い、第2のエッチングは非晶質半導体膜上の被覆膜を除去させた後に、非晶質半導体膜に対するエッチングレートが高く、且つ結晶性半導体膜に対するエッチングレートが低い条件により行い、積層半導体膜に設けられた結晶性半導体膜の一部を露出させる。

(もっと読む)

酸化物半導体素子、酸化物半導体素子の製造方法、酸化物半導体素子を含む表示装置、及び酸化物半導体素子を含む表示装置の製造方法

【課題】酸化物半導体素子、酸化物半導体素子の製造方法、酸化物半導体素子を含む表示装置、及び酸化物半導体素子を含む表示装置の製造方法を提供すること。

【解決手段】酸化物半導体素子は、基板上に配置されるゲート電極と、リセス構造を含むゲート絶縁層と、ゲート絶縁層の一側上に配置されるソース電極と、ゲート絶縁層の他側上に配置されるドレーン電極と、ゲート絶縁層、ソース電極、及びドレーン電極上に配置されるアクティブパターンとを含むようにすることができる。リセス構造はゲート電極の上部に位置するようにすることができ、アクティブパターンはリセス構造を埋め立てるようにすることができる。酸化物半導体素子がリセス構造を有するゲート絶縁層を具備することによって、電荷移動度、閾値電圧分布、動作電流などの多様な電気的特性を向上させることができる。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】省電力化かつ高速での書き込み処理が可能なメモリの多値化に適した半導体装置およびベリファイ処理を提供する。

【解決手段】半導体装置に用いるメモリセルを、酸化物半導体を用いたトランジスタと酸化物半導体以外の材料を用いたトランジスタをそれぞれ有する構成とし、書き込み回路を用いてデータバッファのデータをメモリセルに書き込む前に、予め各々のメモリセルの有するしきい値ばらつきを調べ、データバッファのデータに対して当該しきい値ばらつきを補正したデータが各々のメモリセルに書き込む。

(もっと読む)

121 - 140 / 1,159

[ Back to top ]