Fターム[5F110GG30]の内容

Fターム[5F110GG30]に分類される特許

321 - 331 / 331

垂直型ナノチューブ半導体デバイス構造体及びその形成方法

【課題】 大量生産技術に対応した、チャネル領域として1つ又は複数の半導体カーボン・ナノチューブを組み込む垂直型FET構造体を提供する。

【解決手段】 少なくとも1つのナノチューブを組み組む垂直型デバイス構造体、及び、化学気相成長法によってこうしたデバイス構造体を製造する方法である。各々のナノチューブは、触媒パッドによって触媒作用が及ぼされる化学気相成長法によって成長され、誘電体材料のコーティング内に包み込まれる。包み込まれたナノチューブがゲート電極の厚さを通って垂直方向に延びるように、該包み込まれたナノチューブの周りにゲート電極を形成することによって、垂直型電界効果トランジスタを作ることができる。包み込まれたナノチューブ、及び、該包み込められたナノチューブを支持する対応する触媒パッドが1つのキャパシタ・プレートを形成するように、キャパシタを作ることができる。

(もっと読む)

半導体電源スイッチ、および、半導体電源スイッチの製造に適した方法

半導体電源スイッチ(1)が、ソース端子(2)と、ドレイン端子(3)と、それらの間に設けられた半導体構造と、ゲート(5)とを備えている。このゲート(5)は、ソース端子(2)とドレイン端子(3)との間の半導体構造を介して電流の流れを制御するために、用いられる。該半導体構造は、複数のナノワイヤ(4)を備えている。これらのナノワイヤ(4)は、並列に接続されており、各ナノワイヤがソース端子とドレイン端子との間の電気接続を形成するように、配置されている。  (もっと読む)

(もっと読む)

完全に量子井戸が空乏化した低出力のマルチチャネルCMOSFET

マルチチャネル半導体デバイスは、完全に、または部分的に量子井戸が空乏化(排除)(depleted)されており、CMOSFETのようなULSIデバイスにおいて特に役立つ。マルチチャネル領域(15)は、最上部のチャネル領域上に、例えばゲート絶縁膜(14c)により分離されるゲート電極が形成された状態で、基板(12)上に形成される。マルチチャネル領域(15)およびゲート電極(16)の垂直方向の積み重なりが、デバイスによって占有されるシリコン領域を増加させることなく、半導体デバイス中の駆動電流を増加させることができる。  (もっと読む)

(もっと読む)

1つ以上のトランジスタチャンネルを形成可能な電界効果マイクロエレクトロニクスデバイス

本発明は、電界効果マイクロエレクトロニクスデバイスと、さらにその製造方法に関わる。このデバイスは、基板(700)と、さらに1つ以上のトランジスタチャンネル(transistor channel)を形成することができる少なくとも1つの改善された構造(702)を含む。この構造は、基板上にスタックされた複数のバーによって形成され、電界効果トランジスタの集積化においてスペースを節約することを可能にし、さらにその性能を改善することを可能にする。  (もっと読む)

(もっと読む)

半導体装置及び半導体装置の製造方法

ソース/ドレイン領域の少なくともその幅が最も大きい部分では半導体領域の幅よりも大きく、かつソース/ドレイン領域の最上部側から基体側に向かって連続的に幅が大きくなっている傾斜部を有し、該傾斜部表面にシリサイド膜が形成されていることを特徴とする半導体装置とする。  (もっと読む)

(もっと読む)

ナノ構造を沈着、配向させる方法、装置及び組成物

移送基体上に複数のナノ材料を供給し、これらナノ材料を、受取基体の表面又は複数部分上に配置した付着性材料と接触させることを特徴とする、ナノ材料を受取基体上に沈着し、任意にナノ材料を所望の配向で沈着させる方法及びシステム。配位は任意に、移送工程中、移送基体及び受取基体を互いに対し移動することにより付与される。 (もっと読む)

フィン型電界効果トランジスタを有する半導体装置

n型電界効果トランジスタおよびp型電界効果トランジスタとを含む半導体装置であって、n型電界効果トランジスタを構成する突起状半導体領域の結晶方位は、その基板と平行な面が実質上{100}面であり、その側面が実質上前記{100}面と直交する{100}面であり、p型電界効果トランジスタを構成する突起状半導体領域の結晶方位は、その基板と平行な面が実質上{100}面であり、その側面が実質上前記{100}面と直交する{110}面である、という条件を満足する半導体装置とする。 (もっと読む)

ナノワイヤ複合体およびこれらに由来する電子基板を作製するためのシステムおよび方法

本発明は、ナノワイヤ−材料複合体を生成するシステムおよび処理に関わる。ナノワイヤ(606)が少なくとも一つの表面の一部分(604)に取り付けられた基板が提供される。ナノワイヤ−材料複合体を生成するよう、当該部分上に材料が堆積される。処理は、独立したナノワイヤ−材料複合体を生成するよう基板からナノワイヤ−材料複合体を分離することを必要に応じて含む。独立したナノワイヤ−材料複合体は、必要に応じて、電子基板に更に処理される。様々な電子基板は本明細書記載の方法を用いて形成される。例えば、多色発光ダイオードは、それぞれの複合体層が異なる波長で光を発するナノワイヤ−材料複合体の多数の積層された層から形成され得る。  (もっと読む)

(もっと読む)

化学機械研磨プレーナ化のためのデュアルシリコンゲート層を有するFINFET

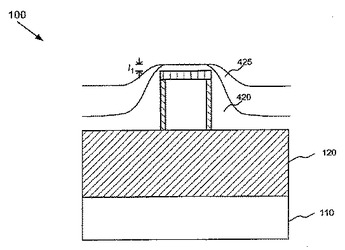

FinFETタイプの半導体デバイスは、フィン構造(210)を含んでいる。この上には、比較的薄いアモルファスシリコン層(420)を形成し、それから非ドープポリシリコン層(425)を形成する。この半導体デバイスは、アモルファスシリコン層(420)がフィン構造の損傷を防ぐ停止層として働く化学機械研磨(CMP)を使用してプレーナ化することができる。  (もっと読む)

(もっと読む)

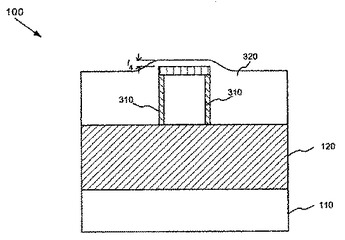

FINFET中のゲート領域のマルチステップ化学機械研磨

チャネル上にたい積されるゲート材料層(320)をプレーナ化するステップを含む、MOSFET型の半導体デバイスを製造する方法である。このプレーナ化は、第1の”荒い”プレーナ化と、その後の”緻密な”プレーナ化を含んだ複数のステッププロセスで実行される。より緻密なプレーナ化で使用されるスラリーは、ゲート材料の低い領域に付着し易い付加材料を含んでいてもよい。  (もっと読む)

(もっと読む)

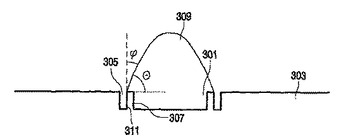

半導体構成用の構造およびその製造方法

本発明は、半導体構成用の構造に関する。半導体を含む溶液の堆積を補助するレジスト構造は、直接、あるいは介在層を介して基板に結合される。このレジスト構造は、半導体を含む溶液(309)を堆積するくぼみ(301)と、くぼみ(309)の縁部の少なくとも一部に整列し、突出部(307)によってくぼみ(309)から分離した溝(305)とを備える。好ましくは、溝(305)は、くぼみ(309)を取り囲む。この溝により、半導体を含む溶液を固定する作用が得られ、それによって濡れ性が改善し、それにしたがって、より大きな体積の半導体を所与の区域に付着させることができる。  (もっと読む)

(もっと読む)

321 - 331 / 331

[ Back to top ]