Fターム[5F110HJ13]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−不純物領域 (11,069) | 不純物領域の製法 (6,364) | 不純物の導入方法 (4,201) | イオン注入 (2,973)

Fターム[5F110HJ13]の下位に属するFターム

斜めイオン注入 (155)

Fターム[5F110HJ13]に分類される特許

2,001 - 2,020 / 2,818

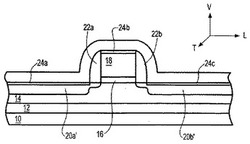

半導体構造およびその製作方法(チャネルの応力向上のための低ヤング率スペーサ)

【課題】チャネル領域を有する半導体基板を使用する半導体構造およびその製作方法を提供すること。

【解決手段】ゲート電極が、半導体基板上に配置される。スペーサが、ゲート電極の側壁に隣接して配置される。このスペーサは、約10〜約50GPaのモジュラスを有する材料で形成される。このモジュラスは、チャネル領域内に向上した応力をもたらす。

(もっと読む)

光照射装置、結晶化装置、結晶化方法、およびデバイス

【課題】 レーザ光源の特性の経時的な劣化などに起因する光束の波面の歪みの影響を受けることなく所望の光強度分布を安定的に形成することのできる光照射装置。

【解決手段】 互いにインコヒーレントな複数のレーザ光源(1a)を有する光源装置(1)と、複数のレーザ光源から発振されるレーザ光に基づいて光変調素子(2)を重畳的に照明するためのホモジナイザ(3a)を含む照明光学系(3)と、光変調素子により位相変調されたレーザ光に基づいて所定の光強度分布を所定面に形成する結像光学系とを備えている。

(もっと読む)

半導体装置の製造方法

【課題】半導体層下に埋め込み絶縁層を埋め込むことを可能としつつ、平坦化膜の膜厚測

定にかかる時間を短縮する。

【解決手段】SOI構造の素子分離に用いられる絶縁膜を平坦化するときの膜厚をモニタ

するための膜厚測定領域R1およびSOI構造を形成するSOI構造形成領域R2を半導

体基板1に設け、膜厚測定領域R1に形成された絶縁膜12および支持体8の膜厚をモニ

タしながら、絶縁膜12および支持体8を薄膜化することにより、SOI構造形成領域R

2の第2半導体層4aの表面を露出させ、第2半導体層4aを水平面内で素子分離する。

(もっと読む)

電荷キャリア移動度修正のための回転剪断応力

【課題】 電荷キャリア移動度修正のための回転剪断応力を提供すること。

【解決手段】 半導体構造体及びその製造方法は、分離トレンチにより取り囲まれた活性領域メサを有する半導体基板を使用する。第1応力を有する第1分離領域は分離トレンチに配置される。第1応力とは異なる第2応力を有する第2分離領域もまた分離トレンチに配置される。第1分離領域及び第2分離領域は活性領域メサに回転剪断応力をかけるような大きさにされ、そのように位置決めされる。

(もっと読む)

ストレッサ層に隣接する活性化領域を有するトランジスタ構造を含む電子デバイスおよび該電子デバイスを製造する方法

電子デバイス(10)が、第1の伝導タイプのトランジスタ構造(50)と、フィールドアイソレーション領域(22)と、フィールドアイソレーション領域の上に横たわる第1の応力タイプの(130)とを有する。例えば、トランジスタ構造(50)がpチャネルトランジスタ構造(50)であってよく、第1の応力タイプが引っ張りであってよく、または、トランジスタ構造(60)がnチャネルトランジスタ構造であってよく、第1の応力タイプ(70)が圧縮であってよい。トランジスタ構造(50)は、活性化領域内に横たわるチャネル領域(54)を含む。活性化領域の端は、チャネル領域(54)とフィールドアイソレーション領域(22)との間の界面を有する。頂部から見ると、層は、活性化領域の端の近くに横たわる端を含む。端の間の位置関係は、トランジスタ構造(50)のチャネル領域(54)内のキャリア移動度に影響する。  (もっと読む)

(もっと読む)

スペーサレスFET及びデュアル・ライナ法による歪み強化を増加させる構造体及び方法

【課題】 スペースレスFET及びデュアル・ライナ法による歪み強化を増加させる構造体及び方法を提供する。

【解決手段】 歪み強化がnFET及びpFETデバイスの両方に対して達成される半導体構造体及びそれを製造する方法を提供する。特に、本発明は、より強い歪み強化及び欠陥削減のための少なくとも1つのスペーサレスFETを提供する。少なくとも1つのスペーサレスFETは、pFET、nFET又はそれらの組合せとすることができるが、一般に、pFETはnFETよりも大きな幅を有するように製造されるので、スペーサレスpFETが特に好ましい。少なくとも1つのスペーサレスFETは、スペーサを有するFETを含んだ従来技術の構造体よりも、デバイス・チャネルにより接近した応力誘起ライナを設けることを可能にする。スペーサレスFETは、スペーサレスFETの下側に侵入しない、対応するシリサイド化ソース/ドレイン拡散コンタクトの抵抗に悪影響を与えることなく達成される。

(もっと読む)

歪みシリコンにおける欠陥低減のための窒素ベース注入物

トランジスタ(200)が半導体基板(202)上に作製され、ここで基板の降伏強さ又は弾性が向上され、又は他の方法で適合される。歪み誘起層(236)がトランジスタを覆って形成され、これに歪みを加えてトランジスタの動作特性を変更し、より詳細にはトランジスタ内のキャリアの移動度を向上させる。キャリア移動度を向上させることにより、トランジスタの大きさを低減させることが可能となると同時に、トランジスタを所望通りに動作させることが可能となる。しかしながら、トランジスタの作製に伴う高い歪み及び温度は、有害な塑性変形をもたらす結果となる。従って、窒素を基板に、より詳細にはトランジスタのソース/ドレイン延長領域(220,222)及び/又はソース/ドレイン領域(228,230)に導入することによって、シリコン基板の降伏強さが適合される。窒素は、ソース/ドレイン延長領域形成及び/又はソース/ドレイン領域形成の一部として窒素を付加することにより、トランジスタ作製中に容易に導入することができる。基板の降伏強さが向上すると、歪み誘起層に起因するトランジスタの塑性変形が軽減される。 (もっと読む)

半導体装置および半導体装置の製造方法

【課題】チャネル領域のダメージを抑制しつつ、半導体層の側壁にチャネルを持たせるとともに、チャネルが形成される半導体層の膜厚制御を安定して行えるようにする。

【解決手段】選択エピタキシャル成長を用いることにより、第1半導体層52に設けられた凸部の側壁に第2半導体層55を成膜し、第1半導体層52をエッチング除去した後、第2半導体層55の側壁にサイドウォール62a、62bをそれぞれ形成し、サイドウォール62a、62bをマスクとして半導体基板51および第2半導体層55の選択酸化を行うことにより、半導体基板51と第2半導体層55との間に埋め込まれた埋め込み酸化膜63aを形成する。

(もっと読む)

半導体構造およびその製作方法(複数の結晶方位を有する半導体基板)

【課題】実用性の向上した半導体構造およびそのような半導体構造の製作方法を提供すること。

【解決手段】半導体構造およびその製作方法は、基板の誘電体表面に配置された第1の結晶方位の第1の表面半導体層を含む。スタック層が、第1の表面半導体層から横方向に離れて誘電体表面に配置される。スタック層は、誘電体表面のより近くに配置された埋め込み半導体層と、埋め込み半導体層の上に、それと接触せずに配置された、第1の結晶方位と異なる第2の結晶方位の第2の表面半導体層とを含む。この半導体構造は、異なる結晶方位の一対の半導体表面領域を提供する。特定の実施形態は、順次の積層、パターン化、選択的な剥離、および選択的なエピタキシャル堆積法を利用して製作されることができる。

(もっと読む)

画像表示装置及びその製造方法

【課題】画像表示装置の製造歩留まりを向上させること。

【解決手段】絶縁性基板上に、複数の島状半導体層を形成する工程と、前記島状半導体層上にゲート絶縁膜を形成する工程と、該ゲート絶縁膜にコンタクトホールを開口する工程と、前記ゲート絶縁膜上にゲート電極を形成し、前記島状半導体層と前記ゲート電極を接触させる工程と、前記島状半導体層にソース領域、ドレイン領域、及びそれらに挟まれたチャネル領域を形成する工程と、前記ゲート電極上に層間絶縁膜を形成する工程と、前記ソース領域、前記ドレイン領域および前記層間絶縁膜と接するソース/ドレイン電極を形成する工程と、前記ソース/ドレイン電極形成後に、スルーホールを開口し、前記島状半導体層と前記ゲート電極の接触部を除去する工程を有する画像表示装置の製造方法。

(もっと読む)

電界効果トランジスタ(FET)およびその製造方法(高性能および低リーク電界効果トランジスタを製造するための構造および方法)

【課題】ソース側半導体、ドレイン側半導体、およびゲートを含む電界効果トランジスタ(FET)を提供すること。

【解決手段】ソース側半導体は高移動度半導体材料で作製され、ドレイン側半導体は低リーク半導体材料で作製される。一実施形態では、このFETは、金属酸化物半導体電界効果トランジスタ(MOSFET)である。また、このFETの製造方法も提供される。

(もっと読む)

半導体装置及びその製造方法

【課題】大容量化、小型化が可能であり、絶縁破壊及びリーク電流等の不良が低減された容量素子を有する半導体装置。

【解決手段】絶縁基板上に、薄膜トランジスタ及び容量素子42を備える半導体装置であって、上記薄膜トランジスタは、チャネル43c並びにチャネル43c横に配置されたソース43s及びドレイン43dを有する半導体層43と、チャネル43c上に配置された第1絶縁膜3と、第1絶縁膜3上のチャネル43cと対向する位置に配置された第1電極5とを有するものであり、上記容量素子42は、第1電極5、第2絶縁膜4及び第2電極6が絶縁基板側からこの順に配置され、かつ第2電極6の外縁が第1電極5の外縁よりも内側又は外縁上に位置する半導体装置。

(もっと読む)

記憶装置

【課題】作製工程数を削減し、よりコスト削減が可能な、不揮発メモリを含むライトワンスメモリデバイスのような記録装置及び該記憶装置を利用した半導体装置を提供する。

【解決手段】第1の導電膜113と、前記第1の導電膜113上に形成された絶縁膜114と、前記絶縁膜114に形成された開口部115とコンタクトホール116及び前記絶縁膜114上に形成された第2の導電膜117とを有し、前記第1の導電膜113と前記開口部内に形成された前記第2の導電膜117との間に前記絶縁膜が存在し、前記コンタクトホール116において、前記第1の導電膜113と前記第2の導電膜117とが電気的に接続されている。

(もっと読む)

SOI構造を有する半導体装置の製造方法

【課題】ソース/ドレイン領域からの不純物の拡散を抑制することができるSOI構造を有する半導体装置の製造方法を提供する。

【解決手段】フォトレジスト6をマスクとして、シリコン層3の分離注入領域に第1導電型の不純物をイオン注入しチャネル領域よりも高い不純物濃度を有する不純物領域を形成する。フォトレジスト6をマスクとしてシリコン層3を複数に分離する。シリコン層3の主表面上にゲート絶縁膜11を介しゲート電極12を形成する。ゲート電極12をマスクとしてシリコン層3に第2導電型の不純物をイオン注入しソース/ドレイン領域14を形成する。ゲート電極12をマスクとして窒素を注入し熱処理を施すことによって窒素の濃度ピークがフィールド酸化膜13に接する前記シリコン層3表面に位置するようにする。

(もっと読む)

光吸収しきい値バイアス領域を有するフローティングボディゲルマニウムフォトトランジスタ

【課題】 ゲルマニウムフォトトランジスタのフローティングボディ効果を高める。

【解決手段】 光吸収しきい値バイアス領域を有するフローティングボディゲルマニウムフォトトランジスタの製造方法において、P型シリコン基板の第1の表面上に選択的に形成された絶縁体層上に、エピタキシャルGe層を形成する工程と、Ge層中にチャネル領域を形成する工程と、ゲート誘電体、ゲート電極、およびゲートスペーサを形成する工程と、Ge層中にソース/ドレイン(S/D)領域を形成する工程と、Ge層中にチャネル領域に隣接する光吸収しきい値バイアス領域を形成する工程とを有する。一実施形態において、第2のS/D領域は、オフセット領域によりチャネルから引き離され、光吸収しきい値バイアス領域は、濃度の薄いP型ドーピング後のGe層中のオフセット領域である。

(もっと読む)

薄膜トランジスタの作製方法

【課題】

本発明は、大粒径の結晶粒を有する結晶性半導体膜を、位置を制御して形成することにより、高速動作が可能な薄膜トランジスタを提供することを目的とする。

【解決手段】

下地絶縁膜231と半導体膜232が形成された基板230の表面側から第1のレーザビーム241を照射し、基板230の裏面側に設置された反射層222で反射された第2のレーザビーム242を裏面側から照射することにより、半導体膜の所定の位置に結晶核245を形成し、横方向に結晶成長させることで大粒径の結晶粒を有する結晶性半導体膜を得るものである。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 製造コストを抑制しつつ、絶縁体上に半導体層を形成するとともに、絶縁体上に形成された半導体層の品質の劣化を抑制しつつ、メサ分離された半導体層の上端部の丸め処理を行う。

【解決手段】 半導体基板1と第2半導体層4との間の空洞部10に埋め込み絶縁層11を形成した後、半導体基板1および第2半導体層4の上端部を熱酸化することにより、溝9bに沿って第2半導体層4の上端部を丸めるとともに、溝9a、9cに沿って半導体基板1の上端部を丸め、溝9bに端部がかかるようにして第2半導体層4上にゲート電極15を形成するとともに、溝9aまたは溝9cに端部がかかるようにして半導体基板1上にゲート電極25を形成する。

(もっと読む)

レトログレード領域を備える横型DMOSトランジスタ及びその製造方法

【課題】レトログレード領域を備える横型DMOSトランジスタ及びその製造方法を提供する。

【解決手段】表面に隣接したソース領域及びドレイン領域と、ソース領域とドレイン領域との間のドリフト領域とを備える半導体基板を備え、ドリフト領域は、ドリフト領域の不純物濃度のピークが半導体基板の表面から離れて位置するように不純物濃度の分布を有することを特徴とするMOSトランジスタである。ドリフト領域は、半導体基板の表面下で一定の距離ほど離れているレトログレード領域を備え、ドリフト領域の不純物濃度のピークは、レトログレード領域の一部内に提供される。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 シリコン層の厚さが極薄膜化した場合でも、チャネル領域の端部での寄生チャネル形成を防止できるようにした半導体装置の製造方法及び半導体装置を提供する。

【解決手段】 SOI基板10にLOCOS層15を形成し、LOCOS層15で囲まれた素子領域にnチャネルSOIトランジスタ100を形成する半導体装置の製造方法であって、素子領域のSOI層5にゲート絶縁膜21を形成する工程と、トランジスタのソースとドレインとによって挟まれるチャネル領域のLOCOS層15側の端部のSOI層5に、寄生チャネル防止用のBを導入する工程とを含み、前記Bを導入する工程はゲート絶縁膜21を形成した後で行う。

(もっと読む)

半導体デバイスおよびその製造方法

【課題】仕事関数の調整された複数ゲート電極を形成するための製造方法を提供する。

【解決手段】相補型金属酸化膜半導体(CMOS)デバイスは、第1のパラメータを有する少なくとも2つの第1のゲート電極120を備えたPMOSトランジスタと、上記第1のパラメータとは異なる第2のパラメータを有する少なくとも2つの第2のゲート電極120を備えたNMOSトランジスタと、を有している。上記第1のパラメータおよび上記第2のパラメータは、上記PMOSおよびNMOSトランジスタの上記ゲート電極材料の厚さ、またはドーパントプロファイルを含んでいる。上記少なくとも2つの第1のゲート電極および上記少なくとも2つの第2のゲート電極の上記第1および第2のパラメータは、それぞれ、上記PMOSおよびNMOSトランジスタの仕事関数を規定する。

(もっと読む)

2,001 - 2,020 / 2,818

[ Back to top ]