Fターム[5F110HJ13]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−不純物領域 (11,069) | 不純物領域の製法 (6,364) | 不純物の導入方法 (4,201) | イオン注入 (2,973)

Fターム[5F110HJ13]の下位に属するFターム

斜めイオン注入 (155)

Fターム[5F110HJ13]に分類される特許

2,801 - 2,818 / 2,818

ナノワイヤ複合体およびこれらに由来する電子基板を作製するためのシステムおよび方法

本発明は、ナノワイヤ−材料複合体を生成するシステムおよび処理に関わる。ナノワイヤ(606)が少なくとも一つの表面の一部分(604)に取り付けられた基板が提供される。ナノワイヤ−材料複合体を生成するよう、当該部分上に材料が堆積される。処理は、独立したナノワイヤ−材料複合体を生成するよう基板からナノワイヤ−材料複合体を分離することを必要に応じて含む。独立したナノワイヤ−材料複合体は、必要に応じて、電子基板に更に処理される。様々な電子基板は本明細書記載の方法を用いて形成される。例えば、多色発光ダイオードは、それぞれの複合体層が異なる波長で光を発するナノワイヤ−材料複合体の多数の積層された層から形成され得る。  (もっと読む)

(もっと読む)

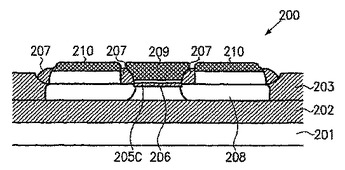

ゲートの枯渇を低減した注入ゲート電極を有する電界効果型トランジスタ、及び、このトランジスタを製造する方法

ドレイン領域及びソース領域(208)を規定する前に、注入マスク(220)を形成することにより、ゲートドーパント密度をドレインドーパント密度及びゲートドーパント密度から効果的に分離する。さらに、注入マスク(220)を除去した後に、ゲート電極(205)の横方向寸法は、十分に確立された側壁スペーサ(207)技術によって規定される。その結果、フォトリソグラフィ及び異方性エッチングに基づく従来の方法に対してデバイスの縮小に関する優位性を提供する。  (もっと読む)

(もっと読む)

フロントゲート型SOI−MOSFETの製造方法

【課題】ソース/ドレイン拡張とフロントゲート(front gate)に自己整合させたバックゲートを含む、FD型SOI−CMOSデバイスの製造方法に関する。

【解決手段】

SOI−CMOS技術は、ポリシリコン、即ちポリSiバックゲートは、フロントゲート・デバイスの閾値電圧を制御するために使用され、nMOS及びpMOSバックゲートは、互いに独立に、及びフロントゲートと独立に、スイッチされる。

特に、バックゲートが、デバイスのフロントゲート及びソース/ドレイン拡張に自己整合されたバックゲートFD型CMOSデバイスの製造方法を提供する。バックゲートFD型CMOSデバイスは、SIMOX又は結合SOI−ウエハ、ウエハボンディングと薄膜化、ポリSiエッチング、LP−CVD、機械化学研磨(CMP)を用いて製造される。

(もっと読む)

半導体デバイスおよびその製造方法

集積回路での使用に適した歪み半導体デバイスおよび歪み半導体デバイスの製造方法。半導体−オン−インシュレータ基板からメサ分離構造が形成される。このメサ分離構造にゲート構造が形成される。このゲート構造は、ゲート絶縁材料に配置されたゲートと、対向する2組の側壁を有する。ゲート構造の対向する第1の組の側壁に隣接するメサ分離構造の一部に、半導体材料が選択的に成長され、ドープが行われる。ドープされた半導体材料がシリサイド化されて、絶縁材料によって保護される。ゲートがシリサイド化され、このシリサイドが、対向する第2の組の側壁を覆っており、チャネル領域に応力を付与する。  (もっと読む)

(もっと読む)

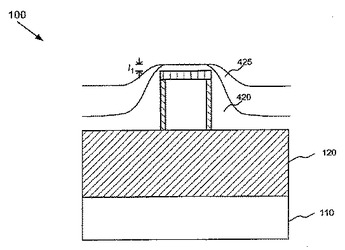

化学機械研磨プレーナ化のためのデュアルシリコンゲート層を有するFINFET

FinFETタイプの半導体デバイスは、フィン構造(210)を含んでいる。この上には、比較的薄いアモルファスシリコン層(420)を形成し、それから非ドープポリシリコン層(425)を形成する。この半導体デバイスは、アモルファスシリコン層(420)がフィン構造の損傷を防ぐ停止層として働く化学機械研磨(CMP)を使用してプレーナ化することができる。  (もっと読む)

(もっと読む)

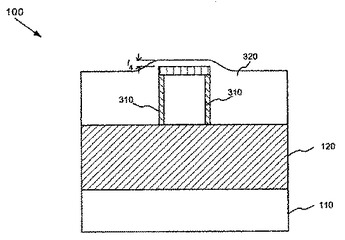

FINFET中のゲート領域のマルチステップ化学機械研磨

チャネル上にたい積されるゲート材料層(320)をプレーナ化するステップを含む、MOSFET型の半導体デバイスを製造する方法である。このプレーナ化は、第1の”荒い”プレーナ化と、その後の”緻密な”プレーナ化を含んだ複数のステッププロセスで実行される。より緻密なプレーナ化で使用されるスラリーは、ゲート材料の低い領域に付着し易い付加材料を含んでいてもよい。  (もっと読む)

(もっと読む)

個別ゲート構造を備えたトランジスタ

個別ゲート構造(701,703)を備えたトランジスタを形成する方法。これらのゲート構造はそれぞれ、半導体構造(105)の複数の側壁に隣接する。本方法は、ゲート材料層(203)を含む少なくとも一つの共形な層を、チャネル領域を含む半導体基板の上に堆積させることを含む。平坦層(403)がウェハの上に形成される。平坦層は、基板上の所定の位置において少なくとも一つの共形な層の頂部表面よりも低い位置に頂部表面を有する。少なくとも一つの共形な層をエッチングすることにより、半導体構造の上のゲート材料は除去される。  (もっと読む)

(もっと読む)

半導体装置および電子機器

【課題】 本発明では剥離技術を用いることにより様々な基板上に薄膜素子を形成し、従来の技術では不可能であると考えられていた部分に薄膜素子を形成することにより、省スペース化を図ると共に耐衝撃性やフレキシビリティに優れた半導体装置を提供する。

【解決手段】 本発明では、剥離技術を用いて一旦基板から剥離させた膜厚50μm以下の素子形成層を基板上に固着することにより、様々な基板上に薄膜素子を形成することを特徴とする。例えば、可撓性基板上に固着された薄膜素子をパネルの裏面に貼り付けたり、直接パネルの裏面に固着したり、さらには、パネルに貼り付けられたFPC上に薄膜素子を固着することにより、省スペース化を図ることができる。

(もっと読む)

半導体装置の製造方法

【課題】閾値電圧の絶対値を低く抑えながら、オフリーク電流を低下させることができる半導体装置の製造方法を提供する。

【解決手段】Nチャネル型TFT形成予定領域内のpoly−Si層4にリンを注入することにより、n+領域8を形成した後、Pチャネル型TFT形成予定領域にのみ開口部が存在するレジストマスク9を用いて、ボロンのイオン注入を行うことにより、Pチャネル型TFTのソース・ドレイン領域となるp+領域10を形成する。次に、レジストマスク9を残存させたまま、水素注入を行うことにより、Pチャネル型TFT形成予定領域内において、チャネル領域(poly−Si層4)及びソース・ドレイン領域(p+領域10)の水素化処理を行う。このような方法によれば、Nチャネル型TFTに対する水素化処理が行われないため、Nチャネル型TFTにおける不要な閾値電圧の遷移が防止され、オフリーク電流の上昇を回避することができる。

(もっと読む)

絶縁ゲート型電界効果トランジスタを含む半導体装置及びその製造方法

【課題】シリコン基板上のSi1−xGex層を用いた素子構造において、電流駆動能力の高いMISFETを含む半導体装置及びその製造方法を提供することにある。

【解決手段】シリコン基板101上に、Si1−xGex層103を形成し、このSi1−xGex層103にMISFETを形成する。ソース層及びドレイン領域106,107の接合深さを、前記Si1−xGex層103とシリコン層とが接する面を越えないようにする。

(もっと読む)

表示装置及びその製造方法

【課題】表示品質と画像取込み性能に優れた表示装置及びその製造方法を提供する。

【解決手段】表示装置の製造工程にてTFT11のチャネル部とフォトダイオードD1,D2のI層をともに水素化する際、TFT11とフォトダイオードD1,D2とで水素化の進行に違いが出るようにして、TFT11のチャネル部の欠陥密度を少なくし、かつフォトダイオードD1,D2のI層の欠陥密度を多くする。これにより、TFT11のリーク電流が抑制され、フォトダイオードD1,D2の光に対する感度を向上できる。

(もっと読む)

シリコン結晶化方法

【課題】 短い時間で良質の結晶成長をなすことができるポリシリコンの結晶化方法を提供する。

【解決手段】 非晶質シリコン薄膜が蒸着された基板110にあって、固定手段とレーザー発生装置間の遮断領域と階段状の透過領域で構成されたマスクにレーザービームを照射して、前記非晶質シリコン薄膜に照射された領域が溶融した領域との界面でグレーンが各々成長して、第1グレーン領域114aと核生成領域と第2グレーン領域114bで構成された階段状の領域を形成する第1結晶化段階と;前記マスクを横長さだけ移動して、同一な照射した後に再結晶化して、重畳された部分のグレーンが成長して、横方向に新しい結晶領域が形成される第2結晶化段階を含む方法。

(もっと読む)

半導体装置及びその製造方法

【課題】 より優れたソフトエラー耐性を有するSOI基板を用いた高信頼性のCMOS・SRAMセルを備える半導体装置及びその製造方法を提供することを目的とする。

【解決手段】 SOI基板の表面半導体層上にゲート絶縁膜を介して形成されたゲート電極と、該ゲート電極の両側の表面半導体層に形成された第1導電型ソース/ドレイン領域とから構成される半導体装置であって、前記第1導電型ソース/ドレイン領域の双方又は一方に接して第2導電型引出拡散層が形成され、少なくとも前記第1導電型ソース/ドレイン領域上から第2導電型引出拡散層上にわたってシリサイド層が形成されており、シリサイド層に接地電位が与えられてなる半導体装置。

(もっと読む)

薄膜トランジスタ装置およびその製造方法

【課題】 電気特性の優れた多結晶TFTを提供する。

【解決手段】多結晶膜3を堆積させる工程、堆積した多結晶膜のうち所望の位置4のみを残すようにエッチングする工程、残された部分的な多結晶膜の中で所望の結晶方位の結晶粒5だけを、しかも所望の結晶面(ファセット)6を出した状態になるように異方性エッチングする工程、さらに、こうして得られた結晶核の上に膜を堆積し結晶化させる工程を用いる。

(もっと読む)

薄膜トランジスタの製造方法

【課題】 薄膜トランジスタの製造方法に関し、LDD領域の抵抗を許容レベルにまで下げるとともにTFTしきい値電圧のシフトを防ぐことを目的とする。

【解決手段】 絶縁性基板上に多結晶Siを形成する工程と、該多結晶Si上にゲート絶縁膜を形成する工程と、該ゲート絶縁膜上に下層ゲート電極と該下層ゲート電極より幅の狭い上層ゲート電極から成る2層ゲート電極を形成する工程と、該2層ゲート電極をマスクにして3属あるいは5属元素から成る不純物をイオン注入する工程と、熱処理する工程と、該2層ゲート電極をマスクにして水素をイオン注入する工程を含むように構成する。

(もっと読む)

MOS型センサおよびその駆動方法

【課題】 最適な蓄積時間を素早く見つける駆動方法を提供する。

【解決手段】 複数の画素を有するMOS型センサにおいて、複数の画素の全ての画素を同時にリセットした後、前記複数の画素から信号を順に出力し、前記リセットをした時から、前記複数の画素が、飽和した信号を出力する直前までの期間を、蓄積時間とすることを特徴とするMOS型センサの駆動方法が提供される。

(もっと読む)

半導体装置の製造方法

【課題】 優れた特性を有する多結晶シリコン膜を備えた半導体装置を高い歩留まりで製造することが可能な半導体装置の製造方法を提供する。

【解決手段】 石英ガラスや無アルカリガラスなどの基板1上に、非晶質シリコン膜2aを形成する。その非晶質シリコン膜2a上にWシリサイド膜(導電膜)4bを形成する。そして、Wシリサイド膜(導電膜)4bに対し、高周波やYAGレーザービームなどの電磁波を照射することにより、Wシリサイド膜(導電膜)4bを発熱させ、この熱を利用して、非晶質シリコン膜2aを多結晶シリコン膜2に変える。

(もっと読む)

半導体膜形成方法及び薄膜半導体装置の製造方法

【課題】 本発明の目的は、基板上に高品質な半導体膜を形成するための半導体膜形成方法を提供することにある。

【解決手段】 本発明は、バイアス触媒CVD,高密度バイアス触媒CVD,バイアス減圧CVD,バイアス常圧CVDを利用して、基板に半導体膜を形成する半導体膜形成方法である。真空容器1に原料ガスを供給し、真空容器1中に配置された基板10と電極3aとの間にグロー放電開始電圧以下の電界を印加して、基板10上に、少なくとも錫、ゲルマニウム、鉛のいずれか一つ以上を含有する半導体膜と、絶縁膜と、を形成することを含む工程と、この半導体膜および絶縁膜にレーザーを照射してアニールする工程と、このアニールする工程の後工程であって、水蒸気でアニールを行う工程と、を備える。

(もっと読む)

2,801 - 2,818 / 2,818

[ Back to top ]