Fターム[5F110HL27]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−コンタクトホール介在 (16,138) | 電極、配線の製法 (3,290) | 電極、配線形成後の処理 (186)

Fターム[5F110HL27]に分類される特許

81 - 100 / 186

表示装置用Al合金膜

【課題】450〜600℃程度の高温下に曝されてもヒロックが発生せず高温耐熱性に優れており、膜自体の電気抵抗(配線抵抗)も低く、アルカリ環境下の耐食性にも優れた表示装置用Al合金膜を提供する。

【解決手段】Ta、Nb、Re、Zr、W、Mo、V、Hf、Ti、CrおよびPtよりなる群(X群)から選択される少なくとも一種の元素と、希土類元素の少なくとも一種とを含み、450〜600℃の加熱処理を行なったとき、下記(1)の要件を満足する表示装置用Al合金膜である。

(1)Alと、X群から選択される少なくとも一種の元素と、希土類元素の少なくとも一種とを含む第1の析出物について、円相当直径20nm以上の析出物が500,000個/mm2以上の密度で存在する。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いたトランジスタと、酸化物半導体以外の半導体材料を用いたトランジスタとを積層して、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタと、第1のトランジスタ上に絶縁層と、絶縁層上に第2のトランジスタと、を有し、第1のトランジスタは、第1のチャネル形成領域を含み、第2のトランジスタは、第2のチャネル形成領域を含み、第1のチャネル形成領域は、第2のチャネル形成領域と異なる半導体材料を含んで構成され、絶縁層は、二乗平均平方根粗さが1nm以下の表面を有する半導体装置。

(もっと読む)

表示装置

【課題】高速動作が可能な絶縁ゲート型FETによる駆動回路で表示装置を形成し、さらに、単位画素当たりの画素電極の面積を小さくしても十分な保持容量が得られるアクティブマトリクス型表示装置を提供することを目的とする。

【解決手段】単結晶半導体を活性層とした絶縁ゲート型電界効果トランジスタによるアクティブマトリクス回路を備えた半導体装置において、前記絶縁ゲート型電界効果トランジスタ上に有機樹脂絶縁層を形成し、該有機樹脂絶縁層上に形成された遮光層と、該遮光層に密接して形成された誘電体層と、前記絶縁ゲート型電界効果トランジスタに接続された光反射性電極とから保持容量を形成する。

(もっと読む)

半導体装置の製造方法

【課題】オン抵抗の低いパワーMOS等の半導体装置を提供する。

【解決手段】ゲート酸化膜を介しゲート電極22を形成するゲート電極形成工程と、ゲート電極間よりも広い第1の開口部を有する第1のレジストパターンを形成する工程と、第1の開口部において露出している表面に第1の導電型の不純物元素をイオン注入する第1のイオン注入工程と、ゲート電極間よりも狭い第2の開口部31を有する層間絶縁膜30を形成する層間絶縁膜形成工程と、第2の開口部よりも広い第3の開口部を有する第2のレジストパターン32を形成する工程と、第3の開口部33において露出している表面に第2の導電型の不純物元素をイオン注入する第2のイオン注入工程と、を有し、第2のイオン注入工程において注入される第2の導電型の不純物元素の濃度は、第1のイオン注入工程において注入される第1の導電型の不純物元素の濃度の2倍以上であることを特徴とする。

(もっと読む)

表示装置の作製方法

【課題】液滴吐出法により吐出する液滴の着弾精度を飛躍的に向上させ、微細でかつ精度の高いパターンを基板上に直接形成することを可能にする。もって、基板の大型化に対応できる配線、導電層及び表示装置の作製方法を提供することを課題とする。また、スループットや材料の利用効率を向上させた配線、導電層及び表示装置の作製方法を提供することを課題とする。

【解決手段】液滴吐出法による液滴の吐出直前に、所望のパターンに従い基板表面上の液滴着弾位置に荷電ビームを走査し、そのすぐ後に該荷電ビームと逆符号の電荷を液滴に帯電させて吐出することによって、液滴の着弾位置の制御性を格段に向上させる。

(もっと読む)

電子機器及び電子システム

【課題】使用者が、場所を選ばず情報を閲覧、さらには画面に表示されたキーボードに直接またはスタイラスペンなどを用いて間接的に触れることにより情報を入力でき、その入力情報を利用することができる新規の電子機器を提供することを課題の一とする。

【解決手段】同一基板上に反射電極と電気的に接続する第1のトランジスタと、フォトセンサとを有し、表示部の第1画面領域に表示するタッチ入力ボタンを静止画として表示し、表示部の第2画面領域に動画として出力表示する。表示部に表示される画像が静止画である場合と、動画である場合とで異なる信号供給を表示部の表示素子に行う映像信号処理部を有し、静止画を書き込んだ後に表示素子制御回路を非動作とすることで、消費電力の節約ができる。

(もっと読む)

半導体装置及びその製造方法

【課題】貼り合わせSOI基板を使用せずに、容易なプロセスにより、高速なMIS電界効果トランジスタを提供する。

【解決手段】p型のSi基板1上に、一部に空孔4を有するシリコン酸化膜2が設けられ、空孔4を挟んでシリコン酸化膜2上に延在したp型のSOIC基板(Si)5が設けられ、シリコン窒化膜3により素子分離されている。空孔4に自己整合して、SOIC基板5上にゲート酸化膜10を介してゲート電極11が設けられ、ゲート電極11の側壁にサイドウォール12が設けられ、SOIC基板5には、ゲート電極11に自己整合してn型ソースドレイン領域(7、8)及びサイドウォール12に自己整合してn型ソースドレイン領域(6、9)が設けられ、n型ソースドレイン領域には、バリアメタル15を有する導電プラグ16を介してバリアメタル18を有するCu配線19が接続されている構造からなるNチャネルのMIS電界効果トランジスタ。

(もっと読む)

半導体装置

【課題】異なる特性の半導体素子を一体に有しつつ、高集積化が実現可能な、新たな構成の半導体装置を提供することを目的の一とする。

【解決手段】第1の半導体材料が用いられた第1のチャネル形成領域と、第1のゲート電極と、を含む第1のトランジスタと、第1のゲート電極と一体に設けられた第2のソース電極および第2のドレイン電極の一方と、第2の半導体材料が用いられ、第2のソース電極および第2のドレイン電極と電気的に接続された第2のチャネル形成領域と、を含む第2のトランジスタと、を備えた半導体装置である。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体OSを用い、オフ状態でのソースとドレイン間のリーク電流(オフ電流)が少ない書き込み用トランジスタ162、書き込み用トランジスタ162と異なる半導体材料を用いた読み出し用トランジスタ160及び容量素子164を含む不揮発性のメモリセルを有する半導体装置において、メモリセルへの情報の書き込みは、書き込み用トランジスタ162のソース電極またはドレイン電極の一方と、容量素子164の電極の一方と、読み出し用トランジスタ160のゲート電極とが電気的に接続されたノードFGに電位を供給し、ノードFGに所定量の電荷を保持させることで行う。書き込みを1×109回行う前後において、メモリセルのメモリウィンドウ幅の変化量は2%以内である。

(もっと読む)

表示装置の作製方法

【課題】表示装置の作製工程で紫外線の照射を行っても、酸化物半導体層を用いた薄膜トランジスタのしきい値電圧のシフトを低減させることができる、表示装置の作製方法を提供することを課題の一つとする。

【解決手段】少なくとも一回以上の紫外線の照射を行い、且つ酸化物半導体層を有する薄膜トランジスタをスイッチング素子として用いる、表示装置の作製方法において、全ての紫外線照射工程を終えた後で、紫外線照射による該酸化物半導体層のダメージを回復させる熱処理を行う表示装置の作製方法である。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的とする。

【解決手段】チャネル形成領域と、第1のゲート絶縁層と、第1のゲート電極と、第1のソース電極及び第1のドレイン電極と、を有する第1のトランジスタと、酸化物半導体層と、第2のソース電極及び第2のドレイン電極と、第2のゲート絶縁層と、第2のゲート電極と、を有する第2のトランジスタと、第2のソース電極または第2のドレイン電極の一方と、第2のゲート絶縁層と、第2のゲート絶縁層上に第2のソース電極または第2のドレイン電極の一方と重畳するように設けられた電極と、を有する容量素子と、を有し、第1のゲート電極と、第2のソース電極又は第2のドレイン電極の一方とは電気的に接続されている。

(もっと読む)

半導体装置

【課題】記憶保持期間において、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

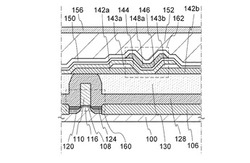

【解決手段】酸化物半導体以外の半導体材料が用いられた第1のチャネル形成領域を有する第1のトランジスタ160と、第1のトランジスタ160の上方の、酸化物半導体材料が用いられた第2のチャネル形成領域を有する第2のトランジスタ162と、容量素子164と、を有し、第2のトランジスタ162の第2のソース電極または第2のドレイン電極の一方と、容量素子164の電極の一方とは、電気的に接続される。

(もっと読む)

液晶表示装置、及び当該液晶表示装置を具備する電子機器

【課題】低消費電力化できる液晶表示装置を提供することを課題の一とする。

【解決手段】駆動回路部及び画素部を有する表示パネルと、駆動回路部を駆動する制御信号及び画素部に供給する画像信号を生成するための信号生成回路と、画像信号をフレーム期間毎に記憶する記憶回路と、記憶回路でフレーム期間毎に記憶された画像信号のうち、連続するフレーム期間の画像信号の差分を検出する比較回路と、比較回路で差分を検出した際に連続するフレーム期間の画像信号を選択して出力する選択回路と、比較回路で差分を検出した際に制御信号及び選択回路より出力される画像信号の駆動回路部への供給を行い、比較回路で差分を検出しない際に制御信号を駆動回路部への供給を停止する表示制御回路と、を有する。

(もっと読む)

半導体装置

【課題】信頼性の高いトランジスタ及びそれを用いた半導体装置を提供することを課題の一とする。

【解決手段】ゲート電極を有し、ゲート電極上にゲート絶縁膜を有し、ゲート絶縁膜上に酸化物半導体膜を有し、酸化物半導体膜上にソース電極及びドレイン電極を有し、ゲート電極に、しきい値電圧以上の電圧を印加した際にソース電極とドレイン電極間に流れる電流(オン電流)の温度依存性より求めた酸化物半導体膜の活性化エネルギーが、0meV以上25meV以下である半導体装置を提供する。

(もっと読む)

半導体装置

【課題】無線通信機能を有する半導体装置を低消費電力化又は長寿命化すること。

【解決手段】当該半導体装置は、電力供給源となる電池と、特定の回路とがチャネル形成領域が酸化物半導体によって構成されるトランジスタを介して電気的に接続することによって解決することができる。当該酸化物半導体の水素濃度は、5×1019(atoms/cm3)以下である。そのため、当該トランジスタのリーク電流を低減することができる。その結果、当該半導体装置の待機時の消費電力を低減することができる。また、これにより当該半導体装置を長寿命化することができる。

(もっと読む)

半導体装置の製造方法

【課題】半導体膜の厚みを適当な範囲に制御することによって、大きいドレイン電流を有するとともに、所望の電気的特性を備える半導体装置の製造方法、を提供する。

【解決手段】半導体装置の製造方法は、50nmを超え150nm以下の厚みを有し、第1の層7mと第2の層7nとを有する半導体膜7を形成する工程を備える。半導体膜7を形成する工程時、第1の層7mに含まれる水素の割合は、第2の層7nに含まれる水素の割合よりも小さい。半導体装置の製造方法は、半導体膜7を熱処理することによって、半導体膜7に含まれる水素を低減する工程と、ゲート絶縁膜17およびゲート電極21を形成する工程と、半導体膜7にソース領域9およびドレイン領域13を形成する工程と、半導体膜7を水素雰囲気中で熱処理することによって、半導体膜7に含まれる水素を0.5原子%以上10原子%以下に設定する工程とを備える。

(もっと読む)

スパッタリングターゲットおよびその製造方法、並びにトランジスタ

【課題】酸化物半導体膜を成膜する成膜技術を提供することを課題の一とする。

【解決手段】金属酸化物の焼結体を含み、その金属酸化物の焼結体の含有水素濃度が、たとえば、1×1016atoms/cm3未満と低いスパッタリングターゲットを用いて酸化物半導体膜を形成することで、H2Oに代表される水素原子を含む化合物、もしくは水素原子等の不純物の含有量が少ない酸化物半導体膜を成膜する。また、この酸化物半導体膜をトランジスタの活性層として適用する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、書き込み回数にも制限が無い半導体装置を提供する。

【解決手段】第1の配線と、第2の配線と、第3の配線と、第4の配線と、第1のゲート電極、第1のソース電極、および第1のドレイン電極を有する第1のトランジスタ160と、第2のゲート電極、第2のソース電極、および第2のドレイン電極を有する第2のトランジスタ162と、を有し、第1のトランジスタ160は、半導体材料を含む基板に設けられ、第2のトランジスタ162は酸化物半導体層を含んで構成される。

(もっと読む)

半導体装置

【課題】安定した電気特性を有する薄膜トランジスタを有する電位保持機能の高い固体撮像素子を提供する。

【解決手段】酸化物半導体層を用いて薄膜トランジスタのオフ電流を1×10−13A以下とし、該薄膜トランジスタを固体撮像素子のリセットトランジスタ及び転送トランジスタの両方に用いることで信号電荷蓄積部の電位が一定に保たれ、ダイナミックレンジを向上させることができる。また、周辺回路に相補型金属酸化物半導体素子が作製可能なシリコン半導体を用いることで高速かつ低消費電力の半導体装置を作製することができる。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極を形成してからチャネル形成用半導体部を形成する方法において、結晶品質の良い単結晶Siを用いて良質なゲート絶縁膜を形成した縦型半導体装置を提供する。

【解決手段】単結晶半導体基板に少なくとも第1絶縁層を有する積層体を形成する工程S1と、前記積層体に、前記単結晶半導体基板が露出する孔を形成する工程S2と、前記孔の底面に露出している前記単結晶半導体基板を種結晶領域とすることにより、前記第1絶縁層の上にゲート電極となる単結晶半導体部を形成する工程S3と、前記孔内に埋められた前記単結晶半導体部を除去することで、前記孔の底面に前記単結晶半導体基板を再び露出させる工程S4と、前記単結晶半導体部の前記孔の側面に露出している部分にゲート絶縁膜を形成する工程S5と、前記孔にチャネル形成用半導体部を形成する工程S6と、を有する半導体装置の製造方法。

(もっと読む)

81 - 100 / 186

[ Back to top ]