Fターム[5F110HL27]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−コンタクトホール介在 (16,138) | 電極、配線の製法 (3,290) | 電極、配線形成後の処理 (186)

Fターム[5F110HL27]に分類される特許

121 - 140 / 186

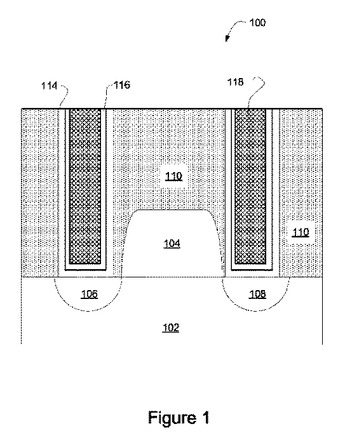

金属−絶縁体−半導体トンネリングコンタクト

本発明はソース領域又はドレイン領域へのコンタクトに関する。コンタクトは導電性材料を有するが、その導電性材料は絶縁体によりソース領域又はドレイン領域から分離されている。  (もっと読む)

(もっと読む)

半導体装置、およびその作製方法

【課題】酸化物半導体を用いた半導体装置を提供するに際し、酸化物半導体層と電極層との接触抵抗を低減することを課題の一とする。

【解決手段】ゲート絶縁層上方の第1のソース電極層または第1のドレイン電極層と、ゲート絶縁層上方の酸化物半導体層と、酸化物半導体層、および第1のソース電極層または第1のドレイン電極層上方の第2のソース電極層または第2のドレイン電極層と、を有し、酸化物半導体層の下面は、ゲート電極層と重畳する領域においてゲート絶縁層と接しており、且つ、少なくとも他の一部の領域において第1のソース電極層または第1のドレイン電極層と接しており、酸化物半導体層の上面は、その一部の領域において第2のソース電極層または第2のドレイン電極層と接しており、第1のソース電極層または第1のドレイン電極層は、第2のソース電極層または第2のドレイン電極層と電気的に接続している。

(もっと読む)

回路基板、アクティブマトリクス回路基板及び画像表示装置

【課題】コスト的な利点の多いスクリーン印刷法を用いて、平面性及びサイズの均質性に優れた上部電極を有する回路基板を提供する。

【解決手段】基板1と、基板1上に形成される複数の下部電極4と、基板1上に形成され、複数の下部電極4のそれぞれの上に開口部9を有する層間絶縁膜6と、複数の開口部9のそれぞれを埋めるように形成され、複数の下部電極4のそれぞれと電気的に接続される上部電極7とを有する回路基板20において、層間絶縁膜6は、一の開口部9と、該一の開口部9に最も近接する開口部9又は次に近接する開口部9との略中間点で、基板表面からの高さが極大高さdとなる極大点Cを備える曲面形状を有し、開口部9での上部電極7の基板表面からの高さtが、極大点Cの極大高さdよりも小さいことを特徴とする

(もっと読む)

有機トランジスタアレイ、表示パネル及び表示装置

【課題】オフ電流を低減することが可能な有機トランジスタアレイ、表示パネル及び表示装置を提供する。

【解決手段】マトリクス状に設けられている走査線11及び信号線12と、走査線11と接続するゲート電極21と、ゲート電極21及び走査線11を覆うように形成されている第1のゲート絶縁膜と、信号線12と接続するソース電極23と、チャネル領域Cを挟んでソース電極23と対向して形成されているドレイン電極24と、チャネル領域Cに形成されている有機半導体層25とを備え、走査線11及び信号線12が交差して形成されている画素領域A1、A2に設けられる有機トランジスタ20とを有する有機トランジスタアレイ10において、ゲート電極21は、更に平面視でドレイン電極24と信号線12とに挟まれる領域Sに形成され、有機半導体層25は、更に平面視でドレイン電極24と信号線12に挟まれる領域S1に形成されている。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタの製造方法、薄膜トランジスタアレイ及び画像表示装置

【課題】溶剤乾燥や熱硬化のための熱処理工程を用いずに形成した欠陥の少ない絶縁層を有する薄膜トランジスタ、薄膜トランジスタの製造方法、薄膜トランジスタアレイ及び画像表示装置を提供すること。

【解決手段】バンプ107と、バンプ107により貫通される層間絶縁層105とを含む薄膜トランジスタにおいて、バンプ107がフッ素化合物を含み、層間絶縁層105がフィルム状ホットメルト接着剤の加熱圧着により形成され、バンプがフッ素化合物を含み、フッ素含有量が、0.01wt%以上5wt%以下であることを特徴とする薄膜トランジスタ。

(もっと読む)

半導体装置およびその作製方法

【課題】インジウム(In)、ガリウム(Ga)、及び亜鉛(Zn)を含む酸化物半導体膜を用いる薄膜トランジスタにおいて、ソース電極層またはドレイン電極層のコンタクト抵抗を低減した薄膜トランジスタ及びその作製方法を提供することを課題の一つとする。

【解決手段】ソース電極層及びドレイン電極層上にIGZO半導体層を設け、ソース電極層及びドレイン電極層とゲート絶縁層との間に、IGZO半導体層よりも酸素濃度の低いソース領域及びドレイン領域を意図的に設けることによってオーミック性のコンタクトを形成する。

(もっと読む)

半導体装置、ウエハ構造体および半導体装置の製造方法

【課題】放熱効率を向上し且つ歩留りや信頼性の低下を防止することが可能な半導体装置および半導体装置の製造方法を提供する。

【解決手段】裏面に凹部DP1が形成されたシリコン基板101と、シリコン基板101における裏面と反対側の上面上に成長されたp型半導体層103と、p型半導体層103の上方または側方に互いに離間して形成されたソース電極108sおよびドレイン電極108dと、を含むMOSFETと、を備える。p型半導体層103は、シリコン基板101に対して格子定数および熱膨張係数のうち少なくとも1つが異なる。凹部DP1は、シリコン基板101の厚み方向から見て少なくともソース電極108sおよびドレイン電極108dで挟まれた領域を内包する領域に形成されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】高誘電率膜をゲート絶縁膜として用いたCISトランジスタの信頼性を向上する。

【解決手段】基板1の主面には、素子分離領域2によって互いに絶縁分離されたpMISトランジスタの活性領域およびnMISトランジスタの活性領域が設けられている。素子分離領域2に係るようにnMISトランジスタの活性領域上にnMISトランジスタのゲート絶縁膜を構成するハフニウム系酸化膜5が設けられており、そのハフニウム系酸化膜5と素子分離領域2上で接触し、pMISトランジスタの活性領域上にハフニウム系酸化膜5と異なる材料から構成されるpMISトランジスタのゲート絶縁膜を構成するハフニウム系酸化膜9が設けられている。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】 真性酸化亜鉛からなる半導体薄膜を有する薄膜トランジスタの製造に際し、加工精度を良くする。

【解決手段】 まず、真性酸化亜鉛からなる半導体薄膜8の上面全体に保護膜9を形成し、その上に上層絶縁膜12を成膜する。次に、上層絶縁膜12および保護膜9にコンタクトホール10、11を形成する。この場合、チャネル長Lは2つのコンタクトホール10、11間の間隔により決定され、チャネル幅Wはコンタクトホール10、11の所定方向の寸法により決定される。これにより、半導体薄膜8にサイドエッチングがやや生じても、チャネル長Lおよびチャネル幅Wに寸法変化が生じることはない。

(もっと読む)

薄膜トランジスタ及びその製造方法、ならびに薄膜トランジスタを備える平板表示装置

【課題】本発明は、酸素を含む化合物半導体を活性層とする薄膜トランジスタ及びその製造方法、ならびに薄膜トランジスタを備える平板表示装置を提供する。

【解決手段】基板上に形成されたゲート電極と、ゲート絶縁膜によりゲート電極から絶縁され、酸素を含む化合物半導体からなる活性層と、活性層上に形成された保護層と、活性層と接触するソース電極及びドレイン電極とを備え、保護層が、酸素との結合力を有する無機物を含む酸化物からなる。

(もっと読む)

配線の作製方法及び表示装置の作製方法

【課題】配線の凹凸やコンタクト不良を大幅に低減した配線の作製方法を用いることによって半導体装置の信頼性を向上させること。

【解決手段】層間絶縁膜207に設けられた開口部に液滴吐出法を用いてノズル208から導電性組成物が分散された液滴209を滴下し配線210を形成する。さらに、加熱処理を行うことで配線210をリフローする。これにより、配線表面を平坦化し、且つ配線のコンタクト不良を改善することができる。

(もっと読む)

表示装置用Al合金膜、表示装置およびスパッタリングターゲット

【課題】低温での熱処理後も十分に低い電気抵抗率を示し、かつ直接接続された透明画素電極とのコンタクト抵抗が十分に低減されると共に、耐食性および耐熱性に優れた表示装置用Al合金膜を提供する。

【解決手段】表示装置の基板上で、透明導電膜と直接接続されるAl合金膜であって、該Al合金膜は、Niを0.05〜0.5原子%、Geを0.4〜1.5原子%、および希土類元素群から選ばれる少なくとも1種の元素を合計で0.05〜0.3原子%含有すると共に、NiおよびGeの合計量が1.7原子%以下である。

(もっと読む)

電気光学装置、電気光学装置の製造方法、および投射型表示装置

【課題】コンタクトホールを埋める工程を利用して、隣接する画素電極の間に発生する凹部を平坦化した電気光学装置、その製造方法、およびかかる電気光学装置を用いた投射型表示装置を提供する。

【解決手段】電気光学装置において、画素電極9aは、下層側に島状に形成された第1電極91aと、第1電極91a上に島状に形成された上層側の第2電極92aとによって構成されている。第1電極91aの上層には絶縁膜73が積層され、かかる絶縁膜73によって、コンタクトホール72b内の凹部は完全に埋められ、隣接する第1電極91aの間も埋められている。従って、絶縁膜73の表面と、第1電極91aにおいて絶縁膜73から露出している表面とは連続した平坦面を構成しており、かかる平坦面上に第2電極72aが形成されている。

(もっと読む)

回路基板の製造方法、回路基板、アクティブマトリックス回路基板、画像表示装置

【課題】層間絶縁膜にコンタクトホール有する回路基板を安価に提供する。

【解決手段】多層配線からなる回路基板であって、層間絶縁膜を介し下部電極と上部電極とが接続されるコンタクトホールがマトリックス状に二次元的に配列されている回路基板の形成方法において、二次元的に配列されている所定の形状のペースト吐出領域を有するスクリーン版であって、スクリーン版において近接する3つ以上のペースト吐出領域から吐出した絶縁ペースト同士がダレにより二次元的に接合することによりコンタクトホールが形成されるように印刷を行う印刷工程と、印刷された絶縁ペーストを硬化させる硬化工程とを含むことを特徴とする回路基板の形成方法を提供することにより上記課題を解決する。

(もっと読む)

薄膜半導体装置およびその製造方法

【課題】膜厚バラツキを抑制し、かつドライエッチングダメージの発生を抑制できる優れた素子特性を兼ね備えた薄膜半導体装置及びその製造方法を提供すること。

【解決手段】透明絶縁性基板上に形成され、所定の間隔を隔てて第1導電型の不純物を含むソース領域及び第1導電型の不純物を含むドレイン領域を有する島状半導体層、前記ソース領域及びドレイン領域の間の島状半導体層上に形成されたゲート絶縁膜及びゲート電極、前記ゲート電極の側壁に形成された、低温酸化膜、低温窒化膜及び低温酸化膜の3層構造のサイドウォールスペーサー、及び島状半導体層及びゲート電極を覆う層間絶縁膜を具備することを特徴とする。

(もっと読む)

薄膜半導体装置およびその製造方法

【課題】 優れたコンタクト特性及び優れた素子特性を持った薄膜半導体装置及びその製造方法を提供すること。

【解決手段】 透明絶縁性基板上に形成され、所定の間隔を隔てて不純物を含むソース領域ドレイン領域を有する島状半導体層、前記ソース領域及びドレイン領域の間の島状半導体層上に形成されたゲート絶縁膜、前記ゲート絶縁膜上に形成されたゲート電極、前記島状半導体層及びゲート電極を覆う層間絶縁膜、前記ソース領域及びドレイン領域にそれぞれ接続する、前記層間絶縁膜に形成されたコンタクト孔内にそれぞれ埋め込まれた不純物を含む多結晶半導体層、及び前記多結晶半導体層に接続する高融点金属層を含む配線層を具備し、前記多結晶半導体層と配線層の高融点金属層との間には、高融点金属と半導体との化合物からなる薄層が形成されていることを特徴とする。

(もっと読む)

TFT基板及びそれを用いた液晶表示装置並びにそれらの製造方法

【課題】信頼性が向上するTFT基板及びそれを用いた液晶表示装置並びにそれらの製造方法を提供すること。

【解決手段】本発明にかかるTFTアレイ基板1は、外部から接続可能なゲート配線端子28及びゲート配線端子28から延在するゲート配線6を構成する透明導電膜3aを有する。さらに、TFTアレイ基板1は、ゲート配線端子28上では除去され、透明導電膜3a上において透明導電膜3aのパターンの内側に形成された金属膜3bを有する。また、金属膜3bは、ゲート絶縁膜15によって覆われる。

(もっと読む)

半導体素子

【課題】インバータ回路など、電気接続された2つの半導体スイッチによるスイッチング動作を行なうための電気回路において、寄生インダクタンスおよびオン抵抗を抑制することができる構造の半導体素子を提供すること。

【解決手段】この半導体素子は、基板1と、基板1の一方側に形成される半導体積層構造部2とを備える。半導体積層構造部2は、n型層5、このn型層5の一方側(下面側)に積層されたp型層4、およびこのp型層4に積層されたn型層3からなる縦型npn構造の第1半導体積層構造8と、n型層5をこの第1半導体積層構造8と共有し、n型層5、このn型層5の他方側(上面側)に積層されたp型層6、およびこのp型層6に積層されたn型層7からなる縦型npn構造の第2半導体積層構造9とを備える。

(もっと読む)

アレイ基板

【課題】 2層配線を有するアレイ基板において、層間絶縁膜の段差部における第2配線層のエッチング残りを抑制する。

【解決手段】 表示部(表示領域H)と、その周囲に配される額縁部とを有するアレイ基板である。額縁部は、薄膜トランジスタ等により構成される駆動回路を備える。また、薄膜トランジスタと接続されるソース電極及びドレイン電極を含む第1配線層17と、第1配線層17上に第2層間絶縁膜18を介して形成される第2配線層19とを有する。第2配線層19は、Alを含むAl配線層19aと、Al配線層19aの表面を覆うトップバリアメタル層19bとから構成され、Al配線層19aの底面を覆うボトムバリアメタル層が形成されていない。

(もっと読む)

ゲート絶縁膜、薄膜トランジスタ基板及びその製造方法

【課題】薄膜トランジスタが有する特性のよいゲート絶縁膜、及びそのゲート絶縁膜を有する薄膜トランジスタ基板及びその製造方法を提供する。

【解決手段】シリコン薄膜トランジスタ基板が有する酸化ケイ素からなるゲート絶縁膜であって、ゲート電圧を正電圧から負電圧に掃引したとき、ゲート電極からゲート絶縁膜中に流れ込むゲートリーク電流の値が正から負に変わる時のゲート電圧値と、ゲート電圧を負電圧から正電圧に掃引したとき、ゲート電極からゲート絶縁膜中に流れ込むゲートリーク電流の値が負から正に変わる時のゲート電圧値との差ΔV(V)が、ゲート絶縁膜の厚さd(nm)との関係で、[ΔV/d]<0.0045であるように構成する。

(もっと読む)

121 - 140 / 186

[ Back to top ]