Fターム[5F110HM12]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−共通 (7,931) | 配置 (4,297) | 非対称 (1,159)

Fターム[5F110HM12]に分類される特許

141 - 160 / 1,159

薄膜トランジスタアレイパネル

【課題】薄膜トランジスタアレイパネルにおいて、酸化シリコン膜の厚さを減少させる。

【解決手段】本発明の実施形態に係る薄膜トランジスタアレイパネルは、絶縁基板と、絶縁基板上に配置され、ゲート電極を含むゲート線と、ゲート線上に配置され、窒化シリコンを含む第1ゲート絶縁膜と、第1ゲート絶縁膜上に配置され、酸化シリコンを含む第2ゲート絶縁膜と、第2ゲート絶縁膜上に配置される酸化物半導体と、酸化物半導体上に配置され、ソース電極を含むデータ線と、酸化物半導体上に配置され、ソース電極と対向するドレイン電極と、ドレイン電極と接続される画素電極と、を含み、第2ゲート絶縁膜の厚さは200Å以上500Å未満であることを特徴とする。

(もっと読む)

横型素子を有する半導体装置

【課題】高速スイッチング動作を行う場合でも、アバランシェブレークダウンを抑制でき、スイッチング損失低減や素子破壊を抑制することが可能な構成とする。

【解決手段】横型FWD7などの横型素子において、SRFP21の全抵抗Rの抵抗値を90kΩ〜90MΩ、好ましくは270kΩ〜27MΩ、より好ましくは900kΩ〜9MΩとすることにより、2ndピーク時のアノード電流IAなどの電流が大きくなることを抑制できる。これにより、高速スイッチング動作を行う場合でもアバランシェブレークダウンを抑制でき、横型FWD7のスイッチング損失低減や素子破壊を抑制することが可能となる。

(もっと読む)

半導体装置

【課題】従来に比してオン電圧性能に優れた横型IGBT、および順方向電圧特性に優れた横型FWDを同一基板上に構成可能とする半導体装置を提供する。

【解決手段】半導体基板上において、横型IGBTと、横型FWDとが、絶縁体であるトレンチ絶縁仕切り部を挟むように横方向に隣接配置されて成る半導体装置であって、横型IGBTは、平面視した場合に、エミッタ領域と当該横型IGBTのドリフト領域との境界面の幅がコレクタ領域と当該横型IGBTのドリフト領域との境界面の幅より狭くなるよう形成されており、横型FWDは、平面視した場合に、カソード領域と当該横型FWDのドリフト領域との境界面の幅がアノード領域と当該横型FWDのドリフト領域との境界面の幅より狭くなるよう形成されていることを特徴とする、半導体装置。

(もっと読む)

半導体装置及びその製造方法

【課題】Cdsubの低減化を通じて、出力容量Cossの低減化に寄与する半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1とこの半導体基板1上に埋め込み絶縁層を介して形成された第1導電型の半導体層とを有するSOI基板と、第1導電型の半導体層からなる活性領域3内に形成された素子領域と、素子領域の少なくとも1つに接続される外部取り出し用の電極(ドレインパッド9p)とを有する半導体装置において、外部取り出し用の電極9p下に位置する活性領域が、埋め込み絶縁層2に到達するように形成された絶縁分離領域11で囲まれており、絶縁分離領域11で分離された活性領域3と、外部取り出し用の電極9pとの間に絶縁体13が配されたことを特徴とする。

(もっと読む)

表示装置及び表示装置の製造方法

【課題】映像品質が向の上された表示装置とその製造方法が提供される。

【解決手段】本発明による表示装置は複数の画素を有し、各画素は第1絶縁基板の上に具備されたゲート電極と、ゲート電極をカバーし、第1絶縁基板の上に具備されたゲート絶縁膜と、ゲート絶縁膜の上にゲート電極とオーバーラップして配置された半導体パターンと、半導体パターンの上に互に離隔されて具備されたソース電極とドレイン電極と、ゲート絶縁膜の上に配置され、その一部がドレイン電極と接触する透明画素電極、透明画素電極の上に形成された保護層、及び第1絶縁基板と第1絶縁基板に対向する第2絶縁基板の中でいずれか1つに具備され画素電極と電界を形成する共通電極を含む。

(もっと読む)

半導体装置およびその作製方法

【課題】新規な構造の半導体装置あるいはその作製方法を提供することを課題とする。例えば、高電圧若しくは大電流で駆動されるトランジスタの信頼性向上を図ることを課題とする。

【解決手段】トランジスタの信頼性向上を図るため、電界集中を緩和するバッファ層をドレイン電極層(またはソース電極層)と、酸化物半導体層との間に設け、バッファ層の端部をドレイン電極層(またはソース電極層)の側面から突出させた断面形状とする。バッファ層は、単層又は複数の層からなる積層で構成し、例えば窒素を含むIn−Ga−Zn−O膜、窒素を含むIn−Sn−O膜、SiOxを含むIn−Sn−O膜などを用いる。

(もっと読む)

表示装置の駆動方法

【課題】酸化物半導体を半導体層として具備するトランジスタにおいて、当該トランジスタの特性劣化を回復することの出来る表示装置の駆動方法を提供する

【解決手段】複数のフレーム期間により画像表示を行う表示装置の駆動方法において、各フレーム期間における複数の走査線のうち、いずれか一の走査線を選択する期間で駆動用素子であるトランジスタに対し、ゲートに20V以上の電圧を1m秒以上印加できるよう駆動する。そして複数のフレーム期間にわたって、各行を選択していくことで全ての駆動用素子であるトランジスタに対し、ゲートに20V以上の電圧を1m秒以上印加できるようにしてトランジスタの特性劣化を回復するものである。

(もっと読む)

窒化物半導体装置

【課題】ゲート電極から染み出した金属がドレイン電極に到達することを抑制して、ドレイン−ゲート間の絶縁破壊を抑制する窒化物半導体装置を提供する。

【解決手段】ゲート電極5の直下に位置するAlGaN層22と、このAlGaN層22の直上に位置する絶縁膜30との間の界面Sに、ゲート電極5とドレイン電極1との間に位置するように、溝50を設けている。ゲート電極5から界面Sを伝ってドレイン電極1側へ染み出した金属を、溝50によって、堰き止めることができる。

(もっと読む)

電荷注入特性が高い有機薄膜トランジスタ

【課題】トランジスタ特性が優れ、しかも大面積化が容易なボトムゲート・ボトムコンタクト構造の有機薄膜トランジスタ、及びその製造方法を提供すること。

【解決手段】第1導電層及び第2導電層からなるソース・ドレイン電極を有するボトムゲート・ボトムコンタクト構造の有機薄膜トランジスタであって、該第1導電層は、塗布法を用いて形成されたものであり、該第1導電層の端部は該第2導電層の端部と比較して電極ブロックの内側に位置している有機薄膜トランジスタ。

(もっと読む)

電気光学装置、電気光学装置の製造方法、電子機器

【課題】入射光が確実に遮光され安定した動作が得られるトランジスターを備えた電気光学装置、電気光学装置の製造方法、この電気光学装置を備えた電子機器を提供すること。

【解決手段】電気光学装置は、ソース領域30sと、ドレイン領域30dと、チャネル領域30cと、チャネル領域30cとドレイン領域30dの間に形成された接合領域30fとを有する半導体層30aと、半導体層30aを覆う第1絶縁膜を介してチャネル領域30cに対向するゲート電極部30gと、平面的に接合領域30fに沿って第1絶縁膜および第2絶縁膜に設けられた溝としてのコンタクトホールCNT5,CNT6と、コンタクトホールCNT5,CNT6内に、ゲート電極部30gから延在して設けられる第1導電膜と、データ線6aを構成する第2導電膜とを含む少なくとも2層の導電膜を有する遮光性の側壁部と、を備えた。

(もっと読む)

半導体装置

【課題】本願発明で開示する発明は、従来と比較して、さらに結晶成長に要する熱処理時間を短縮してプロセス簡略化を図る。

【解決手段】

一つの活性層204を挟んで二つの触媒元素導入領域201、202を配置して結晶化を行い、触媒元素導入領域201からの結晶成長と、触媒元素導入領域202からの結晶成長とがぶつかる境界部205をソース領域またはドレイン領域となる領域204bに形成する。

(もっと読む)

パワー絶縁ゲート型電界効果トランジスタ

【課題】酸化物半導体を用いたパワーMISFETを提供する。

【解決手段】半導体層101を挟んでゲート電極102aとソース電極103a、ドレイン電極103bを形成し、半導体層のうちゲート電極102aとドレイン電極103bとの間にこれらが重ならない領域を設ける。この領域の長さを0.5μm乃至5μmとする。このようなパワーMISFETのドレイン電極とソース電極の間に100V以上の電源と負荷を直列に接続し、ゲート電極102aに制御用の信号を入力して使用する。

(もっと読む)

液晶表示装置、及びその作製方法

【課題】作製工程を削減し、低コストで生産性の良い液晶表示装置を提供する。消費電力が少なく、信頼性の高い液晶表示装置を提供する。

【解決手段】島状半導体層を形成するためのフォトリソグラフィ工程及びエッチング工程を省略し、ゲート電極(同一層で形成される配線等を含む)を形成する工程、ソース電極及びドレイン電極(同一層で形成される配線等含む)を形成する工程、コンタクトホールを形成する(コンタクトホール以外の絶縁層等の除去を含む)工程、画素電極(同一層で形成される配線等を含む)を形成する工程の4つのフォトリソグラフィ工程で液晶表示装置を作製する。コンタクトホールを形成する工程において、半導体層が除去された溝部を形成することで、寄生チャネルの形成を防ぐ。

(もっと読む)

縮合芳香族化合物、有機半導体材料及び有機トランジスタ

【課題】再配向エネルギーが十分に小さい有機化合物の提供。

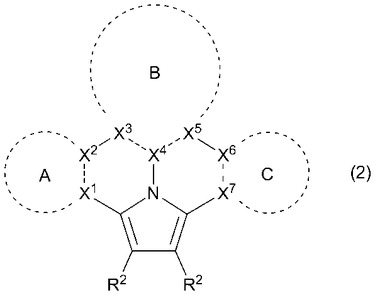

【解決手段】式

[式中、A環、B環及びC環は、各々独立して、芳香環を表す。X1、X2、X3、X4、X5、X6及びX7は、各々独立して、炭素原子又は窒素原子を表す。]で表される縮合芳香族化合物、又は式(2)で表される縮合芳香族化合物から水素原子を2個除いた2価の基を繰り返し単位として有する高分子化合物。

(もっと読む)

発光表示装置及び発光表示装置の作製方法

【課題】薄く、軽量であり且つ破壊が生じにくい発光表示装置を、作製工程を大幅に削減して低コストで作製する方法を提供する。

【解決手段】剥離層を介して基板上に素子領域を形成する際に、半導体層のエッチングと、画素電極とドレイン電極を接続するためのコンタクトホールの形成を、同一のフォトリソグラフィ工程及びエッチング工程で行う。更に素子領域を基板から剥離して、じん性の高い第1の支持体に設け、第1の支持体及びじん性の高い第2の支持体で液晶素子を挟持することで、薄く、軽量であり且つ破壊が生じにくい発光表示装置を、作製工程を大幅に削減して低コストで作製できる。

(もっと読む)

アレイ基板およびその製造方法、並びに液晶ディスプレー

【課題】ソース・ドレイン電極と別体に形成された拡張導電部によって、TFTスイッチング素子の有効チャネル長を短くする。

【解決手段】アレイ基板であって、ベース基板を有し、ベース基板に縦横に交差するデータラインとゲートラインが形成されてマトリックス状に配列する複数の画素ユニットが画成され、各画素ユニットにスイッチング素子が設置される。各スイッチング素子は、ゲート電極、活性層、ソース電極およびドレイン電極と、拡張導電部とを有し、前記ソース電極と前記ドレイン電極の前記活性層に接触する端部は対向してチャネル領域を定義し、前記拡張導電部は、前記ソース電極または前記ドレイン電極に隣接して電気的に接触し、前記拡張導電部の端部は、前記拡張導電部に接触するソース電極またはドレイン電極を超え、前記チャネル領域内に延び、少なくとも前記チャネル領域内で前記活性層に接触する。

(もっと読む)

横型の絶縁ゲート型バイポーラトランジスタ

【課題】更なるスイッチング動作の高速化を図ることが可能な構造の横型IGBTを提供する。

【解決手段】コレクタ電極12がp+型領域4aに対してオーミック接触させられ、かつ、p型領域4bに対してショットキー接触させられるようにする。具体的には、コレクタ電極12とp型領域4bとの接触部位が確実にショットキー接触となるように、p型領域4bの表面上にバリア金属12aを配置する。これにより、コレクタ側からのホールの注入を抑制して低注入効率となるようにでき、ライフタイム制御を行わなくてもスイッチング動作を更に高速化することが可能な構造の横型IGBTとすることができる。

(もっと読む)

横型半導体装置

【課題】高い耐圧性能と長期信頼性を両立可能な半導体装置を提供する。

【解決手段】半導体基板の一主表面上においてドリフト領域を挟むように第1電極部と第2電極部とが各々分離形成され、ドリフト領域上部には酸化膜層が形成され、ドリフト領域、第1電極部、第2電極部、および酸化膜層が層間絶縁膜層により覆われた横型半導体装置であって、第1導電型半導体と第2導電型半導体とを交互にドリフト領域におけるキャリアのドリフト方向へ直列接続して成る連続接合半導体層が酸化膜層と層間絶縁膜層との境界部に設けられ、連続接合半導体層の一方端部は、第2電極部と並列に電源電位線に接続されていることを特徴とする、横型半導体装置である。

(もっと読む)

半導体装置の作製方法及び液晶表示装置の作製方法

【課題】作製工程を増やすことなく、凹凸形状の画素電極を作製することを目的とする。

【解決手段】凸部は、フォトマスクを用いて作製すると再現性の高いものが得られるため、画素TFT1203の作製工程にしたがって作製すればよい。画素TFT1203の作製と同様に積層される半導体層、ゲート絶縁膜および導電膜を積層して凸部を形成する。こうして形成された凸部および同一工程で形成された画素TFT、駆動回路に含まれるTFTを覆うように層間絶縁膜を形成する。凹凸を有する層間絶縁膜が形成されたら、その上に画素電極を形成する。画素電極の表面も絶縁膜の凹凸の影響を受け表面が凹凸化する。

(もっと読む)

高電圧薄膜トランジスタを使用するMEMS装置のための集積化ドライバ電子工学

【課題】作動MEMS装置及び該作動MEMS装置を制御するためのドライバ回路を提供する。

【解決手段】ドライバ回路は、基板上に形成される複数の高電圧薄膜トランジスタ(HVTFT)を含み、各HVTFTは、制御ゲート電極、ソース電極、及び、該ソース電極が制御ゲート電極から第1の距離だけ離れるように配置されたドレイン電極を含む。このドレイン電極は、ドレイン電極のいずれか一部及び制御ゲート電極の間の最短距離が第1の距離より十分に大きいように、ドレイン電極及びソース電極間の第1の破壊電圧が制御ゲート電極及びソース電極間の第2の破壊電圧より大きいように、制御ゲート電極から離間される。複数の作動MEMS装置は、上記基板上に形成され、複数のHVTFTのうちの関連したHVTFTのドレイン電極にそれぞれ接続される。

(もっと読む)

141 - 160 / 1,159

[ Back to top ]