Fターム[5F110HM12]の内容

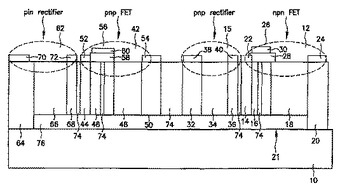

薄膜トランジスタ (412,022) | ソース、ドレイン−共通 (7,931) | 配置 (4,297) | 非対称 (1,159)

Fターム[5F110HM12]に分類される特許

1,141 - 1,159 / 1,159

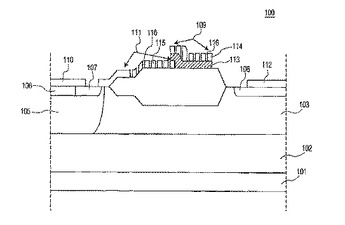

テーパ状単位セル金属酸化物半導体高電圧デバイス構造

電界効果電子デバイス(100,600)(例えばVDMOS等のFET)は、誘電体層(104,608)に隣接して配置されたフィールドプレート(105,607)を有しており、当該フィールドプレートは、半導体層(103,602)に隣接して配置されている。この場合、デバイスのドリフト領域は半導体層中にある。ドーピングレベルはドリフト領域に亘って略非線形的に変化し、デバイスは略一定の低減された表面電界を示す。電界効果デバイスの製造方法は、デバイスの半導体層のドリフト領域に非線形で不均一なドーピング密度を与えることを含んでいる。この場合、半導体層及び誘電体層の両方が一定でない厚さを有している。誘電体層は、low−k誘電材料によって形成され得る。  (もっと読む)

(もっと読む)

コンプリメンタリ横型窒化物トランジスタ

基板の支持表面上に形成された、横方向に隣接した導電性半導体領域により構成された横方向に延びているスタックを備える半導体デバイスおよびそのデバイスを作製する方法。  (もっと読む)

(もっと読む)

垂直型FIN−FETMOSデバイス

【課題】 トランジスタ本体として働く垂直方向のシリコン「フィン」を用いて、低い接触抵抗を持つ高密度の垂直型Fin−FETデバイスを生成すること。

【解決手段】 低い接触抵抗を示す新しいクラスの高密度の垂直型Fin−FETデバイスが説明される。これらの垂直型Fin−FETデバイスは、トランジスタ本体として働く垂直方向のシリコン「フィン」(12A)を有する。ドープされたソース領域及びドレイン領域(26A、28A)が、それぞれフィン(12A)の下部及び上部内に形成される。ゲート(24A、24B)が、フィンの側壁に沿って形成される。適切なバイアスがゲート(24A、24B)に印加されると、電流は、ソース領域(26A)とドレイン領域(28A)との間で、フィン(12A)を通して垂直方向に流れる。pFET、nFET、マルチ・フィン、シングル・フィン、マルチ・ゲート、及びダブルゲートの垂直型Fin−FETを同時に形成するための統合プロセスが説明される。

(もっと読む)

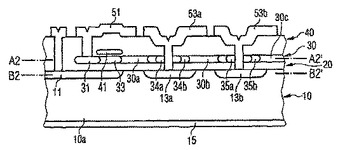

相補的窒化膜トランジスタの垂直およびコモンドレイン

【課題】少ない材料で、電流搬送能力に優れた半導体デバイスを提供する。

【解決手段】 異なる平面に、オーミック接点を含む半導体デバイス、およびそのデバイスを製造するための方法であって、連続したステップで、異なる導電タイプの半導体層の半導体スタックをエッチングし、第1半導体層内に、第1の幅の第1開口部を形成し、別の半導体層を露出させ、次に別の層内に、より狭い幅の第2開口部を形成し、オーミック接点を収容するための別の層の一部を、露出した状態で残すことを含む。

(もっと読む)

マルチゲート構造の半導体素子及びその製造方法

本発明は、複数のスラブを含むメサ型活性領域を有する半導体素子及びその製造方法を提供する。相互連結されている第1活性領域及び第2活性領域を備え、第1活性領域は基板上にライン・アンド・スペースパターン状に形成され、相互逆方向である第1側面、第2側面及び上面をそれぞれ有する複数のスラブから構成され、第2活性領域は第1活性領域とは同じであるか、または異なる物質からなり、複数のスラブを相互連結させるように、基板上でスラブの少なくとも一端部に接して延びている半導体素子である。該半導体素子を製造するために、まず、ライン・アンド・スペースパターン状の第1活性領域を基板上に形成した後、第2活性領域を形成する。  (もっと読む)

(もっと読む)

スペーサによって定められる通路内で成長した半導体ナノチューブを組み込んだ垂直型電界効果トランジスタ

【課題】 ICチップの大量生産技術に対応した、チャネル領域として1つ又は複数の半導体カーボン・ナノチューブを組み込んだ垂直型FET構造体を提供する。

【解決手段】 少なくとも1つの半導体ナノチューブによって定められたチャネル領域を有する垂直型電界効果トランジスタ、及び、こうした垂直型電界効果トランジスタを、スペーサによって定められるチャネルを用いて化学気相成長法によって製造する方法である。各々のナノチューブは、スペーサとゲート電極との間に定められる高アスペクト比通路の底部に位置決めされた触媒パッドにより触媒される化学気相成長法によって、成長する。各々のナノチューブは、スペーサによる境界の存在によって制限される垂直配向を持つ通路内で成長する。通路の開口部から離れたスペーサの底部に、隙間が設けられる。隙間を通って触媒パッドに流れる反応物質が、ナノチューブの成長に関与する。

(もっと読む)

絶縁耐力の高いSOI半導体素子

本発明は、第1半導体域と第2半導体域との間に配置されたフィールド電極および/またはフィールド領域を備えた、SOI半導体素子に関するものである。電気的結合を、フィールド電極とフィールド領域との間で行うことができる。  (もっと読む)

(もっと読む)

電界効果トランジスタ及びそれを用いた表示装置

有機物を含有する半導体層(15)と、少なくとも互いに電気的に非接触である第一電極(16)、第二電極(12)及び第三電極(14)を含む電界効果トランジスタであって、半導体層(15)の上方に第一電極(16)が配置され、半導体層(15)の下方に第二電極(12)が配置され、半導体層(15)の側方に第三電極(14)が配置され、半導体層(15)は第一電極(16)、第二電極(12)及び第三電極(14)から選ばれるいずれか2つの電極と電気的に接合され、各電極(12,14,16)間には電気的絶縁体層(13,17)を介在させ、第一電極(16)は半導体層(15)の上方を半導体層(15)の外周部より外側にはみ出して覆っている。これにより、有機半導体を用いた電界効果トランジスタであっても、空気や水に強く、かつ長寿命な電界効果トランジスタ及びそれを用いた表示装置を提供する。 (もっと読む)

ヘテロ接合を備える半導体デバイス

ヘテロ接合を有する半導体デバイス。このデバイスは、基板と少なくとも1つのナノ構造とを備える。この基板とナノ構造とは、異なる材料から成る。この基板は、例えばIV族半導体材料から成ることがあるのに対して、このナノ構造は、III−V族半導体材料から成ることもある。このナノ構造は、この基板によって支持され、この基板とエピタキシャルな関係にある。ナノ構造は、ゲートアラウンドトランジスタデバイスなどの電子デバイスの機能コンポーネントになる可能性がある。ゲートアラウンドトランジスタの一実施形態においては、ナノワイヤ(51)が、基板(50)によって支持され、この基板はドレインであり、このナノワイヤは電流チャネルであり、上部金属コンタクト(59)はソースである。薄いゲート絶縁膜(54)が、このナノワイヤとこのゲート電極(55A、55B)とを絶縁している。  (もっと読む)

(もっと読む)

半導体装置及び半導体装置の製造方法

ソース/ドレイン領域の少なくともその幅が最も大きい部分では半導体領域の幅よりも大きく、かつソース/ドレイン領域の最上部側から基体側に向かって連続的に幅が大きくなっている傾斜部を有し、該傾斜部表面にシリサイド膜が形成されていることを特徴とする半導体装置とする。  (もっと読む)

(もっと読む)

絶縁された金属領域を備えたフィールドプレートを有する横方向薄膜SOIデバイス

横方向薄膜シリコン−オン−インシュレータ(SOI)デバイスにおいて、フィールドプレートは、パッケージ及び表面電荷効果からデバイスを保護するために横方向ドリフト領域に亘って実質的に延在するように設けられている。特に、フィールドプレートは、シリコンドリフト領域にドーピング量勾配により形成される横方向電界分布を呈するように、スペーシングにより相互に横方向において絶縁される複数の金属領域からなる層を備えている。  (もっと読む)

(もっと読む)

電界効果型半導体装置における容量素子の動的制御

電界効果型装置はキャパシタのプレートをそれぞれ形成する複数のセグメントを有する少なくとも1つのセグメント化されたフィールド・プレートを含んでおり、選択されたセグメントを動的に接続してゲート−ドレイン間容量及びドレイン−ソース間容量を選択的に設定する電子素子に電界効果型装置が接続されている。トランスデューサを送信モードスイッチング装置と、受信モードスイッチング装置との間でスイッチングするスイッチング装置に結合されたトランスデューサを超音波装置が含んでおり、このスイッチング装置は電界効果型装置を含んでいる。  (もっと読む)

(もっと読む)

縦型ナノトランジスタおよび該トランジスタの製造方法ならびにメモリ装置

本発明の課題は、機械的応力に対し良好な耐性をもち、その製造が公知の従来技術よりも煩雑でない縦型ナノトランジスタを提供することである。本発明によればこの課題は、以下の特徴を備えた縦型ナノトランジスタによって解決される。すなわちソースコンタクトと、ドレインコンタクトと、ゲート領域と、ソースコンタクトとドレインコンタクトの間に配置され半導体特性をもつ円筒状のチャネル領域が設けられており、この円筒状チャネル領域は絶縁性フレキシブル基板に埋め込まれており、この領域は、ゲート領域とチャネル領域上部が同軸構造を成すよう、フレキシブル基板上およびチャネル領域上部の金属層により形成されたゲート領域により取り囲まれている。さらにソースコンタクトと半導体特性をもつチャネル領域とドレインコンタクトは縦方向に配置されていて、ソースコンタクトとドレインコンタクトと半導体特性をもつチャネル領域に対向するゲート領域と、基板の上側および下側は電気的に絶縁性の部材を有している。メモリ装置は多数のこの種の縦型ナノトランジスタから成る。本発明はこの種のトランジスタの製造方法にも関する。  (もっと読む)

(もっと読む)

線状素子

柔軟性、可撓性があり任意の形状に集積回路を作成できるという特徴を持つ線状MISFETでは、ソース領域とドレイン領域を並列配置する構造が使用されていた。しかし、MISFETの電気特性を決めるチャネル長が円筒形のゲート絶縁領域に沿ったソース領域とドレイン領域の距離できまるため、チャネル長の微細化や再現性向上が困難だった。 MISFETの構造を、ソース領域とドレイン領域でチャネル領域となる半導体領域を挟む構造とした。半導体領域にゲート絶縁領域を介して制御電圧を加え、ソース領域とドレイン領域間で流れる電流を制御する。チャネル長が、半導体領域の膜厚で決まるため、チャネル長の微細化や再現性向上が可能になった。 (もっと読む)

欠陥解析を実行するための方法及びそのシステム

回路欠陥解析及びプロセス問題識別を実行するための方法は、テスト信号を回路に印加するステップと、テスト信号に応答して生成された応答信号を得るステップと、応答信号を参照情報と比較するステップと、比較するステップの結果に基づいて回路内の欠陥を分類するステップと、欠陥分類に基づいて、欠陥を引き起こした製造プロセスにおける問題を識別するステップとを有している。参照情報は、製造プロセス中に発生する可能性がある予め定義されたタイプの欠陥に対応する1つ又は複数の信号プロフィルを含むことができる。欠陥の分類は、応答信号が、信号プロフィルのうちの1つ又は複数内に入るかどうか判定することによって実行されることが好ましい。応答信号が2つ以上の信号プロフィル内に入る場合には、各プロフィルについて確率を決定することができる。次いで、欠陥は、その信号プロフィルがより高い確率を有する欠陥タイプに対応するものとして分類することができる。処理システムは、同様の方法を使用して、欠陥の分類及びプロセス問題識別を実行する。 (もっと読む)

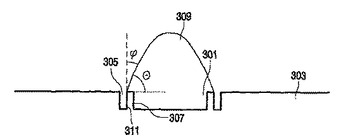

半導体構成用の構造およびその製造方法

本発明は、半導体構成用の構造に関する。半導体を含む溶液の堆積を補助するレジスト構造は、直接、あるいは介在層を介して基板に結合される。このレジスト構造は、半導体を含む溶液(309)を堆積するくぼみ(301)と、くぼみ(309)の縁部の少なくとも一部に整列し、突出部(307)によってくぼみ(309)から分離した溝(305)とを備える。好ましくは、溝(305)は、くぼみ(309)を取り囲む。この溝により、半導体を含む溶液を固定する作用が得られ、それによって濡れ性が改善し、それにしたがって、より大きな体積の半導体を所与の区域に付着させることができる。  (もっと読む)

(もっと読む)

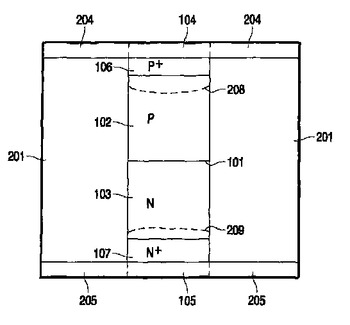

高絶縁破壊電圧を有する半導体装置

半導体装置、例えば、pn接合(101)を有するダイオード(200)がこのpn接合の近傍に、そして、これを跨ぐこともある絶縁材料の電界形成領域(201)を有する。電界形成領域(201)は好ましくは高誘電率を有し、容量性電圧結合領域(204,205)を介してpn接合に印加されるのとほぼ同じ電圧に結合される。pn接合(101)間に逆電圧が印加され且つ装置が非道通時に、電界形成領域(201)が存在しない場合に存在しうるpn接合空乏領域の限界を超えて延びる電界形成領域の一部分に容量性電界が存在し、電界形成領域内の電界が拡張された電界を誘起し、この拡張された電界は対応して拡張されたpn接合空乏領域(208,209)までとされ、装置の逆絶縁破壊電圧を増加させる。  (もっと読む)

(もっと読む)

配線構造、表示装置および能動素子基板

【課題】 パターニングフリーの能動素子基板の提供。

【解決手段】 能動素子基板は、基板上に形成された能動素子1と、能動素子1上に形成された導電膜2とを有する。導電膜2は、能動素子1から出力された電気信号を有限範囲内に伝達する。

(もっと読む)

MOS型センサおよびその駆動方法

【課題】 最適な蓄積時間を素早く見つける駆動方法を提供する。

【解決手段】 複数の画素を有するMOS型センサにおいて、複数の画素の全ての画素を同時にリセットした後、前記複数の画素から信号を順に出力し、前記リセットをした時から、前記複数の画素が、飽和した信号を出力する直前までの期間を、蓄積時間とすることを特徴とするMOS型センサの駆動方法が提供される。

(もっと読む)

1,141 - 1,159 / 1,159

[ Back to top ]