Fターム[5F110HM15]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−共通 (7,931) | 配置 (4,297) | ゲートに対する配置 (3,125) | オフセット (2,875) | LDD (2,472)

Fターム[5F110HM15]に分類される特許

161 - 180 / 2,472

半導体集積回路装置の製造方法

【課題】パターンの微細化、特に、SRAMのセル面積を縮小するためには、隣接ゲートの端部間距離を縮小することが重要となる。しかし、28nmテクノロジノードにおいては、ArFによる単一回露光でパターンを転写することは、一般に困難である。従って、通常、複数回の露光、エッチング等を繰り返すことによって、微細パターンを形成しているが、ゲートスタック材にHigh−k絶縁膜やメタル電極部材が使用されているため、酸化耐性やウエットエッチ耐性が低い等の問題がある。

【解決手段】本願発明は、メモリ領域におけるhigh−kゲート絶縁膜およびメタル電極膜を有するゲート積層膜のパターニングにおいて、最初に、第1のレジスト膜を用いて、隣接ゲート電極間切断領域のエッチングを実行し不要になった第1のレジスト膜を除去した後、第2のレジスト膜を用いて、ライン&スペースパターンのエッチングを実行するものである。

(もっと読む)

半導体装置の製造方法および電気光学装置の製造方法

【課題】特性の異なるTFTを同一基板上に形成する場合、フォトマスク数を増やすことで特性の異なるTFTを形成すると、TATが延び、価格も高騰するという課題があった。

【解決手段】1つのハーフトーンマスクを用いて、第2領域156とチャネル前駆体161aとソース・ドレイン前駆体165aとで膜厚の異なる段差レジストを形成する。NMOSTFTのチャネル前駆体161aには低加速エネルギーでは不純物が透過せず、高加速エネルギーでは不純物が通るレジスト膜厚の設定とし、ソース・ドレイン前駆体165aではレジストを開口させた。まず低加速エネルギーでソース・ドレイン前駆体165aにイオン注入し、次に、高加速エネルギーでチャネル前駆体161aにイオン注入する。第2領域156では2回の注入で、不純物が透過しないレジスト膜厚に設定する。

(もっと読む)

半導体装置

【課題】隣接する画素の間に設ける絶縁膜は、バンク、隔壁、障壁、土手などとも呼ばれ

、薄膜トランジスタのソース配線や、薄膜トランジスタのドレイン配線や、電源供給線の

上方に設けられる。特に、異なる層に設けられたこれらの配線の交差部は、他の箇所に比

べて大きな段差が形成される。隣接する画素の間に設ける絶縁膜を塗布法で形成した場合

においても、この段差の影響を受けて、部分的に薄くなる箇所が形成され、その箇所の耐

圧が低下されるという問題がある。

【解決手段】段差が大きい凸部近傍、特に配線交差部周辺にダミー部材を配置し、その上

に形成される絶縁膜の凹凸形状を緩和する。また、上方配線の端部と下方配線の端部とが

一致しないように、上方配線と下方配線の位置をずらして配置する。

(もっと読む)

半導体装置

【課題】大面積化しても低消費電力を実現した半導体装置の構造およびその作製方法を提供する。

【解決手段】画面で使われる画素の薄膜トランジスタを作製する。その薄膜トランジスタにおいて、ソース配線、ゲート電極を同一平面上に作製する。また、ソース配線と薄膜トランジスタをつなぐ配線と、画素電極と薄膜トランジスタをつなぐ配線を同一工程で作製する。

(もっと読む)

発光装置

【課題】駆動用トランジスタと、スイッチング用トランジスタを有する発光装置において、トランジスタのばらつきを低減する。

【解決手段】駆動用トランジスタと、スイッチング用トランジスタを有する発光装置において、駆動用トランジスタのチャネル幅をチャネル長よりも小さくする。その際、ゲート配線と平行にアノード側電源線を設けて、フルカラー表示を行う。

(もっと読む)

半導体記憶装置およびその作製方法

【課題】半導体記憶装置におけるデータ保持のためのリフレッシュ動作の回数を低減し、消費電力の小さい半導体記憶装置を提供する。また、三次元の形状を適用することで、集積度を高めても短チャネル効果の影響が低減され、かつ従来に比べてフォトリソグラフィ工程数の増加を抑えた半導体記憶装置を提供する。

【解決手段】溝部の設けられた絶縁膜103と、溝部を挟んで離間した一対の電極116と、溝部の側面および底面と接し、溝部の深さよりも厚さの薄い、一対の電極116と接する酸化物半導体膜106と、酸化物半導体膜106を覆うゲート絶縁膜112と、ゲート絶縁膜112を介して酸化物半導体膜106と重畳して設けられたゲート電極112と、を有するトランジスタ150と、キャパシタ160と、を有する半導体記憶装置である。

(もっと読む)

半導体装置の製造方法、半導体装置、電気光学装置および電子機器

【課題】チャネルドープを含む製造工程を簡略化できる半導体装置の製造方法、半導体装置、電気光学装置および電子機器を提供すること。

【解決手段】本適用例の半導体装置の製造方法は、基板に半導体膜としての多結晶半導体膜14aを形成する工程と、多結晶半導体膜14a上に、少なくとも2つの異なる膜厚を有し、それぞれが孤立したレジストパターン16,17を形成するレジスト形成工程と、該レジストパターン16,17をマスクとして多結晶半導体膜14aに第一不純物の注入を行う第一不純物注入工程と、該レジストパターン16,17に沿って多結晶半導体膜14aをエッチングするエッチング工程と、該レジストパターン16,17を剥離する工程とを有し、第一不純物注入工程は、レジストパターン16,17の膜厚の差に基づいて、第一不純物の注入、非注入を制御することを特徴とする。

(もっと読む)

電気光学装置の製造方法

【課題】新たなパラメーターによって半導体層内における不純物分布を制御して電界効果

型トランジスターを形成することのできる電気光学装置の製造方法を提供すること。

【解決手段】LDD構造の電界効果型トランジスターからなる画素トランジスターを基板

本体10wの一方面10sに形成するにあたって、一方面10s側の半導体層1aに不純

物を導入する不純物導入工程を行う。その後、不純物拡散工程において、一方面10s側

にレーザーアニール装置、ヒートガスアニール装置、ランプアニール装置等の加熱装置9

20を配置し、一方面10s側を他方面10t側より温度を高くした状態で半導体層1a

を加熱する。

(もっと読む)

半導体装置

【課題】小型化、薄型化、軽量化を実現した半導体装置の提供を課題とする。また、作製時間を短縮し、歩留まりを向上することができる半導体装置の作製方法の提供を課題とする。

【解決手段】トランジスタと、トランジスタ上に設けられた絶縁層と、絶縁層に設けられた開口部を介して、トランジスタのソース領域又はドレイン領域に電気的に接続された第1の導電層(ソース配線又はドレイン配線に相当)と、絶縁層及び第1の導電層上に設けられた第1の樹脂層と、第1の樹脂層に設けられた開口部を介して、第1の導電層に電気的に接続された導電性粒子を含む層と、第2の樹脂層及びアンテナとして機能する第2の導電層が設けられた基板とを有する。上記構成の半導体装置において、第2の導電層は、導電性粒子を含む層を介して、第1の導電層に電気的に接続されている。また、第2の樹脂層は、第1の樹脂層上に設けられている。

(もっと読む)

TiC膜を含む半導体構造を形成する方法

【課題】 TiC膜を含む半導体構造を形成する方法を提供する。

【解決手段】 高誘電率(k)の誘電体14および界面層12を含む積層体を基板10の表面上に設けるステップと、Heによって希釈された炭素(C)源およびArを含む雰囲気において、Tiターゲットをスパッタすることにより、前記積層体上にTiC膜16を形成するステップとを含む、半導体構造を形成する方法である。

(もっと読む)

液晶表示装置

【課題】動作性能および信頼性の高い液晶表示装置を提供する。

【解決手段】トランジスタ上に第1の絶縁膜を有し、第1の絶縁膜上に第1及び第2の配線を有し、第1及び第2の配線上に第2の絶縁膜を有し、第2の絶縁膜上に電極を有し、電極上に第3の絶縁膜を有し、第3の絶縁膜上に画素電極を有し、画素電極は、電極と重なる第1の領域と、電極と重ならない第2の領域と、を有し、画素電極は、第1の配線に電気的に接続されており、第1の配線は、トランジスタのソース又はドレインの一方と電気的に接続されており、電極は、画素部の外側において前記第2の配線と電気的に接続されている。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】トランジスタのチャネル部が形成される領域にU字状の縦長溝を形成し、見かけ上のチャネル長に対してチャネル長を長くする方法は、溝を掘るためにフォトリソグラフィ工程を余分に行う必要があり、コストや歩留まりの観点で問題があった。

【解決手段】ゲート電極または絶縁表面を有する構造物を利用し、三次元形状のチャネル領域を形成することにより、チャネル長が、上面から見たチャネル長に対して3倍以上、好ましくは5倍以上、さらに好ましくは10倍以上の長さとする。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】特性の良好な半導体装置を形成する。

【解決手段】薄膜領域TA1中に第1の素子領域、第2の素子領域および第1の分離領域を有し、厚膜領域TA2中に第3の素子領域、第4の素子領域および第2の分離領域を有する半導体装置を次のように製造する。(a)絶縁層1bを介してシリコン層1cが形成された基板を準備する工程と、(b)基板の第1の分離領域および第2の分離領域のシリコン層中に素子分離絶縁膜3を形成する工程と、を有するよう製造する。さらに、(c)薄膜領域TA1にハードマスクを形成する工程と、(d)ハードマスクから露出した、第3の素子領域および第4の素子領域のシリコン層上に、それぞれシリコン膜7を形成する工程と、(e)第3の素子領域および第4の素子領域のシリコン膜7間に、素子分離絶縁膜11を形成する工程と、を有するよう製造する。

(もっと読む)

発光装置の製造方法

【課題】発光装置を製造するときに生じ得る静電気に起因した素子の損傷を低減することのできる発光装置の製造方法について提供することを課題とする。また、静電気に起因した素子の損傷による不良が低減された発光装置を提供することを課題とする。

【解決手段】本発明の発光装置の製造方法は、発光素子を駆動するためのプレーナ型のトランジスタを作製する工程を有する。そして、トランジスタを作製する工程において、活性層として機能する半導体層を形成するときに、行方向及び列方向に延びた格子状の第1の半導体層を基板上に形成すると共に、前記第1の半導体層の間に、島状に分離した第2の半導体層を複数形成することを特徴としている。ここで、第2の半導体層は、トランジスタの活性層として機能する層である。

(もっと読む)

薄膜半導体装置

【課題】工程を複雑にすることなく、多結晶シリコン膜に回路特性に適した複数の異なる

ゲート絶縁膜厚を有する薄膜トランジスタ(TFT)を同一基板に形成することができる

薄膜半導体装置とその製造方法を提供。

【解決手段】ガラス基板上に形成した多結晶シリコン膜に駆動電圧が異なるTFTを混載

する際に、低電圧駆動TFTではチャネル領域の不純物をアクセプタがより多くなるよう

にしあるいはドナーがより少なくなるようにし、高電圧駆動TFTではチャネル領域の不

純物をドナーがより多くなるようにしあるいはアクセプタがより少なくなるようにする。

(もっと読む)

液晶表示装置、電子機器

【課題】IPSにおける従来の技術は、工程数が多く、開口率が低いので、実用化できな

い。また、液晶層に最も近接している層に存在する配線及び電極が多く、画素表示部にお

ける個々の液晶にかかる電界が不均一であった。

【解決手段】本発明は、ゲイト線102、105とコモン線103、104を最初に同時

に形成し、層間膜形成後、画素電極108とコモン電極110、111とソ─ス線106

、107を同時に形成する。こうすることによって、電極パタ─ンを単純化でき、工程を

簡略化した。また、液晶層に最も近接している層に存在する配線及び電極を画素電極とコ

モン電極とソ─ス線とし、その形状を単純なものにした。

(もっと読む)

EL表示装置

【課題】動作性能および信頼性の高いEL表示装置を提供する。

【解決手段】第1のチャネル形成領域と、第1のソース領域及び第1のドレイン領域と、ゲート絶縁膜と、第1のゲート電極とを備えた第1のTFTと、第2のチャネル形成領域と、第2のソース領域及び第2のドレイン領域と、ゲート絶縁膜と、第2のゲート電極とを備えた第2のTFTと、第1のTFT及び第2のTFT上に設けられた第1の絶縁膜と、第1のソース領域及び第1のドレイン領域の一方と接続されたソース配線と、第1のソース領域及び第1のドレイン領域の他方と接続し、且つ第2のゲート電極に接続された第1のドレイン配線と、第1の絶縁膜上に設けられ、第2のソース領域及び第2のドレイン領域の一方に接続された第2のドレイン配線と、第1の絶縁膜上に設けられ、第2のソース領域及び第2のドレイン領域の他方に接続された電流供給線と、を有する。

(もっと読む)

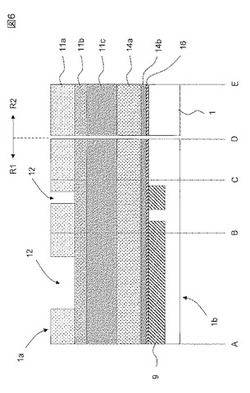

表示装置

【課題】被剥離層に損傷を与えない剥離方法を提供し、小さな面積を有する被剥離層の剥離だけでなく、大きな面積を有する被剥離層を全面に渡って歩留まりよく剥離することを可能とすることを目的としている。また、様々な基材に被剥離層を貼りつけ、軽量された半導体装置およびその作製方法を提供することを課題とする。特に、フレキシブルなフィルムにTFTを代表とする様々な素子を貼りつけ、軽量された半導体装置およびその作製方法を提供する。

【解決手段】基板上に第1の材料層11を設け、前記第1の材料層11に接して第2の材料層12を設け、さらに積層成膜または500℃以上の熱処理やレーザー光の照射処理を行っても、剥離前の第1の材料層が引張応力を有し、且つ第2の材料層が圧縮応力であれば、物理的手段で容易に第2の材料層12の層内または界面において、きれいに分離することができる。

(もっと読む)

半導体装置

【課題】オン抵抗が低く、かつ、容易に素子分離もできる半導体装置を提供する。

【解決手段】第1絶縁膜2の上の第1導電型の第1半導体層3の表面を含む上部に設けられた第2導電型の第1半導体領域7と、第1半導体領域7の上部に設けられた第1導電型の第2半導体領域8と、側面が第1半導体層3と第1半導体領域7と第2半導体領域8に接する第1トレンチ4と、第1トレンチ4の側面に沿って設けられたゲート絶縁膜5と、第1トレンチ4内に埋め込まれたゲート電極6と、第1半導体領域7と第1トレンチ4から離れて第1半導体層3の上部に設けられた第1導電型の第3半導体領域9と、側面が第3半導体領域9に接し第3半導体領域9に対して第1半導体領域7の反対側に配置された第2トレンチ15と、第2トレンチ15の側面に沿って設けられた素子分離絶縁膜10と、第2トレンチ15内に埋め込まれたポリシリコン埋め込み領域11とを有する。

(もっと読む)

EL表示装置

【課題】開口率の高い表示装置又は素子の面積の大きい半導体装置を提供することを課題

とする。

【解決手段】隣接する画素電極(又は素子の電極)の間に設けられた配線との下方にマル

チゲート構造のTFTのチャネル形成領域を設ける。そして、複数のチャネル形成領域の

チャネル幅の方向を前記画素電極の形状における長尺方向と平行な方向とする。また、チ

ャネル幅の長さをチャネル長の長さよりも長くすることでチャネル形成領域の面積を大き

くする。

(もっと読む)

161 - 180 / 2,472

[ Back to top ]