Fターム[5F110NN02]の内容

薄膜トランジスタ (412,022) | その他の構成要素 (47,691) | 保護膜(パッシベーション膜) (34,477) | 層間絶縁膜 (8,935)

Fターム[5F110NN02]の下位に属するFターム

Fターム[5F110NN02]に分類される特許

401 - 420 / 3,265

有機薄膜トランジスタの製造方法及び該方法で製造された有機薄膜トランジスタ

【課題】大面積の素子の製造が容易であり、ソース電極及びドレイン電極を形成する際にゲート絶縁層を損傷せず、有機絶縁材料が有する柔軟性を損なわない、有機薄膜トランジスタの製造方法を提供すること。

【解決手段】ゲート電極、及び該ゲート電極を被覆し、有機絶縁材料を含むゲート絶縁層を形成する工程;該ゲート絶縁層上に塗布法、無電解めっき法又は原子層堆積法を用いて導電性材料からなる第1導電層を成膜する工程;該第1導電層上にパターンニングされた第2導電層を形成する工程;該第2導電層で被覆されていない第1導電層の部分を除去して、第1導電層及び第2導電層からなるソース電極及びドレイン電極を形成する工程;及びソース電極、ドレイン電極、及び該ソース電極と該ドレイン電極に挟まれた領域のゲート絶縁層が被覆されるように、有機半導体層を形成する工程;を有する、有機薄膜トランジスタの製造方法。

(もっと読む)

半導体装置の作製方法

【課題】半導体層となる部分が水分などに曝されず、マスク枚数を削減する半導体装置の作製方法を提供する。

【解決手段】例えば、第1の導電膜、第1の絶縁膜、半導体膜、第2の導電膜及びマスク膜を形成し、マスク膜を加工して第1のマスク層を形成し、第1のマスク層を用いて第1の絶縁膜、半導体膜及び第2の導電膜にドライエッチングを行って薄膜積層体を形成しつつ、第1の導電膜の少なくとも表面を露出させ、薄膜積層体の側面を覆うサイドウォール絶縁層を形成し、第1の導電膜をサイドエッチングして第1の電極層を形成し、第2のマスク層を形成し、第2のマスク層を用いて第2の電極層を形成する。第1のマスク層及び第2のマスク層の形成はレジストマスクを用いて行う。

(もっと読む)

アレイ基板及び液晶ディスプレイ

【課題】本発明はアレイ基板及び液晶ディスプレイに関する。

【解決手段】本発明は、アレイ基板と液晶ディスプレイを開示している。このアレイ基板は、サブストレートと、前記サブストレートに形成された、横縦方向に交差して複数の画素ユニットを囲んで形成したデータライン及びゲートラインと、を備え、各画素ユニットは画素電極と薄膜トランジスタースイッチ素子とを備え、前記薄膜トランジスタースイッチ素子は、ゲート電極、ソース電極、ドレイン電極、活性層を備え、前記ゲート電極と活性層との間にゲート絶縁層が設けられ、前記ゲート絶縁層は不透明絶縁層を含む。

(もっと読む)

電気光学装置、投射型表示装置、電気光学装置の製造方法

【課題】画素電極表面でのヒロックの発生や、平坦化絶縁膜において凹部を埋める部分での空洞の発生を防止することのできる電気光学装置、該電気光学装置を用いた投射型表示装置、および当該電気光学装置の製造方法を提供すること。

【課題手段】電気光学装置100の素子基板10において、反射性の画素電極9aの上層側に設けられた平坦化絶縁膜17は、画素電極9a上に積層された層がドープトシリコン酸化膜170からなる。ドープトシリコン酸化膜170の熱膨張係数は、画素電極9aを構成するアルミニウム膜の熱膨張係数との差が小さい。このため、加熱した状態で平坦化絶縁膜17を成膜しても、画素電極9aおよび平坦化絶縁膜17に大きな熱応力が発生しないので、画素電極9aの表面にヒロック等の欠陥が発生しにくい。また、ドープトシリコン酸化膜170は、段差被覆性に優れている。

(もっと読む)

半導体装置

【課題】本願発明で開示する発明は、従来と比較して、さらに結晶成長に要する熱処理時間を短縮してプロセス簡略化を図る。

【解決手段】

一つの活性層204を挟んで二つの触媒元素導入領域201、202を配置して結晶化を行い、触媒元素導入領域201からの結晶成長と、触媒元素導入領域202からの結晶成長とがぶつかる境界部205をソース領域またはドレイン領域となる領域204bに形成する。

(もっと読む)

薄膜トランジスタ回路基板及びその製造方法

【課題】製造コストの削減が可能であるとともに、安定したトランジスタ特性を得ることが可能な薄膜トランジスタ回路基板及びその製造方法を提供する。

【解決手段】絶縁基板上に酸化物半導体薄膜を形成し、前記酸化物半導体薄膜の上にゲート絶縁層を形成し、前記ゲート絶縁層の上にゲート層を形成し、前記ゲート層の上にレジストパターンを形成し、前記レジストパターンをマスクとして、前記ゲート絶縁層及び前記ゲート層を一括してパターニングして、ゲート絶縁膜上にゲート電極を形成するとともに、ソース領域及びドレイン領域となる前記酸化物半導体薄膜を露出させ、露出させた前記酸化物半導体薄膜を、少なくともシラン(SiH4)を含むガスに晒し、前記シランを含むガスに晒した後に連続して層間絶縁膜を形成する、ことを特徴とする薄膜トランジスタ回路基板の製造方法。

(もっと読む)

液晶パネル、TFTアレイ基板及びその製造方法

【課題】液晶パネル、TFTアレイ基板及びその製造方法を提供する。

【解決手段】本発明は、液晶パネル、TFTアレイ基板及びその製造方法に関する。ベース基板と、前記ベース基板上に形成されたゲート走査線と、データ走査線と、前記ゲート走査線および前記データ走査線を上から覆う保護層とを備えるTFTアレイ基板であって、前記保護層における封止剤を塗布した領域の、ゲート走査線と/またはデータ走査線に対応する位置に、導電層が設けられる。前記導電層は、当該TFTアレイ基板における封止剤の外部領域に延びるとともに、接地端に接続される。前記導電層を形成する材料としては、透明導電材料を有する。

(もっと読む)

薄膜トランジスタアレイ基板、及び液晶表示装置

【課題】透明導電膜上層に形成される絶縁膜の膜浮きの発生を防止或いは抑制し、歩留り或いは信頼性を向上することの可能な薄膜トランジスタアレイ基板、及び液晶表示装置を得る。

【解決手段】この発明のTFTアレイ基板100においては、TFT51と、ソース電極53及びドレイン電極54、並びにソース電極53及びドレイン電極54と同一材料により同層に形成される金属パターン5の何れかに直接重なり形成される透明導電膜パターン6と、透明導電膜パターン6上を含むゲート絶縁膜8上を覆う上層絶縁膜9を備え、少なくとも額縁領域42に形成される透明導電膜パターン6は、ソース電極53、ドレイン電極54或いは金属パターン5のパターン端面を覆うことなく形成される。

(もっと読む)

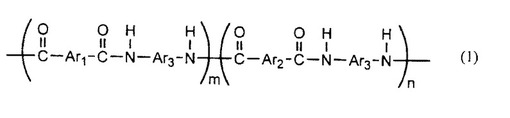

フェノール性水酸基含有芳香族ポリアミド樹脂を含有する絶縁層を有する有機半導体素子並びにその製造方法

【課題】本発明のフェノール性水酸基含有芳香族ポリアミド樹脂を含有する有機絶縁層を用いた有機半導体素子は、トランジスタ特性及び耐湿熱性等の耐久性に優れており、実用性の高い有機半導体素子を提供する。

【解決手段】下記式(1)で表されるフェノール性水酸基含有芳香族ポリアミド樹脂を含有する有機絶縁層を有する有機半導体素子。

(式(1)中、各構造単位の平均重合度m及びnはm+n=2〜200であり、Ar1及びAr3は2価の芳香族基、Ar2はフェノール性水酸基を有する2価の芳香族基を表す。)

(もっと読む)

整流回路及びこれを用いた半導体装置

【課題】整流素子として用いるトランジスタの閾値電圧による出力電圧の降下が抑制された整流回路を提供する。または、入力される交流電圧の振幅が大きく変動する場合であっても、出力電圧の変動が抑制された整流回路を提供する。

【解決手段】トランジスタのゲート電極を、容量素子を介して該トランジスタの第2の電極の後段に接続し、ゲート電極の電位を第2の電極の電位に比べて高く、且つその差が閾値電圧以上となるように保って整流素子として用いればよい。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】 水分に起因するTFT特性の変化を抑制した薄膜トランジスタおよびその製造方法を提供する。

【解決手段】 本発明の薄膜トランジスタは、基板上に、少なくともゲート電極、ゲート絶縁膜、活性層、ソース電極、およびドレイン電極が設けられ、活性層上にソース電極およびドレイン電極が設けられたものである。活性層は、アモルファス酸化物半導体により構成されており、ゲート絶縁膜内に存在する第1の水分量が活性層に存在する第2の水分量よりも少ない。

(もっと読む)

ディスプレイ装置及びその製造方法

【課題】構造及び製造工程を簡素化しながら、開口率を向上させた、ディスプレイ装置及びその製造方法を提供する。

【解決手段】本発明の実施形態に係るディスプレイ装置101は、基板111、前記基板111上に形成された前記第1透明導電膜1301及び前記第1透明導電膜1301上に形成された第1金属膜1302を含む多重膜構造と前記第1透明導電膜1301で形成された単一膜構造とを含むゲート配線、前記ゲート配線の一部の領域上に形成された半導体層153、そして前記半導体層上に形成された第2透明導電膜1701及び前記第2透明導電膜1701上に形成された第2金属膜1702を含む多重膜構造と前記第2透明導電膜1701で形成された単一膜構造とを含むデータ配線を含む。

(もっと読む)

配線構造

【課題】有機ELディスプレイや液晶ディスプレイなどの表示装置において、酸化物半導体層と、例えばソース電極やドレイン電極を構成する金属膜との安定した界面の形成が可能である配線構造を提供する。

【解決手段】基板の上に、基板側から順に、薄膜トランジスタの半導体層と、金属配線膜とを有しており、半導体層と金属配線膜との間にバリア層を有する配線構造であって、半導体層は酸化物半導体からなり、バリア層はTi酸化膜から構成されており、且つ、Ti酸化膜は半導体層と直接接続している。

(もっと読む)

半導体装置の製造方法

【課題】 半導体装置に於けるLDD構造とGOLD構造の形成は、従来、ゲート電極をマスクにセルフアラインで形成しているが、ゲート電極が2層構造となる場合が多く、成膜工程とエッチング工程が複雑になる。またドライエッチング等のプロセスのみでLDD構造及びGOLD構造の形成を行っている為、トランジスタ構造が全て同一構造となり、回路毎にLDD構造とGOLD構造及びシングルドレイン構造を別々に形成することが困難である。

【解決手段】 回折格子パターン或いは半透膜から成る光強度低減機能を有する補助パターンを設置したフォトマスク或いはレチクルをゲート電極形成用フォトリソグラフィ工程に適用することにより、ドライエッチング及びイオン注入工程を通し、回路毎にGOLD構造及びLDD構造及びシングルドレイン構造のトランジスタを簡単に形成することができることを特徴としている。

(もっと読む)

薄膜トランジスタ基板およびそれの製造方法

【課題】薄膜トランジスタ基板およびこれの製造方法を開示する。

【解決手段】本発明の薄膜トランジスタ基板は、基板上に形成されたゲート電極、前記ゲート電極上に前記ゲート電極と重なるように形成され、多結晶シリコンを含むアクティブ層、前記アクティブ層上に前記ゲート電極を中心に両側に分離して形成された第1オーミックコンタクト層、前記第1オーミックコンタクト層上に形成された第2オーミックコンタクト層および前記第2オーミックコンタクト層上に形成されたソース電極およびドレーン電極を含む。

(もっと読む)

埋め込みゲートを有する半導体装置及びその製造方法

【課題】埋め込みゲートトランジスタのSCEに対する免疫性を向上させると同時に、分岐点での重なりを増加させる方法及び構造の提供。

【解決手段】基板102は第1活性領域104と第2活性領域106とを有し、浅溝分離(STI)領域108によって分離される。バッファ層112は応力緩和層として機能しハードマスク層114が形成される。基板102の表面に分離領域108を部分的に網羅するように凹部118を設ける。ゲート誘電体120が凹部118に形成された後第一ドーパントインプラント122により、ドープ済みチャンネル領域124が形成される。インプラントはハードマスク114を貫通しないので、凹部118の下に形成されたドープ済みチャンネル領域124中のドーパント濃度は最も高くなる。ドープ済みチャンネル領域124はトランジスタのオン・オフを切り替える閾値電圧を変調する。

(もっと読む)

半導体装置の作製方法

【課題】マスク数が少なく、工程が簡略な半導体装置の作製方法を提供する。

【解決手段】ゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜と、半導体膜と、不純物半導体膜と、導電膜と、をこの順に積層して形成し、導電膜を加工してソース電極及びドレイン電極を形成し、不純物半導体膜を離間させつつ半導体膜の上部を加工してソース領域及びドレイン領域と、ソース領域及びドレイン領域と重畳しない部分の上部が除去された半導体層と、を形成し、ゲート絶縁膜、半導体層、ソース領域及びドレイン領域、ソース電極及びドレイン電極上にパッシベーション膜を形成し、パッシベーション膜上にエッチングマスクを形成し、エッチングマスクにより、ソース電極またはドレイン電極に達する開口部を形成しつつ、少なくともパッシベーション膜と半導体層を島状に加工し、エッチングマスクを除去し、ゲート絶縁膜及びパッシベーション膜上に画素電極を形成する。

(もっと読む)

発光装置

【課題】開口部をシンプルにしてシュリンクの問題を解決する。

【解決手段】駆動トランジスタと、スイッチングトランジスタと、消去用トランジスタと

、を画素内に有する3トランジスタ型の発光装置の場合において、スイッチング用TFT

5505と消去用TFT5506の2つのTFTを、第1のゲート信号線5502と第2

のゲート信号線5503の間に配置する。このように配置することで開口率を上げ、開口

部もシンプルな形状にすることが出来る。

(もっと読む)

液晶表示装置及び液晶表示装置の作製方法

【課題】薄く、軽量であり且つ破壊が生じにくい液晶表示装置を、作製工程を大幅に削減して低コストで作製する方法を提供する。

【解決手段】剥離層を介して基板上に素子領域を形成する際に、半導体層のエッチングと、画素電極とドレイン電極を接続するためのコンタクトホールの形成を、同一のフォトリソグラフィ工程及びエッチング工程で行う。更に素子領域を基板から剥離してじん性の高い第1の支持体に移し替え、第1の支持体及びじん性の高い第2の支持体で液晶素子を挟持することで、薄く、軽量であり且つ破壊が生じにくい液晶表示装置を、作製工程を大幅に削減して低コストで作製できる。

(もっと読む)

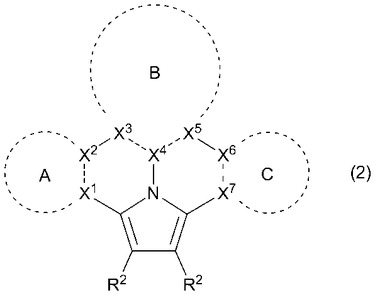

縮合芳香族化合物、有機半導体材料及び有機トランジスタ

【課題】再配向エネルギーが十分に小さい有機化合物の提供。

【解決手段】式

[式中、A環、B環及びC環は、各々独立して、芳香環を表す。X1、X2、X3、X4、X5、X6及びX7は、各々独立して、炭素原子又は窒素原子を表す。]で表される縮合芳香族化合物、又は式(2)で表される縮合芳香族化合物から水素原子を2個除いた2価の基を繰り返し単位として有する高分子化合物。

(もっと読む)

401 - 420 / 3,265

[ Back to top ]