Fターム[5F110NN02]の内容

薄膜トランジスタ (412,022) | その他の構成要素 (47,691) | 保護膜(パッシベーション膜) (34,477) | 層間絶縁膜 (8,935)

Fターム[5F110NN02]の下位に属するFターム

Fターム[5F110NN02]に分類される特許

361 - 380 / 3,265

エッチング方法及び薄膜トランジスタの作製方法

【課題】アモルファスシリコン膜と微結晶シリコン膜とのエッチングレートの差を大きくしたエッチング方法を提供する。

【解決手段】絶縁膜上に微結晶シリコン膜を形成し、前記微結晶シリコン膜上にアモルファスシリコン膜を形成し、前記アモルファスシリコン膜に1000Paより高圧力のH2とArの混合ガス雰囲気中でプラズマ処理を行うことにより前記微結晶シリコン膜を露出させてエッチングを行う。該エッチングは、アモルファスシリコン膜と微結晶シリコン膜とのエッチングレートの差が大きい。

(もっと読む)

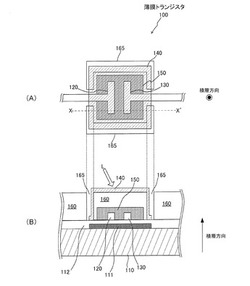

薄膜トランジスタ及び薄膜トランジスタの製造方法

【課題】

製造プロセスのステップ数を少なくでき、素子の構造が簡単でコストを抑制することが可能な薄膜トランジスタを提供する。

【解決手段】本発明の薄膜トランジスタ100は、主面を有する基材110と、前記基材110の前記主面に対する積層方向に配設される遮光層111と、前記積層方向からみて、前記遮光層111に含まれるように設けられる有機半導体層150と、前記有機半導体層150と接触するように設けられ、互いに対向しチャネル領域を形成するソース電極120及びドレイン電極130と、前記積層方向からみて、前記有機半導体層150の外周において前記ソース電極120と前記ドレイン電極130と重畳しない溝部165が設けられたゲート絶縁層160と、前記積層方向からみて前記有機半導体層150を含むように、前記ゲート絶縁層160上及び前記溝部165に設けられるゲート電極140と、からなることを特徴とする。

(もっと読む)

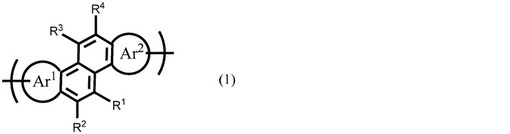

高分子化合物、これを含む薄膜及びインク組成物

【課題】高い電荷の移動度が得られる高分子化合物を提供すること。

【解決手段】式(1)で表される繰り返し単位を有する高分子化合物。

[Ar1及びAr2は、芳香族炭化水素環、複素環、又は芳香族炭化水素環と複素環との縮合環である。R1、R2、R3及びR4は、水素原子、アルキル基、アルコキシ基、アルキルチオ基、アリール基、アリールオキシ基、アリールチオ基、アリールアルキル基、アリールアルコキシ基、アリールアルキルチオ基、置換シリル基、非置換若しくは置換のカルボキシル基、1価の複素環基、シアノ基又はフッ素原子を示す。]

(もっと読む)

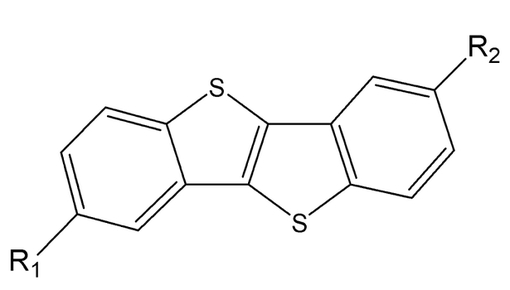

低分子半導体

【課題】高い移動度および良好な膜形成性を示す半導体化合物を提供する。

【解決手段】下式の低分子半導体。

〔R1、R2は、アルケニル、アルキニル、アリール、アルコキシ、アルキルチオ等〕

(もっと読む)

半導体装置およびその作製方法

【課題】スパッタ法でトランジスタ、ダイオード等の半導体用途に好適な材料を提供する。具体的には結晶性の高い酸化物半導体膜を形成する作製プロセスを提供する。

【解決手段】意図的に窒素を酸化物半導体に対して添加することにより、六方晶であり、ウルツ鉱型結晶構造を有する酸化物半導体膜を形成する。酸化物半導体膜において、窒素を含む領域の結晶性は、窒素をあまり含まない領域、或いは窒素を意図的に添加していない領域に比べて高くなる。この結晶性の高いウルツ鉱型結晶構造を有する酸化物半導体膜をトランジスタのチャネル形成領域として用いる。

(もっと読む)

酸化物半導体膜および半導体装置

【課題】より電気伝導度の安定した酸化物半導体膜を提供することを課題の一とする。また、当該酸化物半導体膜を用いることにより、半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を提供することを課題の一とする。

【解決手段】結晶性を有する領域を含み、当該結晶性を有する領域は、a−b面が膜表面に概略平行であり、c軸が膜表面に概略垂直である結晶よりなる酸化物半導体膜は、電気伝導度が安定しており、可視光や紫外光などの照射に対してもより電気的に安定な構造を有する。このような酸化物半導体膜をトランジスタに用いることによって、安定した電気的特性を有する、信頼性の高い半導体装置を提供することができる。

(もっと読む)

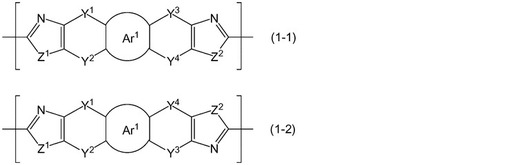

含窒素縮合環化合物、含窒素縮合環重合体、有機薄膜及び有機薄膜素子

【課題】優れた電子輸送性を有する有機n型半導体として利用可能な新規化合物及び新規重合体の提供。

【解決手段】式(1−1)及び式(1−2)で表される構造単位からなる群より選択される、含窒素縮合環化合物。

[式中、Ar1は、芳香環を示し、Y1及びY2のうちいずれか一方は、−C(=X1)−で表される基を示し、他方は、単結合を示し、Y3及びY4のうちいずれか一方は、−C(=X2)−で表される基を示し、他方は、単結合を示し、X1及びX2は、酸素原子等を示し、Z1及びZ2は、酸素原子等を示す。]

(もっと読む)

電界効果型トランジスタ及びその製造方法

【課題】半導体特性に影響を与えることなく、印刷法により形成される半導体の形状再現性に優れた電界効果型トランジスタの製造方法を提供すること。

【解決手段】基材上に、少なくともゲート電極、ソース電極、ドレイン電極と、半導体層およびゲート絶縁膜とが形成されてなる電界効果型トランジスタの製造方法であって、少なくともゲート絶縁膜上に半導体層を形成する工程を有し、該ゲート絶縁膜は露光によりシランカップリング剤と反応可能な官能基を生成し得る材料で形成されており、該工程の前に、ゲート絶縁膜上の半導体を形成する領域の周囲を露光する工程及び露光部においてフッ化アルキル基を有するシランカップリング剤と該官能基とを反応させる工程を有することを特徴とする。

(もっと読む)

半導体集積回路装置

【課題】I/O用バルク部とコアロジック用SOI部が混載されたバルク&SOIハイブリッド型CMISデバイスでは、閾値電圧制御の最適化のため多数のゲートスタックを用いる必要があり、プロセス及び構造が複雑になるという問題がある。

【解決手段】本願発明は、High−kゲート絶縁膜およびメタルゲート電極を有するSOI型半導体CMISFET集積回路装置において、いずれかのバックゲート半導体領域に不純物を導入することにより、対応する部分のMISFETの閾値電圧を調整するものである。

(もっと読む)

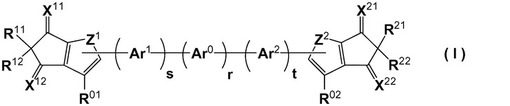

共役系化合物、並びにこれを用いた有機薄膜及び有機薄膜素子

【課題】電子輸送性に優れたn型半導体として利用可能であり、しかも溶剤への溶解性にも優れる共役系化合物の提供。

【解決手段】式(I)で表される共役系化合物。[式中、R01及びR02はアルカン骨格を含む1価の基。R11、R12、R21及びR22は水素原子、ハロゲン原子又は1価の基。X11、X12、X21及びX22は=O,=S又は=CA2(Aは水素原子、ハロゲン原子又は1価の基を示すが、その少なくとも1つは電子吸引性の基。)を示す。Z1及びZ2は−O−,−S−,−Se−,−Te−,−SO−等のいずれかの基を示す。Ar0、Ar1及びAr2は芳香族炭化水素基又は複素環基を示す。rは1〜6の整数、s及びtは0〜6の整数を示す。] (もっと読む)

(もっと読む)

半導体記憶装置

【課題】単位面積あたりのメモリモジュールの記憶容量を増加させる。また、消費電力の小さなメモリモジュールを提供する。

【解決手段】DRAMに、高純度化された、バンドギャップが2.5eV以上の酸化物半導体膜、炭化シリコン膜および窒化ガリウム膜などでなるトランジスタを用いることで、キャパシタの電位の保持期間が延びる。また、メモリセルが容量の異なるn個のキャパシタを有し、n個のキャパシタとそれぞれ異なるn本のデータ線を接続することによって保持容量を様々にとることができる。

(もっと読む)

表示素子の製造方法

【課題】安定した電流駆動能力を発揮させる。

【解決手段】アレイ基板20の製造方法は、基板上にゲート電極24aを形成するゲート電極形成工程と、ゲート電極24a上に不純物を含有するゲート絶縁膜24b、半導体膜SM、導電膜COの順で成膜する成膜工程と、導電膜CO上にレジストRSを塗布し、そのレジストRSに対してフォトマスクを介して露光を行った後に現像を行うことでレジストRSをパターニングするレジストパターニング工程と、パターニングされたレジストRSをマスクとして導電膜COをエッチングすることで開口領域OPを挟んで配されるソース電極24d及びドレイン電極24eを形成する導電膜パターニング工程と、開口領域OPから半導体膜SMを介してゲート絶縁膜24bに含有される不純物を脱離させる不純物脱離工程とを含む。

(もっと読む)

半導体集積回路装置

【課題】I/O用バルク部とコアロジック用SOI部が混載されたバルク&SOIハイブリッド型CMISデバイスでは、閾値電圧制御の最適化のため多数のゲートスタックを用いる必要があり、プロセス及び構造が複雑になるという問題がある。

【解決手段】本願発明は、High−kゲート絶縁膜およびメタルゲート電極を有するSOI型半導体CMISFET集積回路装置において、いずれかのバックゲート半導体領域に不純物を導入することにより、対応する部分のMISFETの閾値電圧を調整するものである。

(もっと読む)

半導体装置の製造方法

【課題】MOSトランジスタの形成工程を利用して、トレンチアイソレーションを形成できるようにした半導体装置の製造方法を提供する。

【解決手段】シリコン基板1にDTI層20とMOSトランジスタとを有する半導体装置の製造方法であって、シリコン基板1に深いトレンチを形成し、トレンチが形成されたシリコン基板1に熱酸化を施して、PMOSトランジスタ50のゲート酸化膜13を形成すると同時に、トレンチの内側面にSiO2膜14を形成する。次に、トレンチを埋め込むようにシリコン基板1上にポリシリコン膜15を堆積し、このポリシリコン膜15をパターニングする。これにより、PMOSトランジスタ50のゲート電極17を形成すると同時に、トレンチ内にSiO2膜14とポリシリコン膜18とを含むDTI層20を形成する。

(もっと読む)

酸化物絶縁膜、酸化物半導体薄膜トランジスタ素子およびその製造方法

【課題】2桁以上高い固有抵抗値を持った酸化物絶縁膜を提供でき、適量の酸素原子を含有した酸化物半導体材料を半導体層に、酸素原子に加えて適量の炭素原子を含有した酸化物絶縁層材料をゲート絶縁層、チャンネル保護層、パッシベーション層に使った酸化物半導体薄膜トランジスタ素子およびその製造方法を得る。

【解決手段】酸化物半導体層中に、酸素原子に加えて、炭素原子を添加して酸化物絶縁膜を形成する。また、本発明に係る酸化物半導体薄膜トランジスタ素子は、酸化物材料がチャンネル半導体層に使われる酸化物半導体薄膜トランジスタ素子であって、前記酸化物絶縁膜は、前記チャンネル半導体層に使われる酸化物材料と同一材料でなり、ゲート絶縁層、チャンネル保護層、パッシベーション層のいずれかまたはすべてに用いる。

(もっと読む)

導電膜用エッチング液組成物

【課題】基板上に形成されたモリブデン系導電性薄膜、または、モリブデン系導電性薄膜とアルミニウム系導電性薄膜とが積層された積層導電性薄膜を、効率よく、側面が良好な順テーパー形状となるようなエッチングを行うことが可能なエッチング液、および、該エッチング液を用いたエッチング方法を提供することを目的とする。

【解決手段】(a)リン酸30〜80重量%と、(b)硝酸0.1〜20重量%と、(c)有機酸塩0.1〜20重量%と、(d)水とを含有するエッチング液を用いてエッチングを行う。

また、上記エッチング液を用いて、アルミニウム系導電性薄膜と、モリブデン系導電性薄膜とを備えてなる2層構造の積層導電性薄膜、または、アルミニウム系導電性薄膜と、アルミニウム系導電性薄膜を挟み込むようにその両主面側に配設された第1のモリブデン系導電性薄膜および第2のモリブデン系導電性薄膜を備えてなる3層構造の積層導電性薄膜をエッチングする。

(もっと読む)

半導体装置及び電子機器

【課題】半導体装置の作製工程におけるプラズマダメージの影響を低減し、しきい値電圧

のばらつきの抑制された均一な表示特性の半導体装置を提供する。

【解決手段】トランジスタ上の平坦化層と、該平坦化層の上面もしくは下面に設けられる

と共に前記平坦化層からの水分や脱ガス成分の拡散を抑制するバリア層を備えた半導体装

置であって、これら平坦化層及びバリア層の位置関係を工夫することにより平坦化層に及

ぶプラズマダメージを低減する上で有効なデバイス構成を用いる。また、画素電極の構造

として新規な構造との組み合わせにより、輝度の向上等の効果をも付与する。

(もっと読む)

半導体装置

【課題】従来に比してオン電圧性能に優れた横型IGBT、および順方向電圧特性に優れた横型FWDを同一基板上に構成可能とする半導体装置を提供する。

【解決手段】半導体基板上において、横型IGBTと、横型FWDとが、絶縁体であるトレンチ絶縁仕切り部を挟むように横方向に隣接配置されて成る半導体装置であって、横型IGBTは、平面視した場合に、エミッタ領域と当該横型IGBTのドリフト領域との境界面の幅がコレクタ領域と当該横型IGBTのドリフト領域との境界面の幅より狭くなるよう形成されており、横型FWDは、平面視した場合に、カソード領域と当該横型FWDのドリフト領域との境界面の幅がアノード領域と当該横型FWDのドリフト領域との境界面の幅より狭くなるよう形成されていることを特徴とする、半導体装置。

(もっと読む)

薄膜トランジスタ、アクティブマトリクス基板、およびそれらの製造方法

【課題】高い表示品質を実現することができるTFT、アクティブマトリクス基板及びそれらの製造方法を提供すること。

【解決手段】本発明にかかる薄膜トランジスタは、ゲート電極2aと、ゲート電極2aを覆うように設けられたゲート絶縁膜3と、ゲート絶縁膜3の上に設けられ、ゲート電極の上方に配置された半導体膜5と、半導体膜5の上に設けられ、半導体膜5と電気的に接続されたソース電極7と、半導体膜5の上に設けられ、半導体膜5と電気的に接続されたドレイン電極9と、ソース電極7又はドレイン電極9の少なくとも一方とゲート絶縁膜3との間に設けられ、半導体膜5と分離して配置された低反射膜6と、を備え、低反射膜6が、平面視におけるゲート電極2aの外側において、ソース電極7、ドレイン電極9のパターンと略同一形状、又は、はみ出しているものである。

(もっと読む)

薄膜トランジスタ表示板の製造方法

【課題】半導体層の側壁がデータ線の側壁に対して突出することを最小化する。

【解決手段】ゲート絶縁膜140上に第1、第2非晶質シリコン層150,160、データ金属層170形成段階と、上部データ金属層170r上に第1感光膜パターン50形成段階と、第1感光膜パターンをマスクとしてデータ金属層170をエッチングして、第1下部データ金属パターン及び側壁が突出した突出部を含む第1上部データ金属パターン形成段階と、第1感光膜パターンをマスクとして第1及び第2非晶質シリコン層をエッチングして、非晶質シリコン層パターン形成段階と、第2感光膜パターンをマスクとして第1上部データ金属パターンをエッチングして、第2上部データ金属パターン形成段階と、第2感光膜パターンをマスクとして第1下部データ金属パターン、非晶質シリコン層パターンをエッチングして、半導体、データ線等を形成する段階、とを含む。

(もっと読む)

361 - 380 / 3,265

[ Back to top ]