Fターム[5F110NN02]の内容

薄膜トランジスタ (412,022) | その他の構成要素 (47,691) | 保護膜(パッシベーション膜) (34,477) | 層間絶縁膜 (8,935)

Fターム[5F110NN02]の下位に属するFターム

Fターム[5F110NN02]に分類される特許

281 - 300 / 3,265

半導体装置

【課題】薄膜トランジスタの寄生容量を低減することが可能な半導体装置を提供する。

【解決手段】 絶縁基板と、前記絶縁基板上に形成されたゲート電極と、前記ゲート電極を覆う第1絶縁膜と、前記第1絶縁膜上に形成され、前記ゲート電極の直上に位置する第1領域と、前記第1領域を挟んだ両側に位置する第2領域及び第3領域と、前記第2領域に積層されるとともに前記第2領域よりも低抵抗な第4領域と、前記第3領域に積層されるとともに前記第3領域よりも低抵抗な第5領域と、を有する酸化物半導体層と、前記酸化物半導体層の前記第1領域を覆うとともに、前記第4領域の一部及び前記第5領域の一部をそれぞれ露出する第2絶縁膜と、前記第2絶縁膜から露出した前記第4領域に電気的に接続されたソース電極と、前記第2絶縁膜から露出した前記第5領域に電気的に接続されたドレイン電極と、を備えたことを特徴とする半導体装置。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置の小型化を実現する。

【解決手段】 第1の絶縁膜上に、島状の半導体層及び前記半導体層を囲む第2の絶縁膜を形成し、前記半導体層の上面と平面的に重なるようにして導電膜からなる抵抗素子(例えばポリシリコン抵抗素子)を配置する。

(もっと読む)

薄膜トランジスタの製造方法

【課題】高温処理プロセスを適用することなく、酸化物半導体膜を効率的に製造できる薄膜トランジスタの製造方法を提供する。

【解決手段】

基板1上にゲート電極2を所定のパターンで形成する工程と、ゲート電極2を覆うゲート絶縁膜3を所定のパターンで形成する工程と、ゲート絶縁膜3上にアモルファス酸化物膜4’を所定のパターンで形成する工程と、アモルファス酸化物膜4’上にソース電極6S及びドレイン電極6Dを所定のパターンで形成する工程と、ソース・ドレイン電極6S,6D間で露出するアモルファス酸化物膜4’を少なくとも覆う保護膜7を形成する工程とを有する。このアモルファス酸化物膜4’の形成工程では、RFスパッタリング法でアモルファス酸化物膜4’を成膜し、保護膜7の形成工程では、RFスパッタリング法で保護膜7を成膜して、アモルファス酸化物膜4’を半導体化する。

(もっと読む)

半導体装置

【課題】しきい値を電気的に調整可能な半導体装置を提供する。

【解決手段】半導体装置10では、チャネル領域14は対向する第1、第2の面14a、14bを有している。第1、第2不純物領域15、16が、チャネル領域14の両側に配設されている。第1ゲート電極18は、第1ゲート絶縁膜19を介して第1の面14aに、第1ゲート電圧Vg1が印加されると生じる第1反転層23の一側が第1不純物領域15に接触し、他側が第2不純物領域16から離間するように配設されている。第2ゲート電極20は、第2ゲート絶縁膜21を介して第2の面14bに、第2ゲート電圧Vg2が印加されると生じる第2反転層24の一側が第2不純物領域16に接触し、他側が第1不純物領域15から離間するように配設されている。第1、第2ゲート電圧Vg1、Vg2に応じて、第1、第2反転層23、24が接触し、第1、第2不純物領域15、16間が導通する。

(もっと読む)

EL表示装置

【課題】開口率の高い表示装置又は素子の面積の大きい半導体装置を提供することを課題

とする。

【解決手段】隣接する画素電極(又は素子の電極)の間に設けられた配線との下方にマル

チゲート構造のTFTのチャネル形成領域を設ける。そして、複数のチャネル形成領域の

チャネル幅の方向を前記画素電極の形状における長尺方向と平行な方向とする。また、チ

ャネル幅の長さをチャネル長の長さよりも長くすることでチャネル形成領域の面積を大き

くする。

(もっと読む)

半導体装置

【課題】トランジスタ領域におけるゲート間距離などのレイアウトに依存することなく、半導体層のチャネル領域に有効に応力を作用させることができる半導体装置を実現する。

【解決手段】MOSトランジスタを備える半導体装置の構成として、素子分離層4で素子分離されたトランジスタ領域を有する半導体層3と、トランジスタ領域で半導体層3の第1の面上にゲート絶縁膜5を介して形成されたゲート電極6と、トランジスタ領域で半導体層3の第1の面と反対側の第2の面上に形成された応力膜31とを備え、応力膜31は、シリサイド膜を用いて形成されている。

【選択図】図13  (もっと読む)

(もっと読む)

含ピロールヘテロアセン化合物、該化合物の製造方法、該化合物を含む薄膜及び該薄膜を含む有機半導体デバイス

【課題】有機半導体活性層の薄膜を与え得る新規な化合物が求められている。

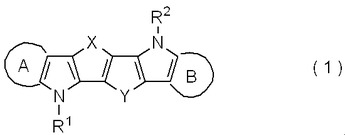

【解決手段】式(1)

(式中、X及びYは、硫黄原子、酸素原子、セレン原子、テルル原子又はSO2を表す。環構造A及び環構造Bは、芳香族炭化水素環又は芳香族複素環を表す。該芳香族複素環は単一の環構造である。

R1およびR2は、水素原子、炭素数1〜30のアルキル基、炭素数1〜30のアルコキシ基、炭素数2〜30のアルケニル基、炭素数2〜30のアルキニル基、炭素数1〜30のアルキルチオ基、炭素数6〜20のアリール基、炭素数4〜20のヘテロアリール基を表す。)

で表される含ピロールヘテロアセン化合物。

(もっと読む)

ホール形成方法、並びに該方法を用いてビアホールを形成した多層配線、半導体装置、表示素子、画像表示装置、及びシステム

【課題】プロセス再現性が高く、微細なホールを効率よく低コストで形成することができるホール形成方法、並びに、該ホール形成方法を用いてビアホールを形成した多層配線、半導体装置、表示素子、画像表示装置、及びシステムの提供。

【解決手段】基材上にピラー形成液を付与してピラーを形成するピラー形成工程と、前記ピラーが形成された基材上に絶縁膜形成材料を付与して絶縁膜を形成する絶縁膜形成工程と、前記ピラーを除去して前記絶縁膜に開口部を形成するピラー除去工程と、前記開口部が形成された絶縁膜を熱処理する熱処理工程とを含むホール形成方法である。

(もっと読む)

半導体装置

【課題】オン抵抗が低く、かつ、容易に素子分離もできる半導体装置を提供する。

【解決手段】第1絶縁膜2の上の第1導電型の第1半導体層3の表面を含む上部に設けられた第2導電型の第1半導体領域7と、第1半導体領域7の上部に設けられた第1導電型の第2半導体領域8と、側面が第1半導体層3と第1半導体領域7と第2半導体領域8に接する第1トレンチ4と、第1トレンチ4の側面に沿って設けられたゲート絶縁膜5と、第1トレンチ4内に埋め込まれたゲート電極6と、第1半導体領域7と第1トレンチ4から離れて第1半導体層3の上部に設けられた第1導電型の第3半導体領域9と、側面が第3半導体領域9に接し第3半導体領域9に対して第1半導体領域7の反対側に配置された第2トレンチ15と、第2トレンチ15の側面に沿って設けられた素子分離絶縁膜10と、第2トレンチ15内に埋め込まれたポリシリコン埋め込み領域11とを有する。

(もっと読む)

表示装置及び電子機器

【課題】アクティブマトリクス型基板において、薄膜トランジスタと、その端子接続部を

同時に作り込み、少ないマスク数で歩留まりの良い表示装置を提供する。

【解決手段】画素部および外部入力端子を有する表示装置であって、画素部は、ゲート電

極と、半導体膜と、ゲート電極上に形成された絶縁膜、および絶縁膜上に半導体膜と電気

的に接続された電極を有するTFTを有し、外部入力端子は、ゲート電極と同じ層に形成

された第1の配線と、電極と同じ層に形成され、絶縁膜に形成されたコンタクトホールを

介し第1の配線と接続された第2の配線と、第2の配線に接続され、第2の配線上に形成

された透明導電膜と、第2の配線と透明導電膜が接続している位置で透明導電膜と電気的

に接続するフレキシブルプリント配線板を有する表示装置。

(もっと読む)

アクセプター性の基を有する化合物、これを用いた有機薄膜及び有機薄膜素子

【課題】本発明の目的は、電子輸送性に優れる有機n型半導体として利用可能な化合物を提供することにある。本発明の目的はまた、係る化合物を含む有機薄膜、及びこの有機薄膜を備える有機薄膜素子を提供することにある。

【解決手段】かご状化合物又は脂肪族炭化水素化合物から誘導される4価以上の基であるコア部と、該コア部に結合した4以上の側鎖基と、を備え、側鎖基のうち2以上がアクセプター性の基を有する、化合物。

(もっと読む)

TFT基板

【課題】アクティブマトリクス型の表示装置の作製工程又は完成品における静電気による不良の発生を抑制する。

【解決手段】本発明に係る表示装置は、アクティブマトリクス回路の角の部分に隣接して、前記アクティブマトリクス回路に接続されていない格子状の放電パターンが形成されていることを特徴とする。また、本発明に係る表示装置は、アクティブマトリクス回路の周辺に、前記アクティブマトリクス回路を構成するゲイト線又はソース線と交わる放電パターンが形成され、前記放電パターンの長さは、前記アクティブマトリクス回路の画素ピッチよりも長いことを特徴とする。これらにより、各種静電破壊によるアクティブマト

クス型表示装置の不良の発生を抑制することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】ソース及びドレインのいずれか一方に高抵抗成分が付加されたときドレイン電流の低下を抑制する。

【解決手段】一つの実施形態によれば、半導体装置は基板、第一のソース及びドレイン、第二のソース及びドレイン、ゲート電極膜が設けられる。第一のソース及びドレインと第二のソース及びドレインは、基板表面に設けられる。第二のソース及びドレインの一方は、第一のソース及びドレインの一方に隣接配置される。第二のソース及びドレインの他方は、第一のソース及びドレインの他方に隣接配置される。ゲート電極膜は、第一及び第二のソース及びドレインの一方と第一及び第二のソース及びドレインの他方の間の基板表面上に設けられ、ゲート絶縁膜を介して設けられる。第一のソース及びドレインとゲート電極膜は第一のFETを構成し、第二のソース及びドレインとゲート電極膜は第二のFETを構成する。

(もっと読む)

同時両極性電界効果型トランジスタ及びその製造方法

【課題】単一金属酸化物半導体材料をチャネル層として使用時に極性をp型伝導又はn型伝導に変更できる同時両極性電界効果型トランジスタを実現し、さらに、該同時両極性TFTを用いたCMOS構造のトランジスタを提供する。

【解決手段】基板上に設けたチャネル層と、前記チャネル層上又は下にゲート絶縁膜を介して設けられて前記チャネル層のキャリア濃度を制御するゲート電極を有する電界効果型トランジスタにおいて、前記チャネル層材料は、酸化第一スズ(SnO)薄膜であり、前記チャネル層とゲート絶縁膜との界面の欠陥準位密度が5×1014cm−2eV−1以下であり、前記チャネル層は、電子(n型)及び正孔(p型)伝導性の両方の動作が可能な同時両極性を有することを特徴とする同時両極性電界効果型トランジスタ。

(もっと読む)

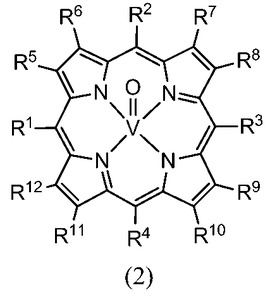

テトラビシクロポルフィリンバナジル錯体の製造方法、半導体層形成用組成物、電子デバイスの製造方法、太陽電池及び太陽電池モジュール

【課題】電子デバイスで好適に用いられるテトラベンゾポルフィリンバナジル錯体の高純度製造法の提供。

【解決手段】テトラビシクロポルフィリン化合物とバナジル化合物の反応を65℃以上95℃以下の温度で行う。式(2)の錯体の製造方法。 (もっと読む)

(もっと読む)

薄膜トランジスタ及びその製造方法、表示装置

【課題】低温プロセスで製造できる酸化物半導体を用いた高信頼性の薄膜トランジスタ及びその製造方法、表示装置を提供する。

【解決手段】薄膜トランジスタは、基板と、前記基板上に設けられ、インジウムを主成分とする酸化物で形成された半導体層140と、前記半導体層140のソース電極コンタクト領域およびドレイン電極コンタクト領域を除いた上面を覆う第1の絶縁膜と、少なくとも前記半導体層140の1対の側面を覆う、前記第1の絶縁膜と異なる条件で成膜された第2の絶縁膜と、前記絶縁膜上または前記半導体層140下に設けられたゲート電極120と、前記半導体層140のソース電極コンタクト領域上に設けられたソース電極161と、前記半導体層140のドレイン電極コンタクト領域上に設けられ、前記半導体層140の1対の側面を挟んで前記ソース電極161と対向するドレイン電極162と、を有する。

(もっと読む)

半導体装置

【課題】基板を介したクロストークを抑制でき、放熱性が高い半導体装置を提供する。

【解決手段】実施形態に係る半導体装置1は、半導体基板10を備える。前記半導体基板の内部には空洞11が形成されている。また、前記半導体基板の内部には、前記空洞を前記半導体基板の上面に連通させる連通孔12も形成されている。前記半導体装置は、さらに、前記空洞及び前記連通孔の内面上に設けられた絶縁膜13と、前記空洞及び前記連通孔の内部に埋め込まれ、熱伝導率が前記絶縁膜の熱伝導率よりも高い伝熱部材14と、前記半導体基板における前記空洞の直上域に形成された素子21,22と、を備える。

(もっと読む)

表示装置及び表示装置の製造方法

【課題】オン電流を確保しつつ、オフ電流を低減した薄膜トランジスタを有する表示装置を提供することを目的とする。

【解決手段】ゲート電極GTと、ゲート電極GTの上側に形成される結晶化された第1の半導体層MSと、第1の半導体層MSの上側に形成される、ソース電極STおよびドレイン電極DTと、第1の半導体層MSの側方から延伸して、ソース電極ST及びドレイン電極DTのうちの一方と第1の半導体層MSとの間に介在する第2の半導体層SLと、を有する表示装置であって、第2の半導体層SLは、第1の半導体層MSと接触して結晶化されて形成される第1部分SLaと、第1部分SLaよりも結晶性が低い第2部分SLbを有する、ことを特徴とする表示装置。

(もっと読む)

半導体装置及びその製造方法

【課題】寄生バイポーラトランジスタのゲインを低下することにより、誤動作や動作特性の変動が少ない半導体装置及びその製造方法を得る。

【解決手段】シリコン層3の上面上には、シリコン酸化膜6が部分的に形成されている。シリコン酸化膜6上には、ポリシリコンから成るゲート電極7が部分的に形成されている。ゲート電極7の下方に存在する部分のシリコン酸化膜6は、ゲート絶縁膜として機能する。ゲート電極7の側面には、シリコン酸化膜8を挟んで、シリコン窒化膜9が形成されている。シリコン酸化膜8及びシリコン窒化膜9は、シリコン酸化膜6上に形成されている。ゲート長方向に関するシリコン酸化膜8の幅W1は、シリコン酸化膜6の膜厚T1よりも大きい。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲート電極の電界集中を緩和して耐圧の更なる向上を実現することに加え、デバイス動作速度を向上させ、アバランシェ耐量が大きく、サージに対して強く、例えばインバータ回路等に適用する場合に外部のダイオードを接続することを要せず、ホールが発生しても安定動作を得ることができる信頼性の高い高耐圧の化合物半導体装置を実現する。

【解決手段】化合物半導体積層構造2に形成された電極用リセス2Cを、ゲート絶縁膜6を介して電極材料で埋め込むようにゲート電極7を形成すると共に、化合物半導体積層構造2に形成されたフィールドプレート用リセス2Dをp型半導体で埋め込み、化合物半導体積層構造2とp型半導体層8aで接触するフィールドプレート8を形成する。

(もっと読む)

281 - 300 / 3,265

[ Back to top ]