Fターム[5F110NN02]の内容

薄膜トランジスタ (412,022) | その他の構成要素 (47,691) | 保護膜(パッシベーション膜) (34,477) | 層間絶縁膜 (8,935)

Fターム[5F110NN02]の下位に属するFターム

Fターム[5F110NN02]に分類される特許

241 - 260 / 3,265

半導体装置

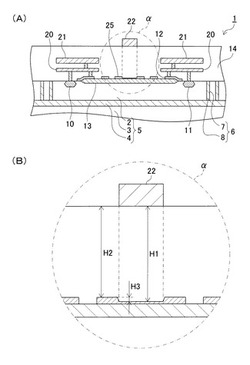

【課題】半導体装置において、高電圧の配線層とその下方を横切るように配置された抵抗層との間の絶縁膜の耐圧を確保し、この配線層と抵抗層との間で破壊が起きるのを抑制することを目的とする。

【解決手段】第1半導体領域10に接続され第2半導体領域11上を通過するように第3配線層22が配置されている。第3配線層22と第2半導体領域11との間に配置される絶縁膜14内には、一端が第3配線層22に接続されると共に、他端が第1半導体領域11よりも電位の低い制御端子12に接続され、且つ第3配線層22とSOI層2との間において第3配線層22を少なくとも1回以上横切る構成で抵抗層25が配置されている。この抵抗層25は、第3配線層22を横切る部位の上面が他の部位よりも下方位置となるように段差状に形成されている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】歩留まりに優れた半導体装置を提供する。

【解決手段】ゲート電極140は素子形成領域104に形成されている。サイドウォール層160は、ゲート電極140の側壁を覆っている。拡散領域170は素子形成領域104に位置する基板100に形成され、トランジスタ110のソース及びドレインとなる。絶縁層200は、素子形成領域104上、及びゲート電極140上に形成されている。コンタクト210は絶縁層200に形成され、拡散領域170に接続している。ゲート電極140のうちコンタクト210と隣に位置する部分は、サイドウォール層160より低く形成されている。絶縁層200は、ゲート電極140のうちコンタクト210と隣に位置する部分上かつ、サイドウォール層160同士の間に形成されている間隙に埋設される。

(もっと読む)

スパッタリングターゲット、酸化物半導体薄膜及びそれらの製造方法

【課題】スパッタリング法を用いて酸化物半導体膜を成膜する際に発生する異常放電を抑制し、酸化物半導体膜を安定かつ再現性よく得ることができるスパッタリングターゲットを提供する。

【解決手段】In、Ga、及びAlの割合が下記式(1)及び(2)の原子比となるように原料化合物を混合後、成形体とする工程、及び、前記成形体を、800℃から焼結温度までの温度範囲を0.1℃/分〜2℃/分の昇温速度で昇温した後、1450℃〜1650℃に10〜50時間保持することにより焼結する工程を含むことを特徴とする焼結体の製造方法。

Ga/(In+Ga+Al)=0.01〜0.08 (1)

Al/(In+Ga+Al)=0.0001〜0.03 (2)

(もっと読む)

NAND型不揮発性メモリのデータ消去方法

【課題】NAND型不揮発性メモリを提供する。

【解決手段】ビット線と、ソース線と、複数の不揮発性メモリが直列に接続されたNAND型セルと、選択トランジスタと、を有し、不揮発性メモリは、第1の絶縁膜を介した半導体上の電荷蓄積層と、第2の絶縁膜を介した電荷蓄積層上の制御ゲートと、を有し、NAND型セルの一方の端子は、選択トランジスタを介して、ビット線に接続され、NAND型セルの他方の端子は、ソース線に接続されたNAND型不揮発性メモリであって、第1の絶縁膜は、半導体に酸素雰囲気で高密度プラズマ処理を行った後、窒素雰囲気で高密度プラズマ処理を行うことで形成されるNAND型不揮発性メモリ。

(もっと読む)

薄膜トランジスタの製造装置およびその製造方法

【課題】フレキシブルな基板を用いても、高い精度で薄膜トランジスタを形成することができる薄膜トランジスタの製造装置およびその製造方法を提供する。

【解決手段】本発明は、基板上に薄膜トランジスタを製造する製造装置であり、基板に関する基板情報を取得する取得部と、取得部で得られた基板に関する基板情報に基づいて、基板の伸縮強度が高い方向を特定し、伸縮強度が高い方向と薄膜トランジスタのチャネル領域を挟んでソース電極およびドレイン電極が配置される配置方向とが直交するように薄膜トランジスタを形成する向きを設定する設定部とを有する。

(もっと読む)

記憶装置及び電子機器

【課題】メモリセル毎に選択動作を行う。

【解決手段】装置は、第1のメモリセルと、第1のメモリセルと同じ行に設けられた第2のメモリセルと、を具備し、前記第1及び第2のメモリセルのそれぞれは、第1のゲート及び第2のゲートを有し、オン状態又はオフ状態になることにより、メモリセルにおける少なくともデータの書き込み及びデータの保持を制御する電界効果トランジスタを備え、前記第1のメモリセル及び前記第2のメモリセルが備える前記電界効果トランジスタの前記第1のゲートのそれぞれに電気的に接続される行選択線と、前記第1のメモリセルが備える前記電界効果トランジスタの前記第2のゲートに電気的に接続される第1の列選択線と、前記第2のメモリセルが備える前記電界効果トランジスタの前記第2のゲートに電気的に接続される第2の列選択線と、をさらに具備する。

(もっと読む)

ワイヤチャンネルを有する電界効果トランジスタ及びその製造方法

【課題】ワイヤチャンネルを有する電界効果トランジスタ及びその製造方法を提供する。

【解決手段】半導体基板100と、半導体基板100上に形成されたソース/ドレイン

領域142と、ソース/ドレイン領域142と電気的に連結され、2列及び少なくとも2

行で配列された複数個のワイヤチャンネル112e、114eと、複数個のワイヤチャン

ネル112e、114eをそれぞれ取り囲むゲート絶縁膜142aと、それぞれの複数個

のワイヤチャンネル112e、114e及びゲート絶縁膜142aを取り囲むゲート電極

と、を備える。

(もっと読む)

電気光学装置の製造方法

【課題】テトラエトキシシラン等のシラン系有機材料を用いたプラズマCVD法によりシリケートガラスを形成した場合でも、シリケートガラスから半導体層へのフッ素の侵入を防止することのできる電気光学装置の製造方法を提供すること。

【解決手段】液晶装置の製造方法において、ゲート電極3cの形成工程、低濃度不純物導入工程、および高濃度不純物導入工程を行った後、シランガス等のシラン系無機原料を用いたCVD法により第1絶縁膜411を形成する。次に、第1アニール工程において第1絶縁膜411をアニールした後、テトラエトキシシラン等のシラン系有機原料を用いたプラズマCVD法によりシリケートガラスからなる第2絶縁膜412を形成する。

(もっと読む)

薄膜トランジスタアレイ、表示装置、およびそれらの製造方法

【課題】本発明は、開口率を大きくする必要がなく、印刷に適し、複数画素を用いずに面積階調できる薄膜トランジスタアレイ、表示装置、および薄膜トランジスタアレイの製造方法を提供する。

【解決手段】画素の有効領域の幅をA、画素の有効領域のネガパターンの幅をBとしたとき、幅Bが幅Aよりも大きな薄膜トランジスタとする。あるいは、対向電極と画素電極の距離をCとしたとき、距離Cが幅Bの4分の1以上B以下である表示装置とする。

(もっと読む)

電界効果トランジスタの製造方法及びそれに用いる製造装置

【課題】生産性が高く微細な電界効果トランジスタとその製造方法ならびに製造装置を提供すること。

【解決手段】以下の工程(1)から(3)よりなる印刷工程により前記基板上へラインもしくはスペース最小幅が1から50μmであり、印刷位置精度が100ppm以下の機能性膜の形成を行うことを特徴とする電界効果トランジスタの製造方法としたもの。

工程(1) 版の画線部に相当する溝構造部にドクターブレードを用いたインキング法で、機能性材料が溶媒へ溶解もしくは分散した薬液を充填する工程。

工程(2) 転写シリンダーと前記版を接触させ、前記溝構造部の薬液を前記転写シリンダーへ転移させる工程。

工程(3) 前記転写シリンダー上の薬液を前記基板の所定の位置へ転写し、機能性膜の形成を行う工程。

(もっと読む)

フィン型電界効果トランジスタ

【課題】フィン型電界効果トランジスタはその動作原理から、低消費電力化を図るためには、動作時のバルク領域は完全空乏化される必要があった。結果として、プロセスばらつきがバルク領域のばらつきを生み、消費電力にばらつきを与えるという問題が生じていた。

【解決手段】本発明のフィン型電界効果トランジスタは、ゲート絶縁膜を介してチャネル領域に電界を印加するためのゲート電極を備えるフィン型電界効果トランジスタにおいて、バルク領域に所定の電位を印加するためのバルク電極を、ゲート電極と別に備えられている。このような構造にすることで、フィンの幅を空乏層程度に保つことを必要せず、基板電位を変化させることでデバイスの特性を変化させる、基板バイアス効果によって消費電力を削減することが可能となる。

(もっと読む)

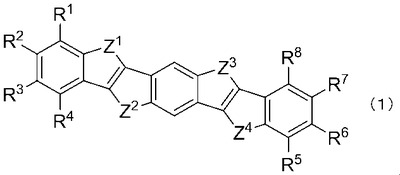

可溶性ヘテロアセン化合物及び該化合物を含有する薄膜および有機トランジスタ

【課題】有機半導体材料として好適な新規化合物の提供。

【解決手段】下記式(1)で示される化合物。

[式中、Z1〜Z4はそれぞれ独立に、硫黄原子又はセレン原子を表す。R1〜R8はそれぞれ独立に、水素原子、フッ素原子で置換されていてもよい炭素数1〜30のアルキル基、フッ素原子で置換されていてもよい炭素数1〜30のアルコキシ基、又は特定な置換シリル基を表す。]

(もっと読む)

非晶質酸化物薄膜トランジスタ及びその製造方法、その薄膜トランジスタを含むディスプレイパネル

【課題】本発明の実施例は非晶質酸化物薄膜トランジスタ及びその製造方法、ディスプレイパネルを開示する。

【解決手段】前記非晶質酸化物薄膜トランジスタは、ゲート電極、ゲート絶縁層、半導体活性層、ソース電極及びドレイン電極を含む。前記半導体活性層はチャネル層とオーミック接触層を含み、前記チャネル層は前記オーミック接触層に比べ酸素含有量が高い。また、前記チャネル層は前記ゲート絶縁層と接し、前記オーミック接触層は二つの独立したオーミック接触領域に分けられ、かつ前記二つの独立したオーミック接触領域はそれぞれ前記ソース電極、ドレイン電極と接する。

(もっと読む)

薄膜トランジスタ及びその製造方法並びに画像表示装置

【課題】薄膜トランジスタにおいて、ゲート絶縁膜に直接ストライプ状に凹部を形成することで隔壁形成プロセスを省き、前記凹部をガイドとして塗布法により精度よく半導体溶液を所望の場所に形成し、トランジスタ素子分離を行うことのできる薄膜トランジスタの構造を提供する。また、その構造を用いた薄膜トランジスタの製造方法、及びそれを用いたが画像表示装置を提供すること。

【解決手段】基板と、前記基板上に形成されたゲート電極と、前記基板上及び前記ゲート電極上のゲート絶縁体層と、前記ゲート絶縁体層に形成された凹部と、前記絶縁体層の凹部内に形成される半導体層と、前記半導体層上の中央部に設けられる保護膜と、前記半導体層の両端部で接続されるソース電極とドレイン電極と、を有する薄膜トランジスタにおいて、前記ゲート絶縁体層の凹部がストライプ状に形成されていることを特徴とする薄膜トランジスタとする。

(もっと読む)

電界効果トランジスタ

【課題】急峻なS値特性を有するとともに、ソース/ドレイン領域が同じ導電型となる対称構造を有する電界効果トランジスタを提供する。

【解決手段】本実施形態による電界効果トランジスタは、半導体層と、前記半導体層に離間して設けられたソース領域およびドレイン領域と、前記ソース領域と前記ドレイン領域との間の前記半導体層上に設けられたゲート絶縁膜と、前記ゲート絶縁膜上に設けられたゲート電極と、前記ソース領域および前記ドレイン領域側の前記ゲート電極の少なくとも一方の側面に設けられた高誘電体のゲート側壁と、を備え、前記ソース領域および前記ドレイン領域は前記ゲート電極の対応する側面から離れている。

(もっと読む)

表示装置、表示装置の製造方法および電子機器

【課題】低コストかつ簡易なプロセスで製造することが可能な表示装置およびその製造方法を提供する。

【解決手段】表示装置1は、酸化物半導体よりなる半導体層12上の選択的な領域(チャネル領域12A)に、ゲート絶縁膜13を介してゲート電極14が設けられ、そのチャネル領域12Aに隣接する領域(ソース・ドレイン接続領域12B)にソース・ドレイン電極層16が電気的に接続される。半導体層12では、これらのチャネル領域12Aおよびソース・ドレイン接続領域12Bとは異なる領域(画素電極部12C)がアノードとして利用される。製造プロセスにおいて、フォトマスク、フォトレジストなどの使用部材を減らし、工程数を削減することができる。

(もっと読む)

回路基板の製造方法

【課題】絶縁膜に形成されるヴィアホールの直径を縮小化することが可能で、高密度化に寄与することのできる回路基板の製造方法を提供する。

【解決手段】本発明の回路基板の製造方法は、基板10上に第1導電体を形成する第1導電体形成工程と、第1導電体を被覆する様にゲート絶縁膜21を成膜する第1絶縁膜成膜工程と、第1導電体上のゲート絶縁膜21に貫通孔32を開口して、当該貫通孔32を介して第1導電体の表面および基板の表面を部分的に露出させる貫通孔形成工程と、貫通孔32内に露出する第1導電体の表面を撥液化させる撥液化工程と、貫通孔32内に露出する第1導電体以外の領域に第2絶縁膜を形成する第2絶縁膜形成工程と、を含むことを特徴とする。

(もっと読む)

窒化物半導体装置及びその製造方法

【課題】低オン抵抗、高耐圧及び高信頼性を達成する。

【解決手段】窒化物半導体装置110は、第1半導体層3、第2半導体層4、第1電極10、第2電極7、第3電極8、第1絶縁膜6及び第2絶縁膜5を備える。第1半導体層3は、窒化物半導体を含む。第2半導体層4は、第1半導体層3上に設けられ、孔部4aを有する。第2半導体層4は、第1半導体層3よりも広い禁制帯幅を有する窒化物半導体を含む。第1電極10は、孔部4a内に設けられる。第1電極10の一方側に第2電極7、他方側に第3電極8が設けられ、それぞれ第2半導体層4と電気的に接続される。第1絶縁膜6は、酸素を含有する膜であって、第1電極10と孔部4aの内壁とのあいだ、及び第1電極10と第2電極7とのあいだに設けられ、第3電極8と離間して設けられる。第2絶縁膜5は、窒素を含有する膜であって、第1電極10と第3電極8とのあいだで第2半導体層4に接して設けられる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置の提供。

【解決手段】酸化物半導体材料を用いたトランジスタ162と、酸化物半導体以外の半導体材料を用いたトランジスタ160を組み合わせて用いることにより、書き込み回数にも制限が無く、長期間にわたる情報の保持ができる、新たな構造の半導体装置を実現することができる。さらに、酸化物半導体以外の半導体材料を用いたトランジスタと酸化物半導体材料を用いたトランジスタとを接続する接続電極130bを、当該接続電極と接続する酸化物半導体以外の半導体材料を用いたトランジスタの電極129より小さくすることにより、新たな構造の半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させることができる。

(もっと読む)

半導体装置

【課題】トランジスタのサイズを縮小しつつ、良好なスイッチング特性を有する半導体装置を提供する。

【解決手段】一対の第1の突起と、一対の第1の突起の間に設けられる第2の突起とを有するゲート電極と、ゲート電極を覆うゲート絶縁膜と、ゲート絶縁膜と接して、且つ一対の第1の突起および第2の突起に重畳する半導体膜と、半導体膜と接して、且つ一対の第1の突起と重畳する一対の電極と、を有し、半導体膜の側端は、半導体膜のチャネル幅方向において、一対の第1の突起の頂面より外側であり、一対の電極の側端は、半導体膜のチャネル幅方向において、一対の第1の突起の頂面より外側である半導体装置である。

(もっと読む)

241 - 260 / 3,265

[ Back to top ]