Fターム[5F110NN03]の内容

薄膜トランジスタ (412,022) | その他の構成要素 (47,691) | 保護膜(パッシベーション膜) (34,477) | 層間絶縁膜 (8,935) | 複数層 (3,316)

Fターム[5F110NN03]に分類される特許

3,101 - 3,120 / 3,316

延伸スペーサを利用した半導体デバイスおよびその形成方法

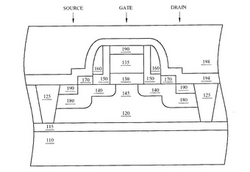

【課題】延伸スペーサを利用した半導体デバイスおよびその形成方法を提供する。

【解決手段】半導体デバイスは、半導体基板110を覆うゲートと、ゲートの側壁上にある誘電体ライナー150とを含む。この半導体デバイスは、誘電体ライナー150に隣接して誘電体ライナー150を越えるように半導体基板110に沿って横向きに延伸された延伸スペーサ170を含む。半導体デバイスは、半導体基板110の上面の下方に位置し、ゲート下のチャネル領域145に隣接するソース/ドレインをさらに含む。ソース/ドレインは、誘電体ライナー150および延伸スペーサ170下で延伸される。半導体デバイスは、ソース/ドレインの一部上を覆い、半導体基板110に沿って横向きに延伸するシリサイド領域190をさらに含む。従って、延伸スペーサ170はソース/ドレインの一部上において誘電体ライナー150とシリサイド領域190との間に形成される。

(もっと読む)

基板及び薄膜トランジスタを備えた基板

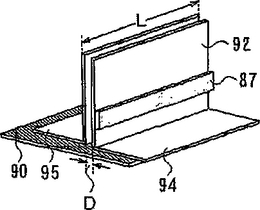

【課題】基板及び薄膜トランジスタを備えた基板を提供する。

【解決手段】製造工程において、熱的ストレスまたは蒸着ストレスなどによる変形が防止された基板のために、一面に変形防止層が備えられていることを特徴とする基板と、製造工程において、熱的ストレスまたは蒸着ストレスなどによる変形が防止された薄膜トランジスタを備えた基板のために、基板と、基板の一面に備えられた薄膜トランジスタと、基板の他面に備えられた少なくとも一つの層を備える変形防止層とを備えることを特徴とする薄膜トランジスタを備えた基板。

(もっと読む)

半導体を利用した薄膜トランジスタ表示板及びその製造方法

【課題】安定した接触特性及び電気的特性を有する信号線を含む有機半導体薄膜トランジスタ表示板の製造方法を提供する。

【解決手段】まず、絶縁基板上にゲート線を形成し、ゲート線を覆う有機絶縁物質のゲート絶縁膜を形成する。次に、ゲート絶縁膜上に常温で非晶質状態のITO膜を積層して感光膜パターンを利用した湿式エッチング工程でパターニングして、データ線及びドレイン電極を形成する。この時、エッチング液はクロムエッチング液を利用する。次に、感光膜パターンを除去した後でアニーリング工程を実施して、非晶質状態のITO膜を準結晶化する。次に、有機半導体を形成した後、ドレイン電極を露出する接触孔を有する保護膜を形成し、接触孔を通じてドレイン電極と連結される画素電極を形成する。

(もっと読む)

半導体装置

【課題】不揮発性であって、作成が簡単であり、追記が可能な記憶回路を有する半導体装置及びその作製方法の提供を課題とする。

【解決手段】一対の導電層間に有機化合物層が挟まれた単純な構造の記憶素子を有する半導体装置及びその作製方法を提供する。また、不揮発性であり、作製が簡単であり、追記が可能な記憶回路を有する半導体装置及びその作製方法を提供する。絶縁層上に設けられた複数の電界効果トランジスタと、複数の電界効果トランジスタ上に設けられた複数の記憶素子とを有する。複数の電界効果トランジスタは、単結晶半導体層をチャネル部とした電界効果トランジスタである。複数の記憶素子の各々は、第1の導電層と、有機化合物層と、第2の導電層が順に積層された素子である。

(もっと読む)

エッチング方法および半導体装置の作製方法

【課題】シロキサンを含む層を選択的にエッチングする技術について提供することを課題とする。また、本発明は、エッチングの際に生じる不具合に起因した動作不良等の低減された半導体装置を提供することを課題とする。

【解決手段】トランジスタに電気的に接続する導電層と、その導電層を覆う絶縁層とを形成した後、さらに絶縁層の上にマスクを形成する工程を有する。そしてマスクを形成した後、臭化水素ガスを含む処理用ガスを用いて絶縁層をエッチングすることを特徴としている。

(もっと読む)

有機薄膜トランジスタ、その製造方法、及びそれを具備した平板表示装置

【課題】 有機薄膜トランジスタ、その製造方法及びそれを具備した平板表示装置を提供する。

【解決手段】 基板110の表面上に形成されたソース/ドレイン電極120a,120bと、ソース/ドレイン電極120a,120bの上部に配置されて、ソース/ドレイン領域及びチャンネル領域を備える有機半導体層130と、有機半導体層130の上部に配置されるゲート電極150と、有機半導体層の表面上に配置される第1絶縁層140aと、を備え、有機半導体層130のソース/ドレイン領域とチャンネル領域とを含む活性領域の外郭部に沿って、有機半導体層130及び第1絶縁層140aの少なくとも一部に貫通部131,142aが備えられることを特徴とする有機薄膜トランジスタ。

(もっと読む)

半導体装置およびその製造方法

【課題】 信頼性の高いフルシリサイドMOSFETおよびシリサイドMOSFETを従来よりも簡単に同一基板上に形成することができる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板10上にゲート絶縁膜30を形成し、ゲート絶縁膜上に第1のゲート電極40および第2のゲート電極42を形成し、第1のゲート電極および第2のゲート電極上にマスク材料90を堆積し、第2のゲート電極を被覆したまま第1のゲート電極の上面を露出させるようにマスク材料をパターニングし、マスク材料を利用して第1のゲート電極の上部をエッチングし、マスク材料を除去し、第1のゲート電極および第2のゲート電極上に金属膜100を堆積し、第1のゲート電極の全部および第2のゲート電極の上部をシリサイド化することを具備する。

(もっと読む)

表示装置の作製方法

従来のフォトリソグラフィーを用いた配線作製工程では、レジストや配線材料、またプラズマ処理時に必要なプロセスガス等の多くが無駄になってしまう。また真空装置等の排気手段が必要であることから、装置全体が大型化するため、処理基板の大型化に伴い製造コストが増加することが問題になっていた。本発明では、レジストや配線材料を液滴として、基板上の必要な箇所に直接線状または点状に噴射して、パターンを描画するという手段を適用する。またアッシングやエッチング等の気相反応プロセスを大気圧又は大気圧近傍下で行う手段を適用する。  (もっと読む)

(もっと読む)

電気光学装置

【課題】電気光学装置に用いるインバータ回路に関する。

【解決手段】インバータのNチャネル型薄膜トランジスタは、チャネル領域と、複数のN型の不純物領域が設けられた半導体層と、前記半導体層上に設けられたゲイト絶縁膜と、前記ゲイト絶縁膜上に設けられ、かつ前記N型の不純物の少なくとも1つと重なっているゲイト電極とを有する。

またインバータ回路のPチャネル型薄膜トランジスタは、チャネル領域と、複数のP型の不純物領域が設けられた半導体層と、前記半導体層上に設けられたゲイト絶縁膜と、前記ゲイト絶縁膜上に設けられたゲイト電極と、を有する。

(もっと読む)

半導体装置

【課題】高い信頼性と動作性能とを兼ね備えた半導体装置を作製する。

【解決手段】薄膜トランジスタの半導体層は、チャネル形成領域114と、第1の不純物領域112,113と、第2の不純物領域115,116と、第3の不純物領域117,118とを有する。前記第1の不純物領域は、前記第2の不純物領域及び前記第3の不純物領域よりも濃度が高く、前記第2の不純物領域は前記第1の不純物領域と前記第3の不純物領域との間に設けられ、前記第3の不純物領域は前記第1の不純物領域よりも前記チャネル形成領域に近く設けられる。前記ゲート電極108は前記チャネル形成領域及び前記第2の不純物領域と重なり、前記第2の不純物領域に含まれる不純物の濃度は、前記チャネル形成領域から前記第1の不純物領域に向かって増加している。

(もっと読む)

薄膜パターン形成方法、半導体装置、電気光学装置、及び電子機器

【課題】 薄膜形成領域の断面全域に機能液を充填することにより、形成される薄膜の機能を実現するために充分な断面積と必要な断面形状を有する薄膜を形成することができる、薄膜パターン形成方法、半導体装置、電気光学装置、及び電子機器を実現する。

【解決手段】 薄膜パターン形成方法は、第1の薄膜を構成する材料を含む機能液に対して親液性を有する第2の薄膜を形成するステップと、第2の薄膜の表面に、機能液に対する撥液性を付与する処理を行うステップと、第2の薄膜の一部を取り除いて、第1の薄膜のパターン形状を規定する凹部を形成するステップと、凹部に向けて機能液を吐出するステップと、凹部に吐出された機能液を乾燥させて第1の薄膜を形成するステップとを有する。半導体装置の回路配線は、上記薄膜パターン形成方法を用いて形成されており、電気光学装置は当該半導体装置を備え、電子機器は上記電気光学装置を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】 様々なパターンを有するゲート電極をフルシリサイド化することができる半導体装置の製造方法を提供する。

【解決手段】 半導体装置の製造方法は、半導体基板10上にゲート絶縁膜30を形成し、ゲート絶縁膜上に、第1のゲート電極40および第1のゲート電極よりもゲート長またはゲート幅が大きい第2のゲート電極40を形成し、第2のゲート電極の厚みが第1のゲート電極の厚みよりも薄くなるように第2のゲート電極の上部を選択的にエッチングまたは研磨し、第1のゲート電極および第2のゲート電極上に金属膜100を堆積し、第1のゲート電極の全部および第2のゲート電極の全部をシリサイド化することを具備している。

(もっと読む)

表示装置

【課題】高画質で信頼性の高い表示装置を低いコストで歩留まり良く製造することができる技術を提供することを目的とする。

【解決手段】画素領域における画素電極層上にスペーサを有する、また、画素電極層周辺を覆う隔壁として機能する絶縁層表面は、絶縁層下の積層物を反映して画素電極表面からの高さが高く形成される。これらのスペーサ、及びスペーサとして機能する絶縁物によって、発光材料を画素電極層上に形成する際、選択的に形成するためのマスクは支持され、マスクのよじれやたわみなどによって画素電極層に接することを防止する。よって、画素電極層にはマスクによる傷などの損傷が生じず、画素電極層は形状不良とならないので、高繊細な表示を行う、高信頼性な表示装置を作製することができる。

(もっと読む)

半導体装置及び表示装置の製造方法

導電性材料を噴射する第一の溶液噴射手段を用いて配線を形成する工程と、第二の溶液噴射手段を用いて前記配線の上にレジストマスクを形成する工程と、前記レジストマスクをマスクとして、線状のプラズマ発生手段を有する大気圧プラズマ装置、又は、複数のプラズマ発生手段が線状に配列された大気圧プラズマ装置を用いて前記配線をエッチングする工程とを有する。  (もっと読む)

(もっと読む)

半導体装置および電気光学装置

【課題】製造工程を増やすことなく、寸法精度の高いダイオード素子をTFTとともに基板上に備えた半導体装置の製造方法、電気光学装置の製造方法、半導体装置、および電気光学装置を提供する。

【解決手段】同一基板10b上にTFT30、80、90のソース・ドレイン領域を形成するための高濃度不純物導入工程を利用して、ダイオード素子50の高濃度N型領域52および高濃度P型領域53を形成し、かつ、それらの間に真性領域51を形成する。その際、TFT30、90の高濃度ソース・ドレイン領域を形成する際に形成するレジストマスクの開口部のみでダイオード素子50の高濃度N型領域52の形成領域を規定するので、真性領域51を高い精度で形成することができる。

(もっと読む)

薄膜トランジスタ表示板

【課題】 表示信号線と検査用配線とを接続する接続部の接触信頼度を確保することができる薄膜トランジスタ表示板を提供する。

【解決手段】 本発明による薄膜トランジスタ表示板は、複数のゲート線、ゲート線と交差する複数のデータ線、ゲート線のうちの一つとデータ線のうちの一つに各々接続されている複数のスイッチング素子、スイッチング素子と各々接続されている複数の画素電極、ゲート線またはデータ線の端部に隣接するように配置されている少なくとも一つ以上の検査線、ゲート線とデータ線とスイッチング素子を覆ってゲート線またはデータ線の端部を各々露出する複数の第1接触孔と各々のゲート線またはデータ線に対応して検査線を露出する複数の第2接触孔を有する絶縁膜、絶縁膜の上部に形成されていて複数の第1及び第2接触孔を通じて少なくとも一つの検査線と複数のゲート線または複数のデータ線を接続されている複数の導電膜が共通に接続されて行われた補助検査線を含む。

(もっと読む)

ビームホモジナイザ、レーザ照射装置、及び半導体装置の作製方法

【課題】レーザビームのビームパラメータに影響されることなく、レーザビームの損失を防止し、常に照射面にエネルギー分布の均一なビームスポットを形成することができるビームホモジナイザ、およびレーザ照射装置の提供、並びに半導体装置の作製方法の提供。

【解決手段】レーザ発振器から射出したレーザビームの均一化に用いる光導波路又はライトパイプの入射口に偏向体を備える。前記偏向体の反射面をレーザビームの光軸に対して傾斜角度を持たせるように備えることにより、光導波路又はライトパイプの入射口径を広げレーザビームの損失を防止する。また、偏向体に角度調整機構を備えることにより、導波部射出口においてエネルギー分布の均一なビームスポットを形成する。

(もっと読む)

導電体用エッチング液及びこれを利用した薄膜トランジスタ表示板の製造方法

【課題】製造工程及び費用を最少化しながらも優れたプロファイルを得ることができる導電体用エッチング液及びこれを利用した薄膜トランジスタ表示板の製造方法を提供する。

【解決手段】 導電体を65乃至75重量%のリン酸、0.5乃至15重量%の硝酸、2乃至15重量%の酢酸、0.1乃至8.0重量%のカリウム化合物及び残量の水を含むエッチング液組成物を利用して写真エッチングする段階を含む。

(もっと読む)

銅配線層の形成方法、半導体装置の製造方法

【課題】 細りのない所望する断面積の銅配線を形成することができる銅配線層の形成方法および半導体装置の製造方法を提供すること。

【解決手段】 基板1上に下地絶縁膜2、下地バリア層3、銅シード層4を順次成膜したのち、この銅シード層4上にフォトレジスト層5の配線溝6パターンを形成し、この配線溝6の底部に露出した銅シード層4上に銅配線層7を形成し(図2(a))、この層7上に保護層8を形成したのちこの層8をマスクとしてフォトレジスト層5、銅シード層4、下地バリア層3を順次エッチングして図2(e)に示す銅配線層7のパターンを形成する。

この層7からの銅の拡散を防止するため表面に層間絶縁層を形成する。

(もっと読む)

配線の作製方法

スピン塗布によりレジストの被膜を形成する場合、無駄となってしまうレジスト材料が存在し、さらに、必要に応じて端面洗浄の工程が増えてしまう。また、真空装置を用いて、基板上に薄膜を成膜する際には、チャンバー内を真空にする特別な装置や設備が必要で、製造コストが高くなってしまう。本発明は、絶縁表面を有する基板上に、CVD法、蒸着法又はスパッタ法により選択的に導電層を形成するステップと、前記導電層に接するように、組成物を吐出してレジストマスクを形成するステップと、前記レジストマスクを用いて、大気圧又は大気圧近傍下で、プラズマ発生手段により前記導電層をエッチングするステップと、大気圧又は大気圧近傍下で、前記プラズマ発生手段により前記レジストマスクをアッシングするステップを有することを特徴とする。上記特徴により、材料の利用効率を向上させて、製造コストの低減を実現する。  (もっと読む)

(もっと読む)

3,101 - 3,120 / 3,316

[ Back to top ]