Fターム[5F110NN71]の内容

Fターム[5F110NN71]の下位に属するFターム

Fターム[5F110NN71]に分類される特許

1,941 - 1,960 / 2,024

剥離および封止可能な装置、ICシート、ICシートの巻物およびICチップの作製方法

【課題】 薄膜集積回路の封止の際の製造効率の悪化を防止し、損傷や破壊を防止することを課題とする。また、基板からの薄膜集積回路の剥離および剥離した薄膜集積回路の封止を効果的に行い、製品の歩留まりを向上させることを課題とする。

【解決手段】 薄膜集積回路が複数設けられた基板を搬送する搬送手段と、薄膜集積回路の一方の面を第1のシート材に接着させて、基板から薄膜集積回路を剥離する第1の剥離手段と、薄膜集積回路の他方の面を第2のシート材に接着させて、第1のシート材から薄膜集積回路を剥離する第2の剥離手段と、薄膜集積回路を第2のシート材と第3のシート材で挟み込み、薄膜集積回路を封止するラミネート手段とを有するラミネート装置を提供する。

(もっと読む)

薄膜トランジスタパネル及びその製造方法

【課題】 アモルファスシリコン薄膜トランジスタとポリシリコン薄膜トランジスタとを備えた画像読取装置において、より一層の小型化を図る。

【解決手段】 アモルファスシリコンからなる半導体薄膜41を有する光電気変換型の薄膜トランジスタ3は、ポリシリコンからなる半導体薄膜25、26を有する駆動回路用のCMOS薄膜トランジスタ21、22よりも上層側に設けられている。この場合、薄膜トランジスタ3のボトムゲート電極9、ソース・ドレイン電極10及びトップゲート電極8と薄膜トランジスタ21、22のソース・ドレイン電極に接続される導電体層35、36とを接続するための上層接続配線48、51、54は、ボトムゲート電極9、ソース・ドレイン電極10及びトップゲート電極8の各電極と同一の層に、同一の導電材料により形成され、下層接続配線50、53、56は、導電体層35、36と同一の層に、同一の導電材料により形成される。

(もっと読む)

薄膜トランジスタパネル及びその製造方法

【課題】 アモルファスシリコン薄膜トランジスタとポリシリコン薄膜トランジスタとを備えた薄膜トランジスタパネルにおいて、より一層の小型化を図る。

【解決手段】 アモルファスシリコンからなる半導体薄膜41を有する光電気変換型の薄膜トランジスタ3は、ポリシリコンからなる半導体薄膜25、26を有する駆動回路用のCMOS薄膜トランジスタ21、22よりも上層側に設けられている。これにより、半導体薄膜41を半導体薄膜25、26と同一の層上に設ける場合と比較して、より一層の小型化を図ることができる。この場合、薄膜トランジスタ3のボトムゲート電極9、ソース・ドレイン電極10及びトップゲート電極8と薄膜トランジスタ21、22のソース・ドレイン電極を含む導電体層35、36とを接続する接続配線の一部である上層接続配線48、51、54は、トップゲート電極8が設けられたトップゲート絶縁膜39上に設けられている。

(もっと読む)

半導体装置およびその作製方法

【課題】 従来のパルス発振のレーザー光による照射を半導体膜に行った場合、半導体表面にリッジと呼ばれる凹凸が形成され、トップゲート型TFTの場合には、素子特性がリッジにより大きく左右されていた。特に、電気的に並列に接続する複数の薄膜トランジスタ間でのバラツキが問題となっている。

【解決手段】 本発明は、複数の薄膜トランジスタからなる回路の作製において、連続発振レーザを用いて半導体膜にレーザ光を照射して溶融する領域の幅LP(微結晶領域を含まない)を大きくし、一つの領域に複数の薄膜トランジスタ(電気的に並列に連結された薄膜トランジスタ)の活性層を配置することを特徴の一つとする。

(もっと読む)

キャパシタ及びキャパシタ装置

【課題】 2つのキャパシタが直列に連結して,面積が狭くても十分な容量を有するキャパシタ装置を提供する。

【解決手段】 不純物がドーピングされた多結晶シリコン層と,前記多結晶シリコン層上に形成される第1絶縁層と,前記第1絶縁層上に,第1領域及び第2領域がそれぞれ分離されるように形成される第1金属層と,前記第1金属層上に形成される第2絶縁層と,前記第2絶縁層上に,前記第1金属層の第2領域と電気的に連結されるように形成される第2金属層とを備える。

(もっと読む)

レーザ照射装置およびレーザ照射方法

【課題】半導体膜全面に対して均一にレーザ処理を行うことができるレーザ照射装置を提供すること、およびレーザ照射方法を提供すること。

【解決手段】第1のレーザ発振器より出射された第1のレーザビームは、スリットを通し、さらに集光レンズを通した後に照射面に入射させる。同時に、照射面において第2のレーザ発振器より出射された第2のレーザビームを第1のレーザビームに重ねて照射する。さらに、照射面に対して相対的に走査することによって、照射面を等しくアニールする。

(もっと読む)

アクティブマトリクス基板の製造方法、アクティブマトリクス基板、電気光学装置並びに電子機器

【課題】 ドライプロセスとフォトリソエッチングを組み合わせた工程の回数を低減することができるアクティブマトリクス基板の製造方法等を提供することを目的とする。

【解決手段】 アクティブマトリクス基板20の製造方法において、第1方向又は第2方向のいずれか一方の配線42が交差部56において分断された格子パターンの配線40,42,46を基板P上に形成する第1工程と、交差部56及び配線40,42,46の一部上に絶縁膜と半導体膜30とからなる積層部を形成する第2工程と、積層部上に分断された配線42を電気的に連結させる導電層49、及び半導体膜30を介して配線42と電気的に接続される画素電極45を形成する第3工程と、を有する。

(もっと読む)

半導体装置の製造方法、及び半導体装置

【課題】半導体装置の基体層に対し、剥離層を確実に形成すると共に、水素のイオン注入を容易に制御できるようにする。

【解決手段】半導体装置Sの製造方法は、活性領域30が形成された複数の第1領域R1と、各第1領域R1同士の間に設けられた第2領域R2とを有する基体層1を備えた半導体装置Sの製造方法であって、活性領域30を覆うゲート酸化膜7の表面と高さが同じようになるように第2領域R2に素子分離用絶縁膜5を形成する素子分離用絶縁膜形成工程と、素子分離用絶縁膜形成工程の後に、基体層1に水素をイオン注入して剥離層を形成する剥離層形成工程と、剥離層に沿って基体層1の一部を分離する分離工程とを備えている。

(もっと読む)

薄膜半導体装置及びその製造方法、電気光学装置、電子機器

【課題】 サージ電圧から内部回路を良好に保護することができる保護回路を構成でき、過大電圧により破壊された場合にも回路動作に不具合を生じることがない、信頼性に優れた保護回路素子を具備した薄膜半導体装置を提供する。

【解決手段】 基体と、該基体上に形成された半導体膜とを具備した薄膜半導体装置において、前記基体上に内部回路(主回路部)17と、保護回路部18と、端子部19とが設けられており、前記保護回路部18に、前記半導体膜を有するPINダイオードと、該PINダイオードのI層と絶縁膜を介して対向配置された浮遊電極とを備えた保護回路素子181,182が設けられている構成とした。

(もっと読む)

半導体装置および半導体装置の作製方法

(課題)様々な基材に被剥離層を貼りつけ、軽量された半導体装置およびその作製方法を提供することを課題とする。

(解決方法)本発明は、基板上に被剥離層を形成し、この被剥離層にエッチングストッパー膜が設けられた封止基板を接着材で貼り合わせ、その後、封止基板のみをエッチングまたは研磨によって除去する。残ったエッチングストッパー膜は、そのままブロッキング膜として機能させる。また、貼り付ける部材としてマグネットシートを貼り付けてもよい。  (もっと読む)

(もっと読む)

積層構造体、積層構造体を用いた電子素子、これらの製造方法、電子素子アレイ及び表示装置

【課題】 印刷法のような低コストかつ材料使用効率の高い方法が適用でき、簡便に微細なパターンの形成が可能であって、かつ、パターン形成以外に高付加価値機能を有し、より高移動度の半導体層を有する積層構造体を廉価に提供する。

【解決手段】 エネルギーの付与によって臨界表面張力が変化する材料を含み、より臨界表面張力の大きな高表面エネルギー部3とより臨界表面張力の小さな低表面エネルギー部4との少なくとも臨界表面張力の異なる2つの部位を有する濡れ性変化層2と、この濡れ性変化層2に対して高表面エネルギー部3の部位に形成された導電層5と、濡れ性変化層2に対して少なくとも低表面エネルギー部4の部位に接して設けられた半導体層6と、を有し、濡れ性変化層2は、メチレン基を含み、側鎖に疎水性基を有する高分子材料を含むように積層構造体1を構成した。

(もっと読む)

表示装置及びその作製方法、並びにテレビジョン装置

【課題】 本発明は、材料の利用効率を向上させ、少ないフォトマスク数で、しきい値のずれが生じにくく、高速動作が可能なTFTを有する表示装置の作製方法を提供する。

【解決手段】 本発明の表示装置の一は、絶縁表面上に設けられたソース電極層、ドレイン電極層及び画素電極層を有し、ソース電極層及びドレイン電極層上に一導電型を有する半導体層を有し、一導電型を有する半導体層上に結晶性半導体層を有し、結晶性半導体層に接してゲート絶縁層を有し、ゲート絶縁層に接してゲート電極層を有し、ゲート絶縁層、ゲート電極層、及び画素電極層上に絶縁層を有し、ゲート絶縁層及び絶縁層は、ソース電極層またはドレイン電極層に達する第1の開口部、及び画素電極層に達する第2の開口部を有し、第1の開口部及び第2の開口部に、ソース電極層またはドレイン電極層と画素電極層とが電気的に接続する配線層を有する。

(もっと読む)

薄膜電子デバイスをつくるためのインライン式の方法

薄膜電子デバイスを基板上につくるためのインライン式の方法であって;a)構造化可能層を基板上へと堆積させる工程と;b)パターン化可能材料を構造化可能層上へと第1パターンで堆積させる工程と;c)構造化可能層をパターン化可能材料で被覆されていない領域においてエッチングする工程とを具備したインライン式の方法。これら複数の工程は、途中で基板を周囲空気に曝すことなく行われる。 (もっと読む)

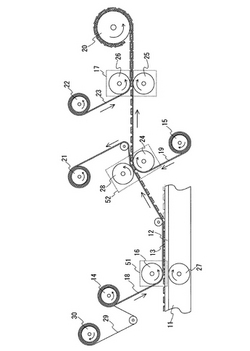

薄膜集積回路を封止する装置、ICシート、ICシートの巻物及びICチップの作製方法

【課題】 薄膜集積回路の封止の際の製造効率の悪化を防止し、また、損傷や破壊を防止することを課題とする。

【解決手段】 薄膜集積回路を封止する第1及び第2の基体のうち一方の基体を加熱溶融状態で押し出しながら供給し、他方の基体の供給とICチップの回収にはロールを用い、剥離処理と封止処理にローラーを用いる装置を提供する。ロールとローラーを回転させることにより、基板上に設けられた複数の薄膜集積回路を剥離し、剥離した薄膜集積回路を封止し、封止した薄膜集積回路を回収する作業を連続的に行うことができるため、製造効率を格段に向上させることができる。

(もっと読む)

有機薄膜トランジスタ材料、有機薄膜トランジスタ、電界効果トランジスタ及びスイッチング素子

【課題】 薄膜トランジスタ用途に有用な有機TFT材料を分子設計し、得られた有機TFT材料を用いて、キャリア移動度が高く、且つ、高耐久性を併せ持つ、有機TFT、電界効果トランジスタ、更に、該有機TFTまたは該電界効果トランジスタを有するスイッチング素子を提供する。

【解決手段】 重量平均分子量Mwが5,000〜10,000,000の範囲に有し、且つ、前記Mwと数平均分子量Mnとの比率Mw/Mnが3以下であるπ共役系構造を部分構造として有する高分子を含有することを特徴とする有機薄膜トランジスタ材料。

(もっと読む)

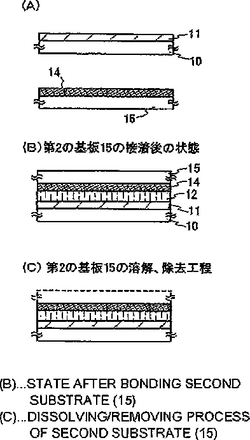

半導体装置および半導体装置の作製方法

(課題)

本発明は、被剥離層に損傷を与えない剥離方法を提供し、小さな面積を有する被剥離層の剥離だけでなく、大きな面積を有する被剥離層を全面に渡って歩留まりよく剥離することを可能とすることを目的としている。また、本発明は、様々な基材に被剥離層を貼りつけ、軽量された半導体装置およびその作製方法を提供することを課題とする。特に、フレキシブルなフィルムにTFTを代表とする様々な素子(薄膜ダイオード、シリコンのPIN接合からなる光電変換素子やシリコン抵抗素子)を貼りつけ、軽量された半導体装置およびその作製方法を提供することを課題とする。

(解決方法)

基板上に金属層11を設け、さらに前記金属層11に接して酸化物層12を設け、さらに被剥離層13を形成し、前記金属層11をレーザー光で照射することで酸化を行い金属酸化物層16を形成させれば、物理的手段で金属酸化物層12の層内または金属酸化物層16と酸化物層12との界面において、きれいに分離することができる。  (もっと読む)

(もっと読む)

表示装置

【課題】TFTと補助容量により各画素を駆動制御する表示装置において、電圧保持率を十分に維持しながら開口率を最大にすることができる表示装置を提供すること。

【解決手段】駆動回路基板118と、対向基板119と、これらの両基板の間に封止された液晶層112とを備え、駆動回路基板118には各画素に対応した駆動制御用の有機TFT117と補助容量部120とを有しており、有機TFT117のソース電極108、ドレイン電極109、ゲート電極104及び補助容量部120の補助容量電極103、特に補助容量電極103が透明導電材料で形成されることにより、開口率を最大にできる。

(もっと読む)

半導体デバイスの形成方法およびその構造

一実施形態では、半導体デバイス(10)の形成方法が示される。半導体基板(11)は、第1の部分(14または16)および第2の部分(18または20)を有する。第1の誘電体層(24または26)は半導体基板の第1の部分の上に形成され、第2の誘電体層(30)は半導体基板の第2の部分の上に形成される。ポリシリコンなどのシリコンを含み得るキャップ(28)は第1の誘電体層の上に形成される。第1の電極層(40)はキャップの上に形成され、第2の電極層(32,36または40)は第2の誘電体の上に形成される。  (もっと読む)

(もっと読む)

半導体装置、半導体装置の製造方法、並びに電気光学装置

【課題】 LDD又はGOLD構造を有する半導体装置の製造工程を簡略化する方法を提供する。

【解決手段】 本発明は、半導体装置の製造方法であって、半導体層上にソース側高濃度領域及びドレイン側高濃度領域に対応するレジストの膜厚を、ソース側低濃度領域、ドレイン側低濃度領域及びチャネル領域に対応するレジストの膜厚より薄く形成する工程と、レジストをマスクとして半導体層を所定パターンにエッチングするとともに、半導体層に高濃度不純物を注入し、ソース側高濃度領域及びドレイン側高濃度領域を形成する工程と、を有する。

(もっと読む)

無線プロセッサ、無線メモリ、情報処理システム、及び半導体装置

【課題】 本発明はプラスチック基板若しくはプラスチックフィルム基板のように熱的に脆弱な基板に、多結晶半導体を用いて高機能集積回路を形成したプロセッサであって、さらに無線で電力又は信号の送受信を行う無線プロセッサ、無線メモリ、及びその情報処理システムを提供することを課題とする。

【解決手段】 本発明は、厚さが10nm乃至200nmであって島状に分離された半導体膜により、少なくともチャネル形成領域が形成されるトランジスタを有する素子形成領域、及びアンテナを有し、トランジスタは、可撓性基板上に固定されおり、素子形成領域により高機能集積回路が形成されている無線プロセッサであり、当該無線プロセッサと、半導体装置とは、アンテナを介してデータ送受信を行うことを特徴とする情報処理システムである。

(もっと読む)

1,941 - 1,960 / 2,024

[ Back to top ]