Fターム[5F110NN78]の内容

Fターム[5F110NN78]に分類される特許

81 - 100 / 894

半導体装置およびその作製方法

【課題】従来のDRAMは、データを保持するために数十ミリ秒間隔でリフレッシュをしなければならず、消費電力の増大を招いていた。また、頻繁にトランジスタのオン状態とオフ状態が切り換わるのでトランジスタの劣化が問題となっていた。この問題は、メモリ容量が増大し、トランジスタの微細化が進むにつれて顕著なものとなっていた。

【解決手段】ワイドギャップ半導体を有するトランジスタを用い、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。ソース電極とドレイン電極との距離を狭くしてもゲート電極用のトレンチの深さを適宜設定することで、短チャネル効果の発現を抑制することができる。

(もっと読む)

半導体記憶装置

【課題】電源電圧の供給の停止及び再開を行う構成において、揮発性の記憶装置と不揮発性の記憶装置との間のデータの退避及び復帰の必要のない半導体記憶装置を提供する。

【解決手段】不揮発性の半導体記憶装置とする際、揮発性の記憶装置と不揮発性の記憶装置を分離することなく構成する。具体的に半導体記憶装置には、酸化物半導体を半導体層に有するトランジスタ及び容量素子に接続されたデータ保持部にデータを保持する構成とする。そしてデータ保持部に保持される電位は、電荷をリークすることなくデータの出力が可能なデータ電位保持回路及び電荷をリークすることなくデータ保持部に保持した電位を容量素子を介した容量結合により制御可能なデータ電位制御回路で制御される。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、配線数を削減することによって高集積化が図られた半導体装置を提供することを目的とする。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、書き込み用のワード線と読み出し用のワード線を共通化し、かつ書き込み用のビット線と読み出し用のビット線を共通化することにより配線数を削減し、更にソース線を削減することにより単位面積あたりの記憶容量を増加させる。

(もっと読む)

半導体装置

【課題】動作速度の低下を抑制しつつ、消費電力を低減する。

【解決手段】第1の半導体領域の上に絶縁領域を有し、且つ絶縁領域の上に第2の半導体領域を有する基板に設けられた第1の電界効果トランジスタと、基板の上に設けられた絶縁層と、絶縁層の一平面に設けられ、酸化物半導体層を含む第2の電界効果トランジスタと、第2の電界効果トランジスタのソース及びドレインと同一工程により形成され、第1の電界効果トランジスタの閾値電圧を制御するための電圧が供給される制御端子と、を備える。

(もっと読む)

記憶回路

【課題】消費電力を抑えることができる記憶回路の提供を目的の一つとする。

【解決手段】記憶回路に電源が供給されない間は、揮発性のメモリに相当する記憶部に記憶されていたデータを、不揮発性のメモリに相当する記憶部に設けられた容量素子によって保持する記憶回路である。不揮発性記憶部では、酸化物半導体層にチャネルが形成されるトランジスタを用いることによって、容量素子に保持された信号は長期間にわたり保持することができる。こうして、記憶回路は電源の供給が停止している間も論理状態(データ信号)を保持することが可能である。また酸化物半導体層にチャネルが形成されるトランジスタのゲートに印加する電位を、電源電位を供給する配線と前記トランジスタのゲートとの間に設けられた昇圧回路によって高くすることで、1つの電源電位であっても誤動作なくデータ信号の保持を行うことが可能である。

(もっと読む)

半導体記憶装置

【課題】電源電圧の供給の停止及び再開を行う構成において、揮発性の記憶装置と不揮発性の記憶装置との間のデータの退避及び復帰の必要のない半導体記憶装置を提供する。

【解決手段】不揮発性の半導体記憶装置とする際、揮発性の記憶装置と不揮発性の記憶装置を分離することなく構成する。具体的に半導体記憶装置には、酸化物半導体を半導体層に有するトランジスタ及び容量素子に接続されたデータ保持部にデータを保持する構成とする。そしてデータ保持部に保持される電位は、電荷をリークすることなくデータの出力が可能なデータ電位保持回路及び電荷をリークすることなくデータ保持部に保持した電位を容量素子を介した容量結合により制御可能なデータ電位制御回路で制御される。

(もっと読む)

記憶装置及び半導体装置

【課題】データの保持期間を確保しつつ、単位面積あたりの記憶容量を高めることができる記憶装置を提供する。

【解決手段】複数のビット線を幾つかのグループに分割し、複数のワード線も幾つかのグループに分割する。そして、一のグループに属するビット線に接続されたメモリセルには、一のグループに属するワード線が接続されるようにする。さらに、複数のビット線は、複数のビット線駆動回路102a,102b,102cによってグループごとにその駆動が制御されるようにする。加えて、複数のビット線駆動回路102a,102b,102cと、ワード線駆動回路101とを含めた駆動回路上に、セルアレイ103a,103b,103cを形成する。駆動回路とセルアレイ103a,103b,103cが重なるように三次元化することで、ビット線駆動回路が複数設けられていても、記憶装置の占有面積を小さくすることができる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】ワイドギャップ半導体、例えば酸化物半導体を含むメモリセルを用いて構成された半導体装置であって、メモリセルからの読み出しのために基準電位より低い電位を出力する機能を有する電位切り替え回路を備えた半導体装置とする。ワイドギャップ半導体を用いることで、メモリセルを構成するトランジスタのオフ電流を十分に小さくすることができ、長期間にわたって情報を保持することが可能な半導体装置を提供することができる。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化する。

【解決手段】酸化物半導体膜を含むトランジスタの作製工程において、非晶質酸化物半導体膜を形成し、該非晶質酸化物半導体膜に酸素を導入して酸素を過剰に含む非晶質酸化物半導体膜を形成する。該非晶質酸化物半導体膜上に酸化アルミニウム膜を形成した後、加熱処理を行い該非晶質酸化物半導体膜の少なくとも一部を結晶化させて、結晶性酸化物半導体膜を形成する。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体を用いたトランジスタ(より広義には、十分にオフ電流が小さいトランジスタ)を用いた記憶回路と、酸化物半導体以外の材料を用いたトランジスタ(換言すると、十分な高速動作が可能なトランジスタ)を用いた駆動回路などの周辺回路と、を一体に備える半導体装置とする。また、周辺回路を下部に設け、記憶回路を上部に設けることで、半導体装置の面積の縮小化及び小型化を実現することができる。

(もっと読む)

半導体装置およびその駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のチャネル形成領域と、第1のゲート電極と、第1のソース領域およびドレイン領域と、を有する第1のトランジスタと、少なくとも第1のソース領域またはドレイン領域の一部と重畳するように設けられた、酸化物半導体材料からなる第2のチャネル形成領域と、第2のソース電極と、第1のゲート電極に電気的に接続される第2のドレイン電極と、第2のゲート電極と、を有する第2のトランジスタと、第1のトランジスタと第2のトランジスタとの間の絶縁層と、を含むメモリセルを有し、第2のトランジスタをオフ状態とすべき期間において、少なくとも第1のソース領域またはドレイン領域に正の電位が与えられるときに第2のゲート電極に負の電位が与えられる半導体装置。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化することを目的の一とする。

【解決手段】第1の絶縁膜を形成し、第1の絶縁膜上に、ソース電極およびドレイン電極、ならびに、ソース電極およびドレイン電極と電気的に接続する酸化物半導体膜を形成し、酸化物半導体膜に熱処理を行って、酸化物半導体膜中の水素原子を除去し、水素原子が除去された酸化物半導体膜に酸素ドープ処理を行って、酸化物半導体膜中に酸素原子を供給し、酸素原子が供給された酸化物半導体膜上に、第2の絶縁膜を形成し、第2の絶縁膜上の酸化物半導体膜と重畳する領域にゲート電極を形成する半導体装置の作製方法である。

(もっと読む)

表示装置

【課題】酸化物半導体を用いた薄膜トランジスタを具備する画素において、開口率の向上

を図ることのできる発光表示装置を提供することを課題の一とする。

【解決手段】薄膜トランジスタ、及び発光素子を有する複数の画素を有し、画素は、走査

線として機能する第1の配線に電気的に接続されており、薄膜トランジスタは、第1の配

線上にゲート絶縁膜を介して設けられた酸化物半導体層を有し、酸化物半導体層は、第1

の配線が設けられた領域をはみ出て設けられており、発光素子と、酸化物半導体層とが重

畳して設けられる。

(もっと読む)

半導体装置の製造方法、及び電気光学装置の製造方法

【課題】信頼性の高いLDD構造のTFTを形成することが可能な半導体装置の製造方法、及び電気光学装置の製造方法を提供する。

【解決手段】第1領域155のPMOSTFTと、第2領域156のLDDを備えるNMOSTFTと、第3領域157のLDDを備えるNMOSTFTとを製造する製造方法は、厚みの異なる2種類の多階調レジスト211,212を形成し、多階調レジスト211,212をマスクとして不純物の注入とアッシングとを繰り返し、セルフアラインでLDDを形成する工程を有する。

(もっと読む)

半導体基板、その製造方法及び半導体装置

【課題】実施形態は、異なる種類の半導体素子のそれぞれに適合した半導体層が1つの絶縁膜上に設けられた半導体基板、その製造方法及び半導体装置を提供する。

【解決手段】実施形態に係る半導体基板は、第1絶縁層と、前記第1絶縁層の上に設けられた第1半導体層と、前記第1半導体層の上に選択的に設けられた第2絶縁層と、前記第2絶縁層を介して前記第1半導体層の上に設けられた第2半導体層と、を備える。さらに、前記第1半導体層の表面から前記第1絶縁膜に至る深さに延設され、前記第1半導体層における前記第1絶縁層と前記第2絶縁層との間の部分と、前記第1半導体層の残りの部分と、を電気的に分離した第3絶縁層を備える。

(もっと読む)

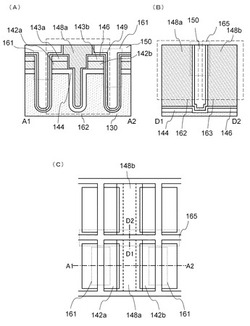

半導体基板およびその製造方法、その半導体基板を用いた半導体装置

【課題】実施形態は、異なる種類の半導体素子のそれぞれに適合した厚さを有する半導体層が1つの絶縁膜上に設けられた半導体基板およびその製造方法、その半導体基板を用いた半導体装置を提供する。

【解決手段】実施形態に係る半導体基板10は、第1絶縁層5と、前記第1絶縁層の上に設けられた半導体層7とを有する半導体基板であって、前記半導体層の中に選択的に設けられ、前記半導体層の表面に平行に延在し、その延在方向の長さが前記第1絶縁層よりも短い第2絶縁層13と、前記半導体層の表面から前記第1絶縁膜に至る深さに延設され、前記半導体層の前記第2絶縁層を含む部分と、前記半導体層の残りの部分と、を電気的に分離する第3絶縁層15と、を備える。

(もっと読む)

半導体記憶装置

【課題】不揮発性の記憶装置を有するCAMとする際に、メモリセルの低消費電力化を図ることのできる半導体記憶装置を提供することを課題の一とする。また、データの書き込みを繰り返し行う際の劣化をなくすことができる半導体記憶装置を提供することを課題の一とする。また、メモリセルの高密度化が可能な不揮発性の記憶装置を提供する。

【解決手段】酸化物半導体を半導体層に有する第1のトランジスタ及び当該第1のトランジスタをオフ状態とすることで書き込んだデータに対応する電位を保持できる容量素子を有するメモリ回路と、書き込んだ電位を参照するための参照回路を有し、参照回路を構成する第2のトランジスタの導通状態を検出することで、整合するデータのアドレスを取得し、高速な検索機能を可能にした半導体記憶装置である。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】省電力化かつ高速での書き込み処理が可能なメモリの多値化に適した半導体装置およびベリファイ処理を提供する。

【解決手段】半導体装置に用いるメモリセルを、酸化物半導体を用いたトランジスタと酸化物半導体以外の材料を用いたトランジスタをそれぞれ有する構成とし、書き込み回路を用いてデータバッファのデータをメモリセルに書き込む前に、予め各々のメモリセルの有するしきい値ばらつきを調べ、データバッファのデータに対して当該しきい値ばらつきを補正したデータが各々のメモリセルに書き込む。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いるトランジスタにおいて、電気特性の良好なトランジスタ及びその作製方法を提供する。

【解決手段】下地絶縁膜上に形成される酸化物半導体膜と、当該酸化物半導体膜とゲート絶縁膜を介して重畳するゲート電極と、酸化物半導体膜に接し、ソース電極及びドレイン電極として機能する一対の電極とを備えるトランジスタであり、下地絶縁膜は、酸化物半導体膜と一部接する第1の酸化絶縁膜と、当該第1の酸化絶縁膜の周囲に設けられる第2の酸化絶縁膜とを有し、トランジスタのチャネル幅方向と交差する酸化物半導体膜の端部は、第2の酸化絶縁膜上に位置するものである。

(もっと読む)

半導体装置およびその製造方法

【課題】シリコンエピタキシャル層の支えの喪失を防止した、局所SOI構造の形成方法の提供。

【解決手段】SiGe混晶層31SG1〜31SG4とシリコンエピタキシャル層31ES1,31ES2,31ES3および31ES4が積層された構造において、

それぞれ、Nウェル31NW及びPウェル31PWがSiGe混晶層31SG1〜31SG4側に突き出る構造を形成し、SiGe混晶層31SG1〜31SG4をエッチングにより除去する際に、支えとなるようにする。

(もっと読む)

81 - 100 / 894

[ Back to top ]