Fターム[5F110NN78]の内容

Fターム[5F110NN78]に分類される特許

101 - 120 / 894

半導体装置及びその作製方法

【課題】酸化物半導体を用いるトランジスタにおいて、電気特性の良好なトランジスタ及びその作製方法を提供する。

【解決手段】下地絶縁膜上に形成される酸化物半導体膜と、当該酸化物半導体膜とゲート絶縁膜を介して重畳するゲート電極と、酸化物半導体膜に接し、ソース電極及びドレイン電極として機能する一対の電極とを備えるトランジスタであり、下地絶縁膜は、酸化物半導体膜と一部接する第1の酸化絶縁膜と、当該第1の酸化絶縁膜の周囲に設けられる第2の酸化絶縁膜とを有し、トランジスタのチャネル幅方向と交差する酸化物半導体膜の端部は、第2の酸化絶縁膜上に位置するものである。

(もっと読む)

半導体装置およびその製造方法

【課題】シリコンエピタキシャル層の支えの喪失を防止した、局所SOI構造の形成方法の提供。

【解決手段】SiGe混晶層31SG1〜31SG4とシリコンエピタキシャル層31ES1,31ES2,31ES3および31ES4が積層された構造において、

それぞれ、Nウェル31NW及びPウェル31PWがSiGe混晶層31SG1〜31SG4側に突き出る構造を形成し、SiGe混晶層31SG1〜31SG4をエッチングにより除去する際に、支えとなるようにする。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層を含むトランジスタの作製工程において、ゲート電極を形成後、インライン装置にて、酸化アルミニウム膜と酸化シリコン膜と酸化物半導体膜を大気暴露することなく連続的に形成し、さらに同インライン装置にて加熱および酸素添加処理を行い、他の酸化アルミニウム膜でトランジスタを覆った後、熱処理を行うことで、水素原子を含む不純物が除去され、且つ、化学量論比を超える酸素を含む領域を有する酸化物半導体膜を形成する。該酸化物半導体膜を用いたトランジスタは、バイアス−熱ストレス試験(BT)試験前後においてもトランジスタのしきい値電圧の変化量が低減されており、信頼性の高いトランジスタとすることができる。

(もっと読む)

記憶回路、記憶装置、信号処理回路

【課題】電源電圧の供給が停止した後もデータ保持可能な記憶回路の提供、消費電力の低減可能な信号処理回路を提供する。

【解決手段】記憶回路は、トランジスタと、容量素子と、第1の演算回路と、第2の演算回路と、第3の演算回路と、スイッチと、を有し、第1の演算回路の出力端子は、第2の演算回路の入力端子と電気的に接続され、第2の演算回路の入力端子は、スイッチを介して第3の演算回路の出力端子と電気的に接続され、第2の演算回路の出力端子は、第1の演算回路の入力端子と電気的に接続され、第1の演算回路の入力端子は、トランジスタのソース及びドレインの一方と電気的に接続され、トランジスタのソース及びドレインの他方は、容量素子の一対の電極のうちの一方、及び第3の演算回路の入力端子と電気的に接続され、トランジスタのチャネルは酸化物半導体層に形成される。

(もっと読む)

半導体装置

【課題】安定したボディ固定動作と共に、高集積化、低寄生容量化や配線容量の低減化を図ることができる、SOI基板上に形成される半導体装置を得る。

【解決手段】ソース領域1,ドレイン領域2及びゲート電極3で形成されるMOSトランジスタにおいて、ゲート一端領域及びゲート他端領域に部分分離領域11a及び11bが形成され、部分分離領域11aに隣接してタップ領域21aが形成され、部分分離領域11bに隣接してタップ領域21bが形成される。部分分離領域11a,11b、タップ領域21a,21b及び活性領域1,2の周辺領域は全て完全分離領域10が形成される。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化する。

【解決手段】酸化物半導体膜を含むトランジスタの作製工程において、少なくとも酸化物半導体膜中に希ガスイオンを注入する注入工程を行い、減圧下、窒素雰囲気下、又は希ガス雰囲気下において、希ガスイオンを注入した酸化物半導体膜に加熱工程を行って希ガスイオンを注入した酸化物半導体膜中に含まれる水素若しくは水を放出させ、酸化物半導体膜を高純度化する。

(もっと読む)

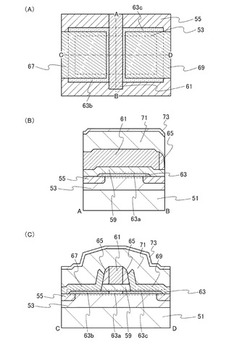

半導体装置

【課題】記憶内容に対する保持特性の改善を図ることが可能な半導体装置を提供する。また、半導体装置における消費電力の低減を図る。

【解決手段】チャネル形成領域に、トランジスタのオフ電流を十分に小さくすることができるワイドギャップ半導体材料(例えば、酸化物半導体材料)を用い、且つ、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能となる。また、ゲート電極用のトレンチを有することで、ソース電極とドレイン電極との距離を狭くしても該トレンチの深さを適宜設定することで、短チャネル効果の発現を抑制することができる。

(もっと読む)

過電流保護回路

【課題】入力電源電圧の動作保証範囲が大きいとしても当該電圧変動の影響を抑制して正常に過電流保護を図るようにした過電流保護回路を提供する。

【解決手段】支持基板10が第1半導体層11および第2半導体層12を絶縁層13で挟んで構成されている。第1半導体層11上には絶縁膜14を介してフィールドプレート抵抗膜20が形成されている。可変電流源ISが、ゲート電極19からドレイン電極17にかけて絶縁膜14上に沿って形成されたフィールドプレート抵抗膜20(フィールドプレート抵抗R1およびR2)に生じるノードN1の電圧に応じて出力電流値を変更してセンス抵抗Rsの検出電圧V2を補正する。

(もっと読む)

半導体記憶装置

【課題】集積度が高く、データ保持時間の長い半導体記憶装置。

【解決手段】基板上の半導体膜と、半導体膜を覆う第1のゲート絶縁膜と、第1のゲート絶縁膜を介して半導体膜上に設けられた第1のゲート電極と、第1のゲート絶縁膜上にあり、半導体膜と重畳しない、第1のゲート電極と同一層かつ同一材料である第1の導電膜と、第1のゲート絶縁膜上にあり、第1のゲート電極および第1の導電膜の上面を露出し、第1のゲート電極および第1の導電膜の間に溝部を有する絶縁膜と、該絶縁膜上にあり、第1のゲート電極、第1の導電膜および溝部と接する酸化物半導体膜と、酸化物半導体膜を覆う第2のゲート絶縁膜と、第2のゲート絶縁膜を介して酸化物半導体膜および溝部上に設けられた第2のゲート電極と、第2のゲート絶縁膜および酸化物半導体膜を介して第1のゲート電極上に設けられた、第2のゲート電極と同一層かつ同一材料である第2の導電膜と、を有する。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いるトランジスタにおいて、電気的特性の良好なトランジスタ及びその作製方法を提供することを課題の一とする。

【解決手段】基板上に酸化物半導体膜及び絶縁膜を有し、酸化物半導体膜の端部は絶縁膜と接しており、酸化物半導体膜は、チャネル形成領域と、チャネル形成領域を挟んで形成されたドーパントを含む領域とを含み、酸化物半導体膜上に接して形成されたゲート絶縁膜と、ゲート絶縁膜上に形成され、サイドウォール絶縁膜を有するゲート電極と、サイドウォール絶縁膜、酸化物半導体膜、および絶縁膜に接して形成されたソース電極およびドレイン電極とを有する半導体装置である。

(もっと読む)

発光装置

【課題】駆動用トランジスタと、スイッチング用トランジスタを有する発光装置において、トランジスタのばらつきを低減する。

【解決手段】駆動用トランジスタと、スイッチング用トランジスタを有する発光装置において、駆動用トランジスタのチャネル幅をチャネル長よりも小さくする。その際、ゲート配線と平行にアノード側電源線を設けて、フルカラー表示を行う。

(もっと読む)

半導体装置

【課題】小型化、薄型化、軽量化を実現した半導体装置の提供を課題とする。また、作製時間を短縮し、歩留まりを向上することができる半導体装置の作製方法の提供を課題とする。

【解決手段】トランジスタと、トランジスタ上に設けられた絶縁層と、絶縁層に設けられた開口部を介して、トランジスタのソース領域又はドレイン領域に電気的に接続された第1の導電層(ソース配線又はドレイン配線に相当)と、絶縁層及び第1の導電層上に設けられた第1の樹脂層と、第1の樹脂層に設けられた開口部を介して、第1の導電層に電気的に接続された導電性粒子を含む層と、第2の樹脂層及びアンテナとして機能する第2の導電層が設けられた基板とを有する。上記構成の半導体装置において、第2の導電層は、導電性粒子を含む層を介して、第1の導電層に電気的に接続されている。また、第2の樹脂層は、第1の樹脂層上に設けられている。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】特性の良好な半導体装置を形成する。

【解決手段】薄膜領域TA1中に第1の素子領域、第2の素子領域および第1の分離領域を有し、厚膜領域TA2中に第3の素子領域、第4の素子領域および第2の分離領域を有する半導体装置を次のように製造する。(a)絶縁層1bを介してシリコン層1cが形成された基板を準備する工程と、(b)基板の第1の分離領域および第2の分離領域のシリコン層中に素子分離絶縁膜3を形成する工程と、を有するよう製造する。さらに、(c)薄膜領域TA1にハードマスクを形成する工程と、(d)ハードマスクから露出した、第3の素子領域および第4の素子領域のシリコン層上に、それぞれシリコン膜7を形成する工程と、(e)第3の素子領域および第4の素子領域のシリコン膜7間に、素子分離絶縁膜11を形成する工程と、を有するよう製造する。

(もっと読む)

液晶表示装置

【課題】動作性能および信頼性の高い液晶表示装置を提供する。

【解決手段】トランジスタ上に第1の絶縁膜を有し、第1の絶縁膜上に第1及び第2の配線を有し、第1及び第2の配線上に第2の絶縁膜を有し、第2の絶縁膜上に電極を有し、電極上に第3の絶縁膜を有し、第3の絶縁膜上に画素電極を有し、画素電極は、電極と重なる第1の領域と、電極と重ならない第2の領域と、を有し、画素電極は、第1の配線に電気的に接続されており、第1の配線は、トランジスタのソース又はドレインの一方と電気的に接続されており、電極は、画素部の外側において前記第2の配線と電気的に接続されている。

(もっと読む)

薄膜半導体装置

【課題】工程を複雑にすることなく、多結晶シリコン膜に回路特性に適した複数の異なる

ゲート絶縁膜厚を有する薄膜トランジスタ(TFT)を同一基板に形成することができる

薄膜半導体装置とその製造方法を提供。

【解決手段】ガラス基板上に形成した多結晶シリコン膜に駆動電圧が異なるTFTを混載

する際に、低電圧駆動TFTではチャネル領域の不純物をアクセプタがより多くなるよう

にしあるいはドナーがより少なくなるようにし、高電圧駆動TFTではチャネル領域の不

純物をドナーがより多くなるようにしあるいはアクセプタがより少なくなるようにする。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置の小型化を実現する。

【解決手段】 第1の絶縁膜上に、島状の半導体層及び前記半導体層を囲む第2の絶縁膜を形成し、前記半導体層の上面と平面的に重なるようにして導電膜からなる抵抗素子(例えばポリシリコン抵抗素子)を配置する。

(もっと読む)

半導体装置の作製方法

【課題】側壁スペーサを形成することなく、且つ、工程数を増やすことなく、自己整合的にLDD領域を少なくとも一つ備えたTFTを提供する。また、同一基板上に、工程数を増やすことなく、様々なTFT、例えば、チャネル形成領域の片側にLDD領域を有するTFTと、チャネル形成領域の両側にLDD領域を有するTFTとを形成する作製方法を提供する。

【解決手段】回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターンを設置したフォトマスクまたはレチクルをゲート電極形成用のフォトリソグラフィ工程に適用して膜厚の厚い領域と、該領域より膜厚の薄い領域を片側側部に有する非対称のレジストパターンを形成し、段差を有するゲート電極を形成し、ゲート電極の膜厚の薄い領域を通過させて前記半導体層に不純物元素を注入して、自己整合的にLDD領域を形成する。

(もっと読む)

液晶表示装置

【課題】動作性能および信頼性の高い液晶表示装置を提供する。

【解決手段】第1のチャネル形成領域713と、第1のソース領域及び第1のドレイン領域と、ゲート絶縁膜と、第1のゲート電極とを備えた第1のTFTと、第2のチャネル形成領域714と、第2のソース領域及び第2のドレイン領域と、ゲート絶縁膜と、第2のゲート電極とを備えた第2のTFTと、第1のTFT及び第2のTFT上に設けられた第1の絶縁膜664と、第1のソース領域及び第1のドレイン領域の一方と接続されたソース配線668と、第1のソース領域及び第1のドレイン領域の他方と接続し、且つ第2のゲート電極に接続された第1のドレイン配線と、第1の絶縁膜上に設けられ、第2のソース領域及び第2のドレイン領域の一方に接続された第2のドレイン配線672と、第1の絶縁膜上に設けられ、第2のソース領域及び第2のドレイン領域の他方に接続された電流供給線と、を有する。

(もっと読む)

半導体装置

【課題】可撓性を有する基板上に有機化合物を含む層を有する素子が設けられた半導体装

置を歩留まり高く作製することを課題とする。

【解決手段】基板上に剥離層を形成し、剥離層上に、無機化合物層、第1の導電層、及び

有機化合物を含む層を形成し、有機化合物を含む層及び無機化合物層に接する第2の導電

層を形成して素子形成層を形成し、第2の導電層上に第1の可撓性を有する基板を貼りあ

わせた後、剥離層と素子形成層とを剥す半導体装置の作製方法である。

(もっと読む)

半導体装置及びその製造方法

【課題】寄生バイポーラトランジスタのゲインを低下することにより、誤動作や動作特性の変動が少ない半導体装置及びその製造方法を得る。

【解決手段】シリコン層3の上面上には、シリコン酸化膜6が部分的に形成されている。シリコン酸化膜6上には、ポリシリコンから成るゲート電極7が部分的に形成されている。ゲート電極7の下方に存在する部分のシリコン酸化膜6は、ゲート絶縁膜として機能する。ゲート電極7の側面には、シリコン酸化膜8を挟んで、シリコン窒化膜9が形成されている。シリコン酸化膜8及びシリコン窒化膜9は、シリコン酸化膜6上に形成されている。ゲート長方向に関するシリコン酸化膜8の幅W1は、シリコン酸化膜6の膜厚T1よりも大きい。

(もっと読む)

101 - 120 / 894

[ Back to top ]