Fターム[5F110PP35]の内容

Fターム[5F110PP35]に分類される特許

141 - 160 / 820

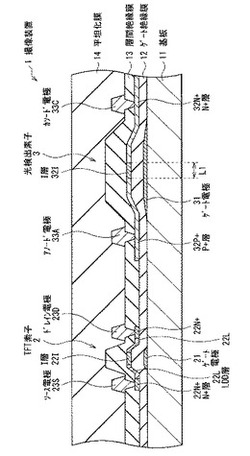

撮像装置、表示撮像装置および電子機器

【課題】製造工程を複雑化させることなく、光検出素子および駆動素子において高い特性を示すことが可能な撮像装置、表示撮像装置および電子機器を提供する。

【解決手段】光検出素子3におけるI層32I(チャネル領域,半導体層)と、TFT素子2におけるI層22I(チャネル領域,半導体層)とにおいて、それらの厚みおよび不純物濃度がそれぞれ互いに略等しくなっている。I層22I,32Iにおける平均トラップ順位密度がそれぞれ、2.0×1017(cm-3)以下となっている。2種類の半導体層(I層22I,32I)を、同一の工程で簡易に形成することができる。また、光検出素子3およびTFT素子2における特性をそれぞれ、高い値で両立させることができる。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】酸化物半導体を用いたトランジスタを有する半導体装置において、電気的特性の変動が小さく、信頼性の高い半導体装置を作製することを課題とする。

【解決手段】酸化物半導体を用いたトランジスタにおいて、トップゲート構造の場合は下地絶縁層に、ボトムゲート構造の場合は保護絶縁層に、酸素が過剰な酸化シリコン(SiOX(X>2))を用いる。酸素が過剰な酸化シリコンを用いることにより、絶縁層から酸素が放出され、酸化物半導体層中の酸素欠損及び下地絶縁層もしくは保護絶縁層と酸化物半導体層の界面準位密度を低減することができ、電気的特性の変動が小さく、信頼性の高い半導体装置を作製することができる。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体膜を用いた半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を作製することを課題の一とする。

【解決手段】ゲート絶縁層上に膜厚が2nm以上15nm以下の薄い第1の酸化物半導体膜を形成し、第1の加熱処理を行って第1の酸化物半導体膜の表面から内部に向かって結晶成長させて第1の結晶層を形成し、第1の結晶層上に第1の酸化物半導体膜よりも厚い第2の酸化物半導体膜を形成し、第2の加熱処理を行って第1の結晶層からその上の第2の酸化物半導体膜表面に向かって結晶成長させて第2の結晶層を形成し、第2の結晶層を形成した後、さらに酸素ドープ処理を行って第2の結晶層に酸素原子を供給する。

(もっと読む)

パターン付基板の作製方法、及び半導体装置の作製方法

【課題】隣接する膜パターンの間隔を制御することが可能なパターン付基板の作製方法を

提供する。また、膜パターンの幅の制御が可能で、特に、幅が細く且つ厚みのあるパター

ン付基板の作製方法を提供する。また、アンテナのインダクタンスのバラツキが少なく、

起電力の高い導電膜を有する基板の作製方法を提供することを課題とする。また、歩留ま

り高く半導体装置を作製する方法を提供することを課題とする。

【解決手段】基板、絶縁膜又は導電膜上に珪素及び酸素が結合し且つ前記珪素に不活性な

基が結合する膜を形成した後、珪素及び酸素が結合し且つ前記珪素に不活性な基が結合す

る膜表面に印刷法を用いて組成物を印刷し、組成物を焼成して膜パターンを形成すること

を特徴とする。

(もっと読む)

半導体膜の作製方法、及び半導体装置の作製方法

【課題】電気的特性ばらつきの小さい酸化物半導体膜の作製方法を提供することを課題とする。電気的特性ばらつきの小さい酸化物半導体膜を用いた半導体装置の作製方法を提供することを課題とする。

【解決手段】透光性を有する酸化物半導体層をパターニングする際に、基板ステージからの散乱光を低減、もしくはその回り込みを少なくするために、基板ステージに光が到達しないように、光の透過を防止する機能を有する層をフォトレジスト層よりも下層に配置し、パターニングを行えばよい。さらに上記パターニング方法で形成した酸化物半導体層を用いて半導体装置を作製すればよい。

(もっと読む)

半導体装置

【課題】貫通電流を低減させることができる相補型の論理回路を用いることで、消費電力を抑えることができる半導体装置の提案を目的の一とする。或いは、貫通電流を低減させることができる相補型の論理回路を用いることで、発熱を抑えることができる半導体装置の提案を目的の一とする。

【解決手段】通常のゲート電極の他に、閾値電圧を制御するための第2のゲート電極が備えられたnチャネル型トランジスタ、或いはpチャネル型トランジスタを、相補型の論理回路に用いる。そして、オフ電流が極めて小さい絶縁ゲート電界効果型トランジスタをスイッチング素子として用い、上記第2のゲート電極の電位を制御する。上記スイッチング素子として機能するトランジスタは、シリコン半導体よりもバンドギャップが広く、真性キャリア密度がシリコンよりも低い半導体材料を、チャネル形成領域に含む。

(もっと読む)

半導体装置及びその作製方法

【課題】微小なコンタクトホールを形成し、集積回路を微細化することを目的とする。

【解決手段】スイッチング素子および各配線を覆う層間絶縁膜111として有機材料を用い、且つ、金属膜112のマスクを用い、ドライエッチング法によってコンタクトホールを形成し、配線114を形成する。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化することを目的の一とする。

【解決手段】ゲート電極を形成し、ゲート電極上に第1の絶縁膜を形成し、第1の絶縁膜にハロゲンドープ処理を行って、第1の絶縁膜にハロゲン原子を供給し、第1の絶縁膜上に、ゲート電極と重畳して酸化物半導体膜を形成し、酸化物半導体膜に熱処理を行って、酸化物半導体膜中の水素原子を除去し、水素原子が除去された酸化物半導体膜に酸素ドープ処理を行って、酸化物半導体膜中に酸素原子を供給し、酸素原子が供給された酸化物半導体膜に熱処理を行い、酸化物半導体膜上に接して、ソース電極およびドレイン電極を形成し、第2の絶縁膜を形成する半導体装置の作製方法である。

(もっと読む)

アクティブマトリックス基板及び液晶装置

【課題】結晶性半導体膜を備え、光リーク電流の発生が抑制され、トランジスタ特性が良好なTFTを提供する。

【解決手段】アクティブマトリックス基板100において、結晶性半導体膜5はソース電極12側及び/又はドレイン電極13側がTFT108の外側でかつゲート電極2の外側の領域に引き出されており、ソース電極12又はソース配線110と結晶性半導体膜5との接触部SCとゲート電極2との間、及び/又は、ドレイン電極13と結晶性半導体膜5との接触部DCとゲート電極2との間に、ゲート電極2と同層の金属遮光膜3を備えている。結晶性半導体膜5のソース電極12又はソース配線110と結晶性半導体膜5との接触部SCとゲート電極2との間、及び/又は、ドレイン電極13と結晶性半導体膜5との接触部DCとゲート電極2との間に、n型不純物が導入された不純物導入領域を形成してもよい。

(もっと読む)

回路基板及び表示装置

【課題】 配線の特性の劣化を生じさせることなく、額縁面積を削減することが可能な回路基板、及び、該回路基板を備える表示装置を提供することを目的とする。

【解決手段】 支持基板上にトランジスタ及び外部接続端子が載置されたトランジスタ基板と、該トランジスタ基板上に取り付けられた外付け部材とを含んで構成される回路基板であって、上記外付け部材は、導電部材を介して外部接続端子と電気的かつ物理的に接続されており、上記トランジスタは、外部接続端子と横並びに配置されている回路基板である。

(もっと読む)

半導体装置

【課題】導電膜を有する半導体装置は、導電膜の内部応力の影響を受ける。内部応力について検討する。

【解決手段】単結晶シリコン基板に形成されたnチャネル型MOSFETを有する半導体装置において、チャネル形成領域が引っ張り応力を受けるように、導電膜には不純物が導入され、単結晶シリコン基板に形成されたpチャネル型MOSFETを有する半導体装置において、チャネル形成領域が圧縮応力を受けるように、導電膜には不純物が導入されている。

(もっと読む)

半導体装置及びその作製方法

【課題】半導体装置の作製工程数を減少させること、半導体装置の歩留まりを向上させること、半導体装置の作製コストを低減することを課題とする。

【解決手段】基板上に、単結晶半導体層をチャネル形成領域に有する第1のトランジスタと、当該第1のトランジスタと絶縁層を介して分離され、酸化物半導体層をチャネル形成領域に有する第2のトランジスタと、当該単結晶半導体層及び酸化物半導体層を有するダイオードを有する半導体装置、及び、その作製方法に関する。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化することを目的の一とする。

【解決手段】第1の絶縁膜を形成し、第1の絶縁膜上に、ソース電極およびドレイン電極、ならびに、ソース電極およびドレイン電極と電気的に接続する酸化物半導体膜を形成し、酸化物半導体膜に熱処理を行って、酸化物半導体膜中の水素原子を除去し、水素原子が除去された酸化物半導体膜に酸素ドープ処理を行って、酸化物半導体膜中に酸素原子を供給し、酸素原子が供給された酸化物半導体膜上に、第2の絶縁膜を形成し、第2の絶縁膜上の酸化物半導体膜と重畳する領域にゲート電極を形成する半導体装置の作製方法である。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】平坦な表面上に絶縁膜を形成し、絶縁膜上にマスクを形成し、マスクにスリミング処理を行い、マスクを用いて絶縁膜にエッチング処理を行い、絶縁膜を覆うように導電膜を形成し、導電膜および絶縁膜に研磨処理を行うことにより、導電膜および絶縁膜の厚さを等しくし、導電膜をエッチングして、導電膜より厚さの小さいソース電極およびドレイン電極を形成し、絶縁膜、ソース電極、およびドレイン電極と接する酸化物半導体膜を形成し、酸化物半導体膜を覆うゲート絶縁膜を形成し、ゲート絶縁膜上の絶縁膜と重畳する領域にゲート電極を形成する。

(もっと読む)

半導体装置及び電子機器

【課題】逆スタガ型TFTにおいて、薄膜の応力を用いてしきい値電圧を制御する。

【解決手段】基板上に形成された電極上に設けられた第1の絶縁層の応力と膜厚の積と、前記第1の絶縁層上に設けられた引張り応力を有する結晶質半導体膜からなる活性層の応力と膜厚の積と、前記活性層上に設けられた第2の絶縁層の応力と膜厚の積を適当な大きさに設定することでしきい値電圧を制御する。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化することを目的の一とする。

【解決手段】酸化物半導体膜を含むトランジスタにおいて、酸化物半導体膜に接し、且つソース電極およびドレイン電極を覆う帯電防止機能を有する金属酸化膜を形成し、該金属酸化膜を通過してハロゲン元素を導入(添加)し、加熱処理を行う。このハロゲン元素導入および加熱工程によって、水素、水分、水酸基または水素化物などの不純物を酸化物半導体膜より意図的に排除し、酸化物半導体膜を高純度化する。また、金属酸化膜を設けることで、トランジスタにおいて酸化物半導体膜のバックチャネル側に寄生チャネルが発生するのを防止する。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】良好な特性を維持しつつ微細化を達成した半導体装置の提供を目的の一とする。さらに、これらの微細化を達成した半導体装置の良好な特性を維持しつつ、3次元高集積化を図ることを目的の一つとする。

【解決手段】絶縁層中に埋め込まれた配線と、絶縁層上の酸化物半導体層と、酸化物半導体層と電気的に接続するソース電極及びドレイン電極と、酸化物半導体層と重畳して設けられたゲート電極と、酸化物半導体層と、ゲート電極との間に設けられたゲート絶縁層と、を有し、絶縁層は、配線の上面の一部を露出するように形成され、配線は、その上面の一部が絶縁層の表面の一部より高い位置に存在し、且つ、絶縁層から露出した領域において、ソース電極またはドレイン電極と電気的に接続し、絶縁層表面の一部であって、酸化物半導体層と接する領域は、その二乗平均平方根粗さが1nm以下である半導体装置である。

(もっと読む)

半導体膜の作製方法

【課題】量産性に優れた薄膜トランジスタを提供する。また半導体装置の作製において有

用な半導体薄膜を提供する。

【解決手段】プラズマCVD法により作製された希ガス元素を1×1020/cm3〜1

×1021/cm3で含む半導体膜を形成し、前記半導体膜の一部を除去して、活性層を

形成し、トップゲート型薄膜トランジスタまたはボトムゲート型薄膜トランジスタを作製

する。また、プラズマCVD法により作製された希ガス元素を1×1020/cm3〜1

×1021/cm3で含む半導体膜を剥離層として用いた半導体装置を作製する。また、

プラズマCVD法により作製された希ガス元素を1×1020/cm3〜1×1021/

cm3で含む半導体膜をゲッタリングサイトとして用いた半導体装置を作製する。

(もっと読む)

表示デバイスおよびその製法、ならびにスパッタリングターゲット

【課題】アルミニウム合金膜と透明電極が直接コンタクトすることを可能とし、バリアメタルの省略を可能にするアルミニウム合金膜を用いた表示デバイスとその製造技術を提供すること。

【解決手段】ガラス基板上に配置された薄膜トランジスタと、透明電極によって形成された画素電極と、これら薄膜トランジスタと画素電極を電気的に接続するアルミニウム合金膜によって形成された接続配線部を主たる構成要素として備えた表示デバイスとその製法を開示する。

(もっと読む)

整流回路、無線通信装置、整流回路の作製方法、および無線通信装置の作製方法

【課題】整流回路において、整流回路を構成する、いわゆるダイオード接続のMOSトランジスタに、オフ電流の小さいトランジスタを適用することで、逆方向バイアスを印加する場合の破壊を防ぐ。以上より、整流回路の信頼性を高め、且つ、整流効率の向上した整流回路の提供を課題とする。

【解決手段】酸化物半導体をチャネル形成領域に用い、室温において、ソース−ドレイン電圧が3.1[V]のときにオフ電流が10−20[A/μm]=10[zA/μm](z:ゼプト)以下であるトランジスタのゲートとドレインを共通に結線し、整流回路の交流信号が入力される端子に接続する。

(もっと読む)

141 - 160 / 820

[ Back to top ]