Fターム[5F110QQ23]の内容

薄膜トランジスタ (412,022) | 製造工程一般 (15,099) | ダングリングボンドの終端化(例;水素化) (1,179) | 拡散 (1,072) | 固相拡散 (454)

Fターム[5F110QQ23]に分類される特許

1 - 20 / 454

半導体装置

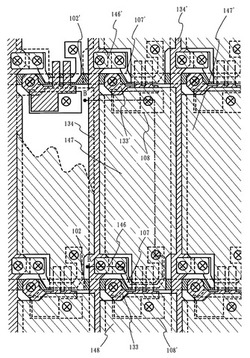

【課題】画素部に形成される画素電極や走査線(ゲート線)及びデータ線の配置を適したものとして、かつ、マスク数及び工程数を増加させることなく高い開口率を実現した画素構造を有するアクティブマトリクス型表示装置を提供する。

【解決手段】半導体膜107と基板との間に第1の絶縁膜を介して設けられた第1の配線102を、半導体膜107と重ねて設け、遮光膜として用いる。さらに半導体膜上にゲート絶縁膜として用いる第2の絶縁膜を形成し、第2の絶縁膜上にゲート電極と第2の配線134を形成する。第1及び第2の配線は、第1及び第2の絶縁膜を介して交差する。第2の配線134の上層には、層間絶縁膜として第3の絶縁膜を形成し、その上に画素電極147を形成する。画素電極147は、第1の配線及び第2の配線とオーバーラップさせて形成することが可能であり、反射型の表示装置において画素電極147の面積を大型化できる。

(もっと読む)

半導体記憶装置

【課題】半導体記憶装置において誤動作が生じる蓋然性を低減する。

【解決手段】積層配置されるメモリセルアレイ(例えば、酸化物半導体材料を用いて構成されているトランジスタを含むメモリセルアレイ)と周辺回路(例えば、半導体基板を用いて構成されているトランジスタを含む周辺回路)の間に遮蔽層を配置する。これにより、当該メモリセルアレイと当該周辺回路の間に生じる放射ノイズを遮蔽することが可能となる。よって、半導体記憶装置において誤動作が生じる蓋然性を低減することが可能となる。

(もっと読む)

半導体装置

【課題】無線通信により交信可能な半導体装置において、個体識別子を容易に付けることができるようにする。

【解決手段】薄膜トランジスタ119と、薄膜トランジスタ上に第1の層間絶縁膜156と、第1の層間絶縁膜上の、ソース領域またはドレイン領域の一方に電気的に接続される第1の電極114と、ソース領域またはドレイン領域の他方に電気的に接続される第2の電極110と、第1の層間絶縁膜、第1の電極、及び第2の電極上に形成された第2の層間絶縁膜135と、第2の層間絶縁膜上の、第1の電極または第2の電極の一方に電気的に接続される第1の配線177と、第2の層間絶縁膜上の、第1の電極または第2の電極の他方に電気的に接続されない第2の配線178とを有し、第2の配線と前記第1の電極または第2の電極の他方は、第2の層間絶縁膜中の分断領域169によって、電気的に接続されない半導体装置及びその作製方法に関するものである。

(もっと読む)

半導体装置

【課題】無線通信により交信可能な半導体装置において、個体識別子を容易に付けることができるようにする。また信頼性の高い半導体装置を提供する。

【解決手段】チャネル形成領域と、ソース領域またはドレイン領域を有する島状半導体膜131と、ゲート絶縁膜と、ゲート電極103とを有する薄膜トランジスタと、層間絶縁膜と、層間絶縁膜中に形成され、ソース領域またはドレイン領域の一方に達する複数のコンタクトホールを含む第1のコンタクトホール142と、ソース領域またはドレイン領域の他方に達する第2のコンタクトホール141とを有し、第2のコンタクトホール141の径は、第1のコンタクトホール142に含まれる複数のコンタクトホール142のそれぞれの径より大きく、第1のコンタクトホールの底面積の合計と、第2のコンタクトホール141の底面積は等しい半導体装置に関する。

(もっと読む)

表示装置

【課題】発光素子の劣化を極力抑えるための構造を提供すると共に、各画素に必要とされ

る容量素子(コンデンサ)を十分に確保するための構造を提供する。

【解決手段】トランジスタ上に、第1パッシベーション膜、第2の金属層、平坦化膜、バ

リア膜及び第3の金属層の順に積層され、平坦化膜に設けられた第1開口部の側面がバリ

ア膜に覆われ、第1開口部の内側に第2開口部を有し、かつ、第3の金属層は前記第1開

口部及び第2開口部を介して前記半導体に接続され、トランジスタの半導体、ゲート絶縁

膜、ゲート電極、第1パッシベーション膜及び前記第2の金属層で積層形成された容量素

子を備えたことを特徴とする。

(もっと読む)

半導体装置

【課題】液晶の配向不良を抑制するために画素電極を平坦化し、開口率を下げずに十分な

容量を得られる容量素子を有する半導体装置を実現することを課題とする。

【解決手段】薄膜トランジスタ上の遮光膜、前記遮光膜上の容量絶縁膜、前記容量絶縁膜

上に導電層、前記導電層と電気的に接続するように画素電極を有する半導体装置であり、

前記遮光膜、前記容量絶縁膜および前記導電層から保持容量素子を形成することにより、

容量素子として機能する領域の面積を増やすことができる。

(もっと読む)

集積回路装置の作製方法

【課題】薄膜回路の下方に外部と接続するための電極を容易に形成できる薄膜回路部品の

構造及び薄膜回路部品の作製方法を提供することを課題とする。

【解決手段】第1の絶縁膜と、第1の絶縁膜の一方の面上に形成された薄膜回路と、薄膜

回路上に形成された第2の絶縁膜と、第2の絶縁膜上に形成された電極と、電極上に形成

された樹脂膜とを有する積層物を形成し、積層物の第1の絶縁膜の他方の面側に、電極と

重なるように導電膜を形成し、導電膜にレーザーを照射する。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】結晶性の高い酸化物半導体をチャネル層に用いて、優れた特性を有する半導体装置を提供することを課題の一つとする。また、下地膜の平坦性を向上させた半導体装置を提供する。

【解決手段】トランジスタの下地膜に化学機械研磨処理を行い、化学機械研磨処理した後、プラズマ処理を行うことで、下地膜の中心線平均粗さRa75値を、0.1nm未満とすることができる。プラズマ処理及び化学機械研磨処理の組み合わせにより得られた平坦性を有する下地膜上に結晶性の高い酸化物半導体層を形成することで、半導体装置の特性向上を図る。

(もっと読む)

半導体装置

【課題】半導体装置において生じるTFTのバラツキを低減する。

【解決手段】トランジスタと、第1のソース配線と、隣り合う第2のソース配線と、電源供給線とを有し、第1のソース配線は、トランジスタと電気的に接続することができ、記トランジスタは、チャネル形成領域を有し、チャネル形成領域は、電源供給線と重なる領域を有し、チャネル形成領域は、第2のソース配線と重なる領域を有し、電源供給線は、第2のソース配線と重ならない半導体装置である。その結果、チャネル長Lに対するチャネル幅Wの比が0.1〜0.01であるTFTを提供することができ、各TFT間のバラツキを低減することができる。さらに、電源供給線は第1のソース配線よりも幅の広い領域を有し、電源供給線は、第2のソース配線よりも幅の広い領域を有する。

(もっと読む)

半導体基板の再生方法、再生半導体基板の作製方法、及びSOI基板の作製方法

【課題】半導体基板の再生に適した方法を提供する。

【解決手段】損傷半導体領域と絶縁層とを含む凸部が周縁部に存在する半導体基板に対し、絶縁層を除去するエッチング処理と、硝酸、硝酸によって酸化された半導体基板を構成する半導体材料を溶解する物質、半導体材料の酸化速度及び酸化された半導体材料の溶解速度を制御する物質、及び亜硝酸を含み、亜硝酸の濃度が10mg/l以上1000mg/l以下である混合液を用いて、未損傷の半導体領域に対して損傷半導体領域を選択的に除去するエッチング処理と、を行うことで半導体基板を再生する。

(もっと読む)

半導体装置の作製方法

【課題】本発明の一態様は、酸化物半導体を用いたデバイスにおいて高い移動度を達成し

、信頼性の高い表示装置を提供する。

【解決手段】表面と略垂直な方向にc軸が配向する結晶領域を有する酸化物半導体層を形

成し、酸化物半導体層上に接する酸化物絶縁層を形成し、第3の加熱処理を行うことによ

り、酸化物半導体層に酸素を供給し、酸化物絶縁層上に、水素を含む窒化物絶縁層を形成

し、第4の加熱処理を行うことにより、少なくとも酸化物半導体層と酸化物絶縁層の界面

に水素を供給する。

(もっと読む)

半導体装置

【課題】プロセス技術が比較的簡単、且つ、少ない素子数で多値情報を記憶することがでるメモリを提供する。

【解決手段】メモリ素子426において、第1の記憶素子における第1の電極417の形状の一部を、第2の記憶素子における第1の電極417の形状と異ならせることで、第1の電極417と第2の電極420の間の電気抵抗が変化する電圧値を異ならせて、1ビットを越える多値の情報の記憶を一つのメモリセルで行う。第1の電極417を部分的に加工することで単位面積当たりの記憶容量を増大することができる。

(もっと読む)

半導体装置

【課題】半導体膜と電極又は配線との接触抵抗を低減し、かつ半導体膜と電極又は配線と

の被覆率を改善し、特性を向上させた半導体装置を得ることを課題とする。

【解決手段】基板上にゲート電極と、前記ゲート電極上にゲート絶縁膜と、前記ゲート絶

縁膜上に第1のソース電極又はドレイン電極と、前記第1のソース電極又はドレイン電極

上に島状半導体膜と、前記島状半導体膜及び前記第1のソース電極又はドレイン電極上に

第2のソース電極又はドレイン電極とを有し、前記第2のソース電極又はドレイン電極は

前記第1のソース電極又はドレイン電極と接触しており、前記第1のソース電極又はドレ

イン電極及び第2のソース電極又はドレイン電極が前記島状半導体膜を挟みこんでいる半

導体装置及びその作製方法に関するものである。

(もっと読む)

半導体装置及び発光装置

【課題】側壁スペーサを形成することなく、且つ、工程数を増やすことなく、自己整合的にLDD領域を少なくとも一つ備えたTFTを提供する。また、同一基板上に、工程数を増やすことなく、様々なTFT、例えば、チャネル形成領域の片側にLDD領域を有するTFTと、チャネル形成領域の両側にLDD領域を有するTFTとを形成する作製方法を提供する。

【解決手段】回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターンを設置したフォトマスクまたはレチクルをゲート電極形成用のフォトリソグラフィ工程に適用して膜厚の厚い領域と、該領域より膜厚の薄い領域を片側側部に有する非対称のレジストパターンを形成し、段差を有するゲート電極を形成し、ゲート電極の膜厚の薄い領域を通過させて前記半導体層に不純物元素を注入して、自己整合的にLDD領域を形成す

る。

(もっと読む)

プログラマブルロジックデバイス

【課題】電源電圧の供給を停止しても論理回路の結線状態を保持可能なプログラマブルロジックデバイスにおける処理速度の向上及び低消費電力化を図ることを目的の一とする。

【解決手段】論理状態を切り替え可能な複数の演算回路と、演算回路の論理状態を切り替えるコンフィグレーション状態切り替え回路と、演算回路の電源電圧の供給または停止を切り替える電源制御回路と、複数の演算回路の論理状態及び電源電圧の状態を記憶する状態記憶回路と、状態記憶回路の記憶情報に応じて、コンフィグレーション状態切り替え回路及び電源制御回路の制御を行う演算状態制御回路と、を有し、演算回路とコンフィグレーション状態切り替え回路との間に、酸化物半導体層にチャネル形成領域が形成されるトランジスタが設け、電源制御回路からの電源電圧の停止時に該トランジスタの導通状態を保持する。

(もっと読む)

半導体装置

【課題】電源電位の供給が遮断されたときでもデータの保持が可能で、且つ、低消費電力化が可能なプログラマブルなアナログデバイスを提供する。

【解決手段】アナログ素子を含むユニットセルを複数並列に接続されたプログラマブル回路とし、ユニットセル毎に導通または非導通の切り替えを行う。また、当該ユニットセルのスイッチとして、オフ電流を十分に小さくすることができる第1のトランジスタと、ゲート電極が第1のトランジスタのソース電極又はドレイン電極と電気的に接続された第2のトランジスタと、を含む構成とし、当該第2のトランジスタのゲート電位によってユニットセルの導通または非導通を制御する。

(もっと読む)

記憶装置及び信号処理回路

【課題】電源の供給を停止しても、記憶している論理状態が消えない記憶装置を提供する。また、該記憶装置を用いることで、電源供給停止により消費電力を抑えることができる信号処理回路を提供する。

【解決手段】第1乃至第4のノードを有する論理回路と、第1のノード、第2のノード、及び第3のノードと接続された第1の制御回路と、第1のノード、第2のノード、及び第4のノードと接続された第2の制御回路と、第1のノード、第1の制御回路、及び第2の制御回路に接続された第1の記憶回路と、第2のノード、第1の制御回路、及び第2の制御回路に接続された第2の記憶回路と、を有する記憶装置である。

(もっと読む)

半導体装置

【課題】高速動作が可能であり、且つ消費電力を低減することが可能な半導体装置を提供する。

【解決手段】レベルシフタ、第1のバッファ、及び第2のバッファと、第1のスイッチ及び第2のスイッチと、第1の端子、第1の端子から入力される信号の反転信号が入力される第2の端子、及び第1のスイッチ及び第2のスイッチの状態を制御するクロック信号が入力される第3の端子と、を備えるラッチ回路を有する。レベルシフタの第1の出力端子は、第1のスイッチを介して、第1のバッファ及び第2のバッファそれぞれの一の入力端子と接続し、レベルシフタの第2の出力端子は、第2のスイッチを介して、第1のバッファ及び第2のバッファそれぞれの他の入力端子と接続する。レベルシフタの第1の入力端子は、第1のバッファの出力端子と接続し、レベルシフタの第2の入力端子は、第2のバッファの出力端子と接続する。

(もっと読む)

半導体装置

【課題】チャネル形成領域の空乏化領域を増やし、電流駆動能力の高い半導体装置を提供する。

【解決手段】島状の半導体領域308と、前記島状の半導体領域308の側面及び上面を覆って設けられたゲート絶縁膜310と、前記ゲート絶縁膜310を介して前記島状の半導体領域308の前記側面及び前記上面を覆って設けられたゲート電極とを有し、前記島状の半導体領域308の前記側面及び前記上面はチャネル形成領域として機能する半導体装置である。

(もっと読む)

半導体装置の作製方法

【課題】基板の大面積化を可能とするとともに、特性の改善された酸化物半導体層を形成し、所望の高い電界効果移動度を有するトランジスタを製造可能とし、大型の表示装置や高性能の半導体装置等の実用化を図ることを課題の一つとする。

【解決手段】絶縁表面を有する基板上にゲート電極層を形成し、ゲート電極層上にゲート絶縁層を形成し、ゲート絶縁層上に酸化物半導体層を形成し、酸化物半導体層上にソース電極層及びドレイン電極層を形成し、酸化物半導体層、ソース電極層、及びドレイン電極層上に酸素を含む絶縁層を形成し、酸素を含む絶縁層上に水素を含む絶縁層を形成した後、熱処理を行うことにより、水素を含む絶縁層中の水素を少なくとも酸化物半導体層に供給することを特徴とする半導体装置の作製方法である。

(もっと読む)

1 - 20 / 454

[ Back to top ]