Fターム[5F140AA10]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 目的 (9,335) | ソース、ドレイン電極部の低抵抗化 (348)

Fターム[5F140AA10]に分類される特許

1 - 20 / 348

半導体装置の製造方法

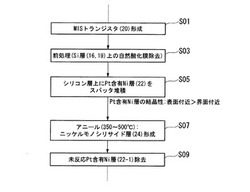

【課題】本発明は、シリコン層上に、抵抗値が低く、かつ平坦性の良好なニッケルモノシリサイド層を形成可能な半導体装置の製造方法を提供することを課題とする。

【解決手段】基板に形成されたシリコン層を覆ように白金を含むニッケル層を堆積する工程であって、シリコン層に近い部分では遠い部分と比較して結晶性が低くなるように、白金を含むニッケル層を堆積する工程S05と、基板を加熱することで、シリコン層と白金を含むニッケル層との界面にニッケルモノシリサイド層を形成する工程S07と、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】FinFETの隣接するフィン同士のショートを回避しつつ、エピタキシャル層の表面積を広く確保する。

【解決手段】実施形態によれば、半導体装置は、半導体基板と、前記半導体基板の表面に形成され、(110)面である側面を有するフィンとを備える。さらに、前記装置は、前記フィンの側面に形成されたゲート絶縁膜と、前記フィンの側面および上面に、前記ゲート絶縁膜を介して形成されたゲート電極とを備える。さらに、前記装置は、前記フィンの側面に、フィン高さ方向に沿って順に形成された複数のエピタキシャル層を備える。

(もっと読む)

グラフェンを含む電極構造体及び電界効果トランジスタ

【課題】グラフェンを含む電極構造体及び電界効果トランジスタを提供する。

【解決手段】半導体層上のグラフェンと、グラフェン上の電極メタルと、を備え、該グラフェンは、半導体層と直接的に接触し、電極メタルは、グラフェンと直接的に接触する電極構造体である。半導体層は、シリコン、ゲルマニウム、シリコン・ゲルマニウム、III−V族半導体、及びII−VI族半導体を含むグループから選択された一つで形成される。グラフェンは、単層または二層のグラフェンで形成される。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 寄生抵抗を低減可能な半導体装置を提供する。

【解決手段】 半導体装置は、第1半導体層の表面に沿って延びる突起(2)を有する第1半導体層(1)を含む。ゲート電極(12)は、突起の表面をゲート絶縁膜を挟んで覆う。第2半導体層(28, 45)は、突起のゲート電極により覆われる部分と別の部分の側面上に形成され、溝(31, 52)を有する。ソース/ドレイン領域(30, 46)は、第2半導体層内に形成される。シリサイド膜(33)は、溝内の表面を含め第2半導体層の表面を覆う。導電性のプラグ(37)は、シリサイド膜と接する。

(もっと読む)

半導体装置およびその製造方法

【課題】ショットキー障壁の高さおよび幅を容易に制御すると共に寄生抵抗が低く、且つ短チャネル効果を効果的に抑制する。

【解決手段】金属ソース・ドレイン電極(ニッケルシリサイド)6とP型シリコン基板1との間に、セシウム含有領域5を形成している。こうして、金属ソース・ドレイン電極6近傍のセシウムをイオン化して正孔に対するエネルギー障壁高さを大きくし、金属ソース・ドレイン電極6とP型シリコン基板1との間のリーク電流を著しく低減する。また、チャネルと金属ソース・ドレイン電極6との間のショットキー障壁の高さおよび幅を実効的に小さくして寄生抵抗を著しく低減する。したがって、金属シリサイドの厚み(深さ)をイオン注入による制約なしに決定でき、極めて浅いソース・ドレインを形成して良好な短チャネル効果特性を得ることができる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】フィンがバルク基板上に形成されたフィン型トランジスタにおいて、ソース/ドレインボトム領域での接合リーク電流の増大を抑制しつつ、ソース/ドレインとソース/ドレイン上に形成されたシリサイドとの接触抵抗を低減する。

【解決手段】フィン型半導体3の両端部に形成した高濃度不純物拡散層10からなるソース/ドレインの側面に、フィン型半導体3の上部の表面が露出するようにしてオフセットスペーサ7およびサイドウォールスペーサ8を形成し、フィン型半導体3の上部の高濃度不純物拡散層10の表面には、シリサイド層9を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】仕事関数の異なる複数の電極層を有し、ゲート抵抗が低く、作製が容易なゲート電極を備える半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置は、基板と、前記基板上に形成されたゲート絶縁膜とを備える。さらに、前記装置は、前記ゲート絶縁膜の上面に形成され、第1の仕事関数を有する第1の電極層と、前記ゲート絶縁膜の上面と前記第1の電極層の上面に連続して形成され、前記第1の仕事関数と異なる第2の仕事関数を有する第2の電極層と、を有するゲート電極と、前記ゲート電極の側面に形成された側壁絶縁膜とを備える。さらに、前記装置では、前記第1の電極層の上面の高さは、前記側壁絶縁膜の上面の高さよりも低い。

(もっと読む)

電界効果トランジスタ

【課題】チャネルへの電子供給能力が改善されたIII−V族FETを提供する。

【解決手段】基板2の上には、ナローバンドギャップ材料のチャネル層4が形成される。チャネル層4の上のソース領域には、ワイドバンドギャップ材料のコンタクト層6が形成される。ソースコンタクト層6は、1×1019cm−3以上の濃度でドーピングされる。FET1は、ソースコンタクト層6によってアンドープのチャネル層4に直接キャリアが注入されるように構成される。

(もっと読む)

半導体装置

【課題】長さ方向がゲート長方向と平行なトレンチに形成されたゲート電極を有し、単位平面積当たり大きなゲート幅を有する高駆動能力横型のMOSトランジスタの駆動能力を、平面的な素子面積を増加させずに向上させる半導体装置を提供する。

【解決手段】半導体基板の表面に長さ方向がゲート長方向と平行なトレンチが形成された第1トレンチ領域013と、前記第1トレンチ領域の凹部底面と同一平面に前記第1トレンチ領域の長さ方向の両端に接して設けられた第2トレンチ領域014および第3トレンチ領域015と、トレンチ領域に形成された第2導電型のウェル領域005と、前記第1トレンチ領域に設けられたゲート絶縁膜004と、前記ゲート絶縁膜上に接して設けられたゲート電極003と、前記第1トレンチと前記第2トレンチ領域と前記第3トレンチ領域に前記ウェル領域より浅く設けられた第1導電型のソース領域とドレイン領域を有する半導体装置。

(もっと読む)

HEMT装置を製造するCMOSコンパチブルな方法とそのHEMT装置

【課題】Si−CMOSプロセス時術とコンパチブルなHEMT装置の製造法を提供する。

【解決手段】基板101を提供するステップと、III族窒化物層のスタックを基板上に形成するステップと、窒化シリコンからなり、スタックの上方層に対して上に位置すると共に当接する第1パッシベーション層301を形成し、第1パッシベーション層が、現場でスタックに堆積されるステップと、第1パッシベーション層に対して上に位置すると共に当接する誘電体層を形成するステップと、窒化シリコンからなり、誘電体層に対して上に位置すると共に当接する第2パッシベーション層303を形成し、第2パッシベーション層が、LPCVD、MOCVD又は同等の手法によって450℃より高い温度で堆積されるステップと、ソースドレイン・オーミック接触とゲート電極601を形成するステップとを備える。

(もっと読む)

半導体装置、金属膜の製造方法及び半導体装置の製造方法

【課題】高集積化することができる半導体装置、金属膜の製造方法及び半導体装置の製造方法を提供することである。

【解決手段】実施形態に係る半導体装置は、半導体基板と、前記半導体基板に形成され、ヒ素を含むヒ素拡散層と、前記ヒ素拡散層上に形成された金属膜と、を備える。前記金属膜は、タングステン、チタン、ルテニウム、ハフニウム及びタンタルからなる群より選択された少なくとも1種の金属、並びにヒ素を含む。

(もっと読む)

半導体装置の製造方法

【課題】王水を用いることなくニッケルプラチナ膜の未反応部分を選択的に除去しうるとともに、プラチナの残滓が半導体基板上に付着するのを防止しうる半導体装置の製造方法を提供する。

【解決手段】シリコン基板10上に、ゲート電極16と、ゲート電極16の両側のシリコン基板10内に形成されたソース/ドレイン拡散層24とを有するMOSトランジスタ26を形成し、シリコン基板10上に、ゲート電極16及びソース/ドレイン拡散層24を覆うようにNiPt膜28を形成し、熱処理を行うことにより、NiPt膜28とソース/ドレイン拡散層24の上部とを反応させ、ソース/ドレイン拡散層24上に、Ni(Pt)Si膜34a、34bを形成し、過酸化水素を含む71℃以上の薬液を用いて、NiPt膜28のうちの未反応の部分を選択的に除去するとともに、Ni(Pt)Si膜34a、34bの表面に酸化膜を形成する。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】シリサイド層を有するトランジスタにおいて、オン電流の高いトランジスタを得ることを課題とする。さらに、加熱処理等の工程を増やさずにオン電流の高いトランジスタを得ることを課題とする。

【解決手段】チャネル形成領域、不純物領域及びシリサイド層を有するシリコン膜と、ゲート絶縁膜と、ゲート電極と、不純物領域にシリサイド層を介して電気的に接続する配線とを有し、シリサイド層断面は、チャネル形成領域側の端点から膜厚が増加している第1領域と、第1領域と比べて膜厚が一定である第2領域とを有する半導体装置において、第1領域と第2領域は、シリサイド層断面の端点を通り、水平線とθ(0°<θ<45°)の角度をなす直線がシリサイド層と不純物領域の界面と交わる点を通り、且つ水平線に対し垂直な線で分けられ、シリコン膜の膜厚に対する第2領域の膜厚比は0.6以上である。

(もっと読む)

半導体装置の製造方法

【課題】王水を用いることなくニッケルプラチナ膜の未反応部分を選択的に除去しうるとともに、プラチナの残滓が半導体基板上に付着するのを防止しうる半導体装置の製造方法を提供する。

【解決手段】シリコン基板10上に、ゲート電極16と、ゲート電極16の両側のシリコン基板10内に形成されたソース/ドレイン拡散層24とを有するMOSトランジスタ26を形成し、シリコン基板10上に、ゲート電極16及びソース/ドレイン拡散層24を覆うようにNiPt膜28を形成し、熱処理を行うことにより、NiPt膜28とソース/ドレイン拡散層24の上部とを反応させ、ソース/ドレイン拡散層24上に、Ni(Pt)Si膜34a、34bを形成し、過酸化水素を含む71℃以上の薬液を用いて、NiPt膜28のうちの未反応の部分を選択的に除去するとともに、Ni(Pt)Si膜34a、34bの表面に酸化膜を形成する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の信頼性を向上させる。

【解決手段】ゲート電極GE1,GE2、ソース・ドレイン用のn+型半導体領域SD1及びp+型半導体領域SD2を形成してから、半導体基板1上にNi−Pt合金膜を形成し、第1の熱処理を行って合金膜とゲート電極GE1,GE2、n+型半導体領域SD1及びp+型半導体領域SD2とを反応させることで、(Ni1−yPty)2Si相の金属シリサイド層13aを形成する。この際、Niの拡散係数よりもPtの拡散係数の方が大きくなる熱処理温度で、かつ、金属シリサイド層13a上に合金膜の未反応部分が残存するように、第1の熱処理を行う。その後、未反応の合金膜を除去してから、第2の熱処理を行って金属シリサイド層13aを更に反応させることで、Ni1−yPtySi相の金属シリサイド層13bを形成する。第2の熱処理の熱処理温度は580℃以上で、800℃以下とする。

(もっと読む)

半導体装置及びその製造方法

【課題】配線抵抗を低減することのできる半導体装置を提供する。

【解決手段】一の実施の形態に係る半導体装置は、半導体基板と、半導体基板上にそれぞれ設けられた第1の領域及び第2の領域とを備える。第1の領域は、半導体基板上の第1配線層に形成され、所定の第1の幅を有する第1の金属配線と、第1配線層の上層の第2配線層に形成され第1の幅を有する第2の金属配線と、第1の金属配線と第2の金属配線とを接続し、第1の幅以下の第2の幅を有する第1のコンタクトとを有する。第2の領域は、第1配線層から第2配線層へと亘る膜厚を有し、所定の第3の幅を有する第3の金属配線を有する。

(もっと読む)

自己整合シリサイドの形成方法、半導体デバイスの製造方法、および半導体構造物

【課題】製造工程の増大を抑制し、コンタクト抵抗および界面抵抗の増大を防止する。

【解決手段】実施形態において、シリコン層は、ゲートラストスキームを用いた機能的ゲート電極の製造後に、形成される。初期的な半導体構造物は、半導体基板上に形成された少なくとも一つの不純物領域、不純物領域の上に形成された犠牲膜、犠牲膜の上に形成された絶縁層、絶縁層の上に形成された絶縁層を備える。ビアは、初期の半導体構造物の絶縁層へ、および、コンタクト開口部が絶縁層に形成されるように絶縁層の厚さを通り抜けて、パターン化される。次に、絶縁層の下にある犠牲膜は、絶縁層の下に空隙を残して除去される。次に、金属シリサイド前駆体は、空隙スペースに配置され、金属シリサイド前駆体は、アニールプロセスを通じてシリサイド層に変換される。

(もっと読む)

半導体素子及び半導体素子の製造方法

【課題】3次元形の半導体素子において、オン抵抗をより効果的に低減できる半導体素子及び半導体素子の製造方法を提供する。

【解決手段】半導体素子は、ドレイン層と、ドレイン層内に選択的に設けられたドリフト領域と、ドリフト領域内に選択的に設けられたベース領域と、ベース領域内に選択的に設けられたソース領域と、ソース領域又はドレイン層の少なくとも一方の内部に、ソース領域又はドレイン層の少なくとも一方に選択的に設けられた第1,第2の金属層と、ドレイン層の表面に対して略平行な方向に、ソース領域の一部から、ソース領域の少なくとも一部に隣接するベース領域を貫通して、ドリフト領域の一部にまで到達するトレンチ状のゲート電極と、第1の金属層に接続されたソース電極と、ドレイン層又は第2の金属層に接続されたドレイン電極と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】携帯電話などのフロントエンドモジュールに使用されているハイパワーアンプは、シリコン系CMOS集積回路をベースとするデバイスであるが、その出力段に多数のLDMOSFETセルを集積し、通常、複数のLDMOSFETを構成したLDMOSFET部を有する。このLDMOSFETセルにおいては、裏面のソース電極と表面のソース領域との間の抵抗を低減するために、半導体基板に高濃度にボロンドープされたポリシリコンプラグが埋め込まれている。このポリシリコンプラグは、熱処理に起因する固相エピタキシャル成長により収縮し、シリコン基板に歪が発生する。

【解決手段】本願発明は、LDMOSFET等の半導体装置の製造方法において、基板の表面からエピタキシャル層を貫通するホールを形成し、ポリシリコンプラグを埋め込むに際して、ホールの内面に薄膜酸化シリコン膜が存在する状態で、ポリシリコン部材の堆積を行うものである。

(もっと読む)

半導体装置の製造方法

【課題】注入した不純物の拡散を抑制しつつ結晶欠陥を低減する半導体装置の製造方法を提供する。

【解決手段】実施の形態の半導体装置の製造方法は、リンまたはボロンを分子状イオンの形態で含有する第1の不純物80と、リンまたはボロンよりも注入量が少ない炭素、フッ素または窒素を分子状イオンの形態で含有する、もしくは、リンまたはボロンよりも注入量が少ない炭素を原子イオンの形態で含有する第2の不純物81と、を半導体層1に注入して不純物注入層9を形成する工程を含む。

(もっと読む)

1 - 20 / 348

[ Back to top ]