Fターム[5F140AC01]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 動作、用途、素子構造 (4,642) | Pchトランジスタ (555)

Fターム[5F140AC01]に分類される特許

541 - 555 / 555

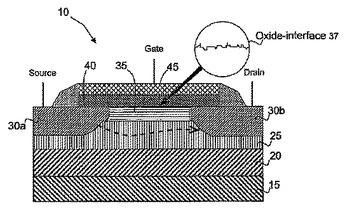

半導体装置の製造方法

【課題】p型トランジスタの動作速度を高め、n型トランジスタとの動作速度の均衡がとれた半導体装置の製造方法を提供する。

【解決手段】p−MOS領域30aのソース/ドレイン領域にSiGe膜からなる圧縮応力印加部20を形成し、その後にp−MOS領域30aおよびn−MOS領域30bに不純物注入を行い、浅い接合領域22a、22bおよび深い接合領域23a、23bを形成する。SiGe膜を形成する際の加熱により浅い接合領域22a、22bの不純物がゲート絶縁膜15の直下に拡散することを防止し、短チャネル効果を防止すると共に、p−MOSトランジスタ13aのチャネル領域の正孔移動度を高め、n−MOSトランジスタ13bの動作速度との均衡により、相補型の半導体装置10の総合的な動作速度を高める。

(もっと読む)

半導体装置とその製造方法、及び半導体装置の評価方法

【課題】 チャネルに応力が印加されるMOSトランジスタの特性のばらつきを防ぐことができる半導体装置とその製造方法を提供すること、及び、MOSトランジスタのチャネルにおけるキャリア分布を直接測定することができる半導体装置の評価方法を提供すること。

【解決手段】 シリコン(半導体)基板10と、シリコン基板10の上に順に形成されたゲート絶縁膜13及びゲート電極14cと、ゲート電極14cの横のシリコン基板10のリセス(穴)10a、10bに形成されたソース/ドレイン材料層18a、18bと、を有し、リセス10a、10bのゲート電極14c寄りの側面10c、10dが、シリコン基板10の少なくとも一つの結晶面で構成されることを特徴とする半導体装置による。

(もっと読む)

半導体装置の製造方法

【課題】 不純物のプロファイルを精度よく制御することが可能な半導体装置の製造方法を提供する。

【解決手段】 半導体領域1に不純物元素のイオンを注入する工程と、半導体領域に、所定元素としてIV族の元素又は不純物元素と同一導電型であって不純物元素よりも質量数が大きい元素のイオンを注入してアモルファス状態の結晶欠陥領域5を形成する工程と、不純物元素及び所定元素が注入された領域にフラッシュランプの光を照射してアニールを行い、アモルファス状態の結晶欠陥領域の結晶欠陥を回復させるとともに不純物元素を活性化する工程と、を備え、フラッシュランプの光を照射してアニールを行う工程を、結晶欠陥領域のアモルファス状態が維持される温度で半導体領域を予め加熱した状態で行う。

(もっと読む)

半導体装置およびその製造方法

【課題】 半導体装置の性能や信頼性を向上させる。

【解決手段】 CMISFETを有する半導体装置において、nチャネル型MISFET30aのゲート電極31aは、P、AsまたはSbをドープしたシリコン膜をNi膜と反応させることで形成されたニッケルシリサイド膜からなり、pチャネル型MISFET30bのゲート電極31bは、ノンドープのシリコンゲルマニウム膜をNi膜と反応させることで形成されたニッケルシリコンゲルマニウム膜からなる。ゲート電極31aの仕事関数はP、AsまたはSbをドープすることによって制御され、ゲート電極31bの仕事関数はGe濃度を調節することによって制御される。

(もっと読む)

半導体装置の製造方法

【課題】 熱処理を最小限に抑えることにより、高誘電率ゲート絶縁膜の結晶化を防止する。

【解決手段】 シリコン基板1上にHfAlOx膜5とポリシリコンゲルマニウム膜6を積層する。ポリシリコンゲルマニウム膜6にボロンイオン7を注入した後、パターニングしてゲート電極6aを形成する。ゲート電極6aをマスクとしてエクステンション領域形成用のボロンイオン9を注入した後、ゲート電極6a側壁にサイドウォール12を形成する。サイドウォール12及びゲート電極6aをマスクとしてソース/ドレイン領域形成用のボロンイオン13を注入する。熱処理を行うことにより、ゲート電極6aにおいてボロンイオン7を拡散させると共に、基板1においてボロンイオン9,13を活性化させてエクステンション領域10a及びソース/ドレイン領域14aを形成する。

(もっと読む)

半導体デバイスを製造する方法およびそのような方法で得られる半導体デバイス

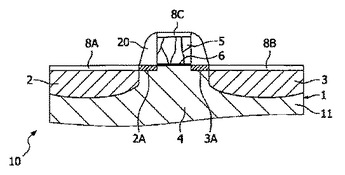

本発明は、半導体デバイス(10)を製造する方法であって、シリコンの半導体本体(1)がその表面に第1導電型の半導体領域(4)を備え、その領域に、第1導電型とは逆の第2導電型の第2半導体領域(2A、3A)が、第2導電型のドーパント原子の半導体本体(1)への添加によって第1半導体領域(4)とのpn接合を形成して形成され、前記ドーパント原子の添加の前に、不活性原子のアモルファス化注入によってアモルファス領域が半導体本体(1)内に形成され、アモルファス化注入後、半導体本体(1)に暫定的ドーパント原子が注入され、第2導電型のドーパント原子の添加後、半導体本体が、それに約500℃から約800℃までの、好ましくは550℃から750℃までの範囲の温度での熱処理を加えることによって、アニールされる方法に関する。第2導電型のドーパント原子はイオン注入によって半導体本体(1)に添加される。このようにして、非常に浅く、熱的に安定で、急峻で、低オーミックであるMOSFETのソースおよびドレイン拡張部(2A、3A)を形成するのに非常に適しているpn接合が形成される。  (もっと読む)

(もっと読む)

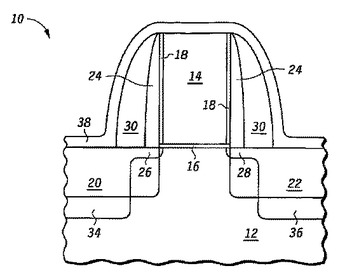

高電圧PMOSトランジスタ

アイソレーションされたゲート電極(18)と、n形導電ウェル(11)内のp形導電ソース領域(15)と、n形ウェル内に配置されているp形導電ウェル(12)内のp形導電ドレイン領域(14)と、ゲート電極とドレイン領域との間のフィールド酸化物領域(13)とを備えている高電圧PMOSトランジスタにおいて、ドレイン領域(14)の下方のn形導電ウェルの深さ(A′−B′)はソース領域(15)の下方のn形導電ウェルの深さより僅かでありかつp形導電ウェルの深さ(A′−C′)はドレイン領域(14)の下方において最大である。  (もっと読む)

(もっと読む)

半導体装置の製造方法

濃度1から10%のSiH3CH3をH2により希釈し、希釈したSiH3CH3の一部と、GeH4と、SiH4(またはDCS)とをそれぞれ所定の流量でエピタキシャル装置のチャンバへ供給し、SiGe:Cをエピタキシャル成長技術により形成する。SiH3CH3を希釈することにより、SiH3CH3に含まれる酸素系不純物の濃度が低減するので、チャンバへ供給される酸素系不純物が低減して、成膜されるSiGe:Cに含まれる酸素系不純物の濃度が低減する。 (もっと読む)

pFET中のボロン拡散係数の減少方法

半導体材料の構造物または本体(例えば基板または層)によって定められる境界を横切って加えられる応力を受ける膜は、境界の近傍の半導体材料中に引張り応力から圧縮応力への変化を提供し、アニーリングの間のホウ素拡散速度を変化させ、ひいては最終ホウ素濃度またはプロフィル/勾配あるいはその両方を変化させるために用いられる。電界効果トランジスターの場合、側壁の有無にかかわらず、ソース/ドレイン、拡張注入部またはハロ注入部、あるいはその両方に対する境界の位置を調節するために、ゲート構造物を形成させることができる。水平方向と垂直方向とで異なるホウ素拡散速度を作り出すことができ、ヒ素と同程度の拡散速度を実現することができる。同じプロセス工程で、nFETとpFETとの両方の接合キャパシタンスの減少を同時に実現することができる。

(もっと読む)

(もっと読む)

ヘテロ構造を有した電界効果トランジスタ、およびその製造方法

本発明は、ヘテロ構造を有した電界効果トランジスタに関する。当該ヘテロ構造では、キャリア材料上に歪み単結晶半導体層(4)が形成されている。当該キャリア材料は、最上層として、第1の半導体材料(Si)からなる緩和単結晶半導体層(3)を備えている。上記緩和単結晶半導体層は半導体合金(GexSi1−x)を含んでいて、第2の半導体材料の比率xは自由に設定できる。さらに、上記歪み半導体層(4)上に、ゲート絶縁層(5)およびゲート層(6)が形成される。この場合、非ドープチャネル領域(K)を構成するために、少なくとも歪み半導体層(4)において、ドレイン/ソース領域(D、S)が上記ゲート層に対して横向きに形成される。Ge比率xを自由に設定できる可能性によって、閾値電圧を任意に設定でき、これによって最新の論理半導体部品を実現することができる。  (もっと読む)

(もっと読む)

固相エピタキシャル再成長を用いてドーピングプロファイルの深さを低減した半導体基板及び同半導体基板の生産方法

半導体デバイスの生産方法であって、a)半導体基板を準備し、b)半導体基板の最上面上に絶縁層を設け、c)適当な注入によって、前記半導体基板の最上層中にアモルファス層を作り、d)所定のドーピングプロファイルを伴う前記アモルファス層を作るための前記絶縁層を通して、前記半導体基板中へドーパントを、前記ドーピングプロファイルが前記絶縁層内に位置するピーク値を持つように注入し、e)前記アモルファス層を再成長させ、前記ドーパントを活性化する固相エピタキシャル再成長作用を適用することを含む半導体デバイスの生産方法。  (もっと読む)

(もっと読む)

シリサイドをソース/ドレインに用いた半導体素子

半導体素子において、非常に深い位置に達するゲルマニウムイオン注入及びゲルマニウムの活性化をニッケルシリサイド形成用のニッケルの堆積の前に行なう。ゲルマニウムを活性化させることにより、イオン注入領域の格子定数が、シリコンであることが好ましい母体基板の格子定数よりも大きくなる。このような変化が加えられた格子によって、ニッケルダイシリサイドの形成を防止することができるという効果が得られる。その結果、ニッケルシリサイドスパイクを防止することができる。  (もっと読む)

(もっと読む)

ストレインド・シリコン電圧制御発振器(VCO)

ストレインド・シリコン電圧制御発振器(VCO)は、ストレインド・シリコン層を有する第1Pチャネル金属酸化膜半導体(PMOS)装置を含み、ストレインド・シリコン層を有する第2PMOS装置に結合される。  (もっと読む)

(もっと読む)

格子不整合のソースおよびドレイン領域を有する歪み半導体CMOSトランジスタを有する集積回路および製作方法

【課題】 p型電界効果トランジスタ(PFET)およびn型電界効果トランジスタ(NFET)を有する集積回路を提供することにある。

【解決手段】 第1の歪みは、NFETではなくPFETのみのソースおよびドレイン領域内に配置されたシリコン・ゲルマニウムなどの格子不整合半導体層を介してNFETではなくPFETのチャネル領域に加えられる。PFETおよびNFETを形成するプロセスが提供される。PFETのソースおよびドレイン領域になるためのエリア内にトレンチがエッチングされ、それに隣接するPFETのチャネル領域に歪みを加えるために、格子不整合シリコン・ゲルマニウム層をそこにエピタキシャル成長させる。シリコン・ゲルマニウム層の上にシリコンの層を成長させ、シリコンの層からサリサイドを形成して、低抵抗ソースおよびドレイン領域を提供することができる。

(もっと読む)

半導体装置及びその製造方法

Si(100)基板の表面にシリコン酸化膜を形成した後、このシリコン酸化膜をプラズマ窒化して酸窒化シリコン膜にする。その後NOガス雰囲気中で770乃至970℃の温度条件下で熱処理することにより、ゲート絶縁膜における基板との界面部分の窒素濃度を1乃至10原子%にすると共に、基板と酸窒化シリコン膜との界面に存在する界面Si結合欠陥の結合手の方位角分布が、基板の[100]方位に対して25°以上の角度にピークをもつようにする。 (もっと読む)

541 - 555 / 555

[ Back to top ]