Fターム[5F140AC21]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 動作、用途、素子構造 (4,642) | 横型DMOS、DSA(二重拡散Tr) (541)

Fターム[5F140AC21]に分類される特許

1 - 20 / 541

半導体装置

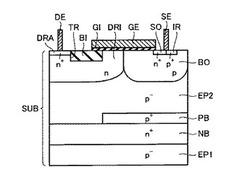

【課題】ハイサイド素子として用いても誤動作が少なく、かつオン耐圧およびオフ耐圧の双方を高く維持することのできる半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBの内部には、p-エピタキシャル領域EP1が、その主表面側にはp-エピタキシャル領域EP2が、その主表面側にはn型ドリフト領域DRIとp型ボディ領域BOとが形成されている。p-エピタキシャル領域EP1とp-エピタキシャル領域EP2との間には、これらの領域を電気的に分離するためにn+埋め込み領域NBが形成されている。n+埋め込み領域NBとp-エピタキシャル領域EP2との間には、p-エピタキシャル領域EP2よりも高いp型不純物濃度を有するp+埋め込み領域PBが形成されている。p+埋め込み領域PBは、n型ドリフト領域DRIとp型ボディ領域BOとの接合部の少なくとも直下に位置し、かつn型ドリフト領域DRIと接するドレイン領域DRAの直下を避けて配置されている。

(もっと読む)

基板貫通バイアを有する半導体構造および製造方法

【課題】基板を貫通するバイアホールを与える。

【解決手段】半導体デバイス構造は、第1の濃度および第1の導電型のバックグラウンドドーピングを有する基板を含んでなる。基板貫通バイアは基板を貫通している。デバイスは基板の第1の面上に第2の導電型の第1のドープ領域を有する。第2のドープ領域が基板貫通バイアの周りにある。第2のドープ領域は、第1の濃度よりも大きい第2の濃度にドーピングされており、第1の導電型を有する。

(もっと読む)

高耐圧MOSFETの回路シミュレーション用モデルの作成方法と装置並びにプログラム

【課題】高耐圧MOSFETのモデルにおいて、ドレイン電流の精度を広いバイアス範囲で得ることができ、シミュレーションの精度を向上させる。

【解決手段】ドレインが共通接続され、ゲートが共通接続され、バックゲートが共通接続され、ソース領域のソース拡散層の幅とウェルコンタクト拡散層の幅にそれぞれ対応した第1及び第2のチャネル幅を有する第1及び第2のMOSFET1、2と、第2のMOSFET2のソースに一端が接続された第1の可変抵抗素子3を備え、第2のMOSFET2のソースと第1の可変抵抗素子3の他端との接続点をソース端子Sとし、第1及び第2のMOSFETの共通接続したドレイン、共通接続したゲート、共通接続したバックゲートをそれぞれドレイン端子D、ゲート端子G、バックゲート端子Bとするモデルを作成し、モデリング対象の高耐圧MOSFETの電気特性データに基づき、第1の可変抵抗素子3の抵抗値を調整する。

(もっと読む)

半導体装置

【課題】 ゲート長方向に対し水平に複数本のトレンチを形成することにより単位面積当たりのゲート幅を増大させる高駆動能力横型MOSにおいて、素子面積を増加させずに更に駆動能力を向上させる。

【解決手段】 半導体基板表面から一定の深さに設けられた高抵抗第一導電型半導体のウェル領域と、前記ウェル領域の表面から途中の深さまで達する複数本のトレンチと、前記トレンチが形成する凹凸部の表面に設けられたゲート絶縁膜と、前記トレンチ内部に埋め込まれたゲート電極と前記トレンチ両端付近を除く前記凹凸部領域において前記トレンチ内部に埋め込まれたゲート電極と接触して基板表面に設けられたゲート電極膜と、前記ゲート電極膜と接触して前記トレンチ両端付近のトレンチ内部に半導体基板表面より深い位置に表面が位置するように埋め込まれたゲート電極膜と、前記ゲート電極膜と接触していない半導体面から前記ウェル領域の深さより浅く設けられた2つの低抵抗第二導電型半導体層であるソース領域とドレイン領域を有する半導体装置とした。

(もっと読む)

半導体装置およびその製造方法

【課題】スイッチング素子として利用される高耐圧かつ低オン抵抗な半導体装置を安価に提供する。

【解決手段】第1導電型の不純物を含有し、互いに対向する第1の主面と第2の主面とを有する半導体基板と、第2導電型の不純物を第1の濃度で含有し、前記半導体基板の前記第1の主面に露出するように形成された第1の拡散領域と、前記第2導電型の不純物を前記第1の濃度よりも高い第2の濃度で含有し、前記半導体基板の前記第1の主面に露出するように前記第1の拡散領域の側方に形成された第2の拡散領域と、前記第1導電型の不純物を含有し、前記半導体基板の前記第1の主面に露出するように前記第1の拡散領域の上方に形成された第3の拡散領域と、前記第2の拡散領域と絶縁膜を介して対向する制御電極と、を備え、前記第1の拡散領域と前記第2の拡散領域とは、前記制御電極に印加される電圧に応じて制御される電流の主経路を形成する。

(もっと読む)

横型半導体装置及びその製造方法

【課題】既存のCMOS製造工程に対して工程の追加や変更を行うことなく、素子に要求される耐圧に応じて横型半導体装置が有するLocos酸化膜を最適に制御することができる、横型半導体装置の製造方法を提供する。

【解決手段】半導体基板(100、101)上のLocos形成領域に、遮蔽部及び開口部が所定の幅及び間隔で設けられたパターン(113a、113b)を有するマスク(113)を形成する(工程3a、3b)。マスク(113)を用いた熱酸化処理を施してLocos形成領域を酸化させ、半導体基板(100、101)のドリフト領域上に厚さが異なる(115a、155b)Locos酸化膜(105a、105b)を同時に形成する(工程4a、4b)。

(もっと読む)

半導体装置の製造方法

【課題】良好な特性の確保、素子サイズの増加の回避、及び製造プロセスの簡素化を実現できる半導体装置の製造方法を提供する。

【解決手段】Si基板111の主面に、LOCOS酸化膜112bを含む酸化膜112を形成する工程と、Si基板111の主面の側に、ソース・ゲート形成領域113aとドレイン形成領域113bとを形成する工程と、レジスト116をマスクとして、Si基板111の主面の側のLOCOS酸化膜112bで覆われていないトレンチ114を通してイオン117注入を行い、イオン注入層118を形成する工程と、LOCOS酸化膜112b上及びソース・ゲート形成領域113a上を部分的に覆うようにゲート電極119を形成する工程とを有し、イオン注入層118のゲート電極119側の端部とゲート電極119のイオン注入層118側の端部との間に間隔121が存在するように、各工程を行う。

(もっと読む)

半導体装置及びその製造方法

【課題】プロセス条件の見直しを最小限に抑制しつつ電気的特性を向上させることができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置1は、半導体構造11の上面領域に形成された島状の絶縁膜20と、絶縁膜20の上面領域に配列された複数の凸状絶縁部23と、これら凸状絶縁部23と絶縁膜20とを被覆する層間絶縁膜26とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】 寄生ダイオードの逆回復時間を短縮でき、スイッチング損失の低減が図れるLDMOSトランジスタを低コストで提供する。

【解決手段】 LDMOSトランジスタT1が、p型半導体基板1内にp型ボディ領域2とp型埋め込み拡散領域3とn型ドリフト領域6を、ボディ領域2内にn型ソースコンタクト領域4とp型ボディコンタクト領域5を、ドリフト領域6内にn型ドレインコンタクト領域7を、ソースコンタクト領域7とドリフト領域6間のボディ領域2の上方にゲート絶縁膜8を、ゲート絶縁膜8上にゲート電極9を夫々備えて形成され、ドリフト領域6とボディ領域2は相互に接触し、埋め込み拡散領域3が、ボディ領域2の底面と接触するボディ領域2よりも深い位置に、半導体基板1の表面に平行な方向に、少なくともボディ領域2からドレインコンタクト領域7のボディ領域2から最も離間した遠方端の下方まで延在している。

(もっと読む)

半導体装置

【課題】横型DMOSの素子面積の増大を抑制し高耐圧化をはかる。

【解決手段】第1の半導体素子100Aは、第1半導体層12Aと、第2半導体層14Aと、第2半導体層に隣接する第3半導体層16Aと、第1絶縁層20Aと、第2半導体層の表面に選択的に設けられた第1ベース領域30Aと、第1ベース領域の表面に選択的に設けられた第1ソース領域32Aと、第1絶縁層の内部に設けられた第1ゲート電極40Aと、第1ベース領域の下に設けられ、第1半導体層の表面から第1ベース領域の側に延在する第1ドリフト層18Aと、第1ソース領域32Aに対向し、第1絶縁層20Aを挟んで第3半導体層16Aの表面に設けられた第1ドレイン領域34Aを有す。第1ドリフト層18Aの不純物元素の濃度は、第1半導体層12Aの不純物元素の濃度よりも低い。第1ドリフト層の不純物元素の濃度は、第2半導体層14Aの不純物元素の濃度よりも高い。

(もっと読む)

半導体装置及びその製造方法

【課題】トレンチ分離構造の上面の周縁部にディボットが形成されても、このディボットに起因するゲート絶縁膜の破壊を防止することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置1は、トレンチ分離構造20Bと、トレンチ分離構造20Bで区画される活性領域上に形成されたゲート絶縁膜30と、ゲート絶縁膜30の上面からトレンチ分離構造20Bの上面まで延在するゲート電極層31と、ゲート電極層31の両側に形成された第1及び第2の不純物拡散領域13D,13Sとを備える。ゲート電極層31は、ゲート絶縁膜30と第1の不純物拡散領域13Dとの間の領域に貫通孔31hを有し、貫通孔31hは、トレンチ分離構造20Bの上面の周縁部の直上に形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】不純物イオンの注入による悪影響を防止しつつ水平方向の耐圧を向上できる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、素子を構成し、電流が流れる一対の不純物領域が、半導体基板の第1主面の表層に形成されたものであり、水平方向の耐圧を確保するため、フィールドプレート33を有している。これに加えて、この半導体装置は、半導体基板の表面から、素子の電流経路となる第1不純物領域37および第2不純物領域38よりも深い所定の深さおいて、少なくとも第1不純物領域および第2不純物領域の間の領域に半導体基板と同一成分の非晶質層24を有する。この非晶質層は、単結晶および多結晶よりも高抵抗の層であり、擬似的なフィールドプレートとして機能する。そして、この非晶質層は、不活性元素のイオン注入により形成される。

(もっと読む)

トレンチ拡散領域を有する金属酸化物半導体デバイスおよびその形成方法

【課題】改善された高周波性能およびオン状態特性を可能にするMOSデバイスを提供すること。

【解決手段】MOSデバイスは、第1の伝導型の半導体層と、半導体層の上面に近接して半導体層中に形成された第2の伝導型の第1および第2のソース/ドレイン領域とを含む。第1および第2のソース/ドレイン領域は、互いに間隔を開けて配置されている。ゲートは、少なくとも部分的に第1のソース/ドレイン領域と第2のソース/ドレイン領域との間の半導体層の上に形成され、かつ半導体層から電気的に絶縁されている。第1および第2のソース/ドレイン領域のうちの少なくとも特定の1つは、半導体層とその特定のソース/ドレイン領域との間の接合の幅よりも実質的に大きな実効幅を有して形作られている。

(もっと読む)

半導体装置

【課題】素子面積を増加させることなく、高耐圧の半導体装置を実現させる。

【解決手段】第1方向に沿ったソース領域、ゲート電極を挟んでソース領域とは反対側に第1方向に沿ったドレイン領域、一部がゲート電極下面と対向しソース領域とドレイン領域との間に設けた絶縁体層、一部がゲート電極下面と対向し絶縁体層よりもソース領域側に設けたベース領域、一部が第2方向に第2長さを有してゲート電極下面と対向し、ベース領域よりも絶縁体層側に設けたドリフト領域、を有する素子活性領域部、ゲート絶縁膜の上に設けたゲート電極、ソース領域、一部がゲート電極下面と対向して設けた絶縁体層、一部がゲート電極下面と対向して絶縁体層よりもソース領域側に設けたベース領域、一部が第1方向に第2長さよりも短い第1の長さを有してゲート電極下面と対向してベース領域よりも絶縁体層側に設けたドリフト領域、を有する素子終端領域部と、を備える。

(もっと読む)

半導体装置

【課題】小型でコストが低い半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、導電形がp形のソース領域と、導電形がp形のドレイン領域と、前記ソース領域と前記ドレイン領域との間に設けられ、導電形がn形のチャネル領域と、前記チャネル領域上に設けられた下側ゲート絶縁膜と、前記下側ゲート絶縁膜上に設けられた下側ゲート電極と、前記下側ゲート電極上に設けられた上側ゲート絶縁膜と、前記上側ゲート絶縁膜上に設けられた上側ゲート電極と、前記下側ゲート電極と前記ソース領域との間に接続されたスイッチング素子と、を備える。

(もっと読む)

半導体装置

【課題】長さ方向がゲート長方向と平行なトレンチに形成されたゲート電極を有し、単位平面積当たり大きなゲート幅を有する高駆動能力横型のMOSトランジスタの駆動能力を、平面的な素子面積を増加させずに向上させる半導体装置を提供する。

【解決手段】半導体基板の表面に長さ方向がゲート長方向と平行なトレンチが形成された第1トレンチ領域013と、前記第1トレンチ領域の凹部底面と同一平面に前記第1トレンチ領域の長さ方向の両端に接して設けられた第2トレンチ領域014および第3トレンチ領域015と、トレンチ領域に形成された第2導電型のウェル領域005と、前記第1トレンチ領域に設けられたゲート絶縁膜004と、前記ゲート絶縁膜上に接して設けられたゲート電極003と、前記第1トレンチと前記第2トレンチ領域と前記第3トレンチ領域に前記ウェル領域より浅く設けられた第1導電型のソース領域とドレイン領域を有する半導体装置。

(もっと読む)

半導体装置

【課題】アバランシェ降伏電流が流れている状態において寄生トランジスタのターンオンを抑制することにより、十分なアバランシェ耐量を確保することのできる半導体装置を提供する。

【解決手段】基板の表面ではn型領域とベース領域とが隣接している。エミッタ/ソース領域はベース領域内でn型領域から離れている。ゲート絶縁膜はn型領域とエミッタ/ソース領域との間でベース領域を覆い、その上にゲート電極が形成されている。ドレイン領域とコレクタ領域とはn型領域内でベース領域から離れている。コレクタ接続領域はn型領域内で、ベース領域、ドレイン領域、及びコレクタ領域のいずれからも離れている。ドレイン電極はドレイン領域に接続されている。コレクタ電極はコレクタ領域とコレクタ接続領域とに接続されている。ゲートターンオフ状態でドレイン電極にアバランシェ降伏電流が流れるとき、コレクタ電極の電位がドレイン電極の電位よりも低い。

(もっと読む)

半導体装置

【課題】微細CMOSと中高耐圧MOSFETとの混載を前提とする集積回路(半導体装置)において、中高耐圧MOSFETのチャネル長やしきい値電圧のばらつきを抑制して、設計仕様どおりの安定した回路動作の実現や出力電流密度の向上を図ることができる技術を提供する。

【解決手段】本発明における特徴は、チャネル領域CHの幅(チャネル長)を小さくしたことにある。具体的には、ゲート電極Gと平面的に重なるチャネル領域CHの幅をLとし、ゲート電極Gの厚さをtとした場合、チャネル領域CHの幅Lが、ゲート電極Gの厚さtの1/5倍以上1倍以下になるようにチャネル領域CHを形成する。これにより、チャネル領域CHの幅Lを小さくすることができ、しきい値電圧のばらつきを小さくすることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】リセスの下部に形成され不純物の注入量が異なる複数の領域を備える電界緩和層(リサーフ層)を備える半導体装置において、製造工程数の増加を抑えつつ、ディッシングの発生を防止する。

【解決手段】半導体装置は、半導体素子の外周領域であるPウェル2の外縁部に形成されたP型のリサーフ層10を備える。リサーフ層10は、P型不純物が第1面密度で注入された第1リサーフ領域11と、第1リサーフ領域11の外側に配設され、P型不純物が第1面密度よりも小さい第2面密度で注入された第2リサーフ領域12と、第2リサーフ領域12の外側に配設され、P型不純物が第2面密度よりも小さい第3面密度で注入された第3リサーフ領域13とを含む。このうち第1リサーフ領域11および第3リサーフ領域13は、半導体層の上面に形成されたリセス11r,13rの下に形成される。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】携帯電話などに使用されるハイパワーアンプの出力段は、多数のLDMOSFETセルを集積し、通常、複数のLDMOSFETを構成するLDMOSFET部を有する。このLDMOSFETセルにおいては、裏面のソース電極と表面のソース領域との間の抵抗を低減するために、半導体基板に高濃度にボロンドープされたポリシリコンプラグが埋め込まれている。本願発明者らが、このポリシリコンプラグについて、検討したところによって、熱処理に起因してポリシリコンプラグの固相エピタキシャル成長により、ポリシリコンプラグが収縮し、それによってシリコン基板に歪が発生し、リーク不良等の原因となることが明らかとなった。

【解決手段】本願発明は、LDMOSFETを有する半導体集積回路装置において、半導体基板に埋め込まれたシリコン系導電プラグのボロン濃度が、固溶限界内に於いて、8.1x1020atom/cm3以上である。

(もっと読む)

1 - 20 / 541

[ Back to top ]