Fターム[5F140BA10]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 基板材料 (9,253) | 2−6族 (113)

Fターム[5F140BA10]に分類される特許

101 - 113 / 113

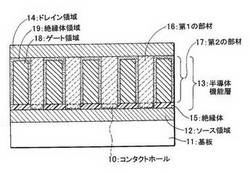

半導体素子およびその製造方法

【課題】素子の微細化が可能でスイッチング性能の高い立体構造を有する電界効果型トランジスタである半導体素子を提供する。

【解決手段】ソース領域と、前記ソース領域の上部に配置された半導体機能層と及び、前記半導体機能層の上部に配置されたドレイン領域とを備え、前記半導体機能層は、前記ソース領域に対してほぼ垂直に配列した、複数の柱状あるいは円筒状の半導体物質からなる第1の部材と、前記第1の部材を取り囲み、前記ソース領域と絶縁体を介して配置された第2の部材から構成され、前記第2の部材はゲート領域と、絶縁体領域とから構成されており、前記第1の部材の平均直径が1nm以上30nm以下であり、前記第1の部材の平均間隔が3nm以上50nm以下であり、前記半導体層の酸素を除く主成分がシリコン、またはゲルマニウム、またはシリコンとゲルマニウムの混合物のいずれかである半導体素子を用いる。

(もっと読む)

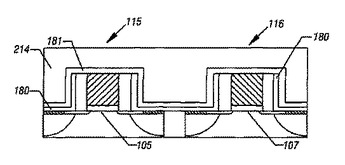

半導体構造およびそれを形成する方法(金属酸化物の付着を介して形成されたしきい電圧制御層を含む窒素含有電界効果トランジスタ・ゲート・スタック)

【課題】 ゲート誘電体とゲート電極との間にVt安定化層を含む半導体構造を提供することにある。

【解決手段】 Vt安定化層は、構造のしきい電圧およびフラットバンド電圧を目標値に安定化することができ、窒化金属酸化物または窒素なし金属酸化物を含み、Vt安定化層が窒素なし金属酸化物を含む条件で半導体基板またはゲート誘電体のうちの少なくとも一方が窒素を含む。また、本発明は、このような構造を形成する方法も提供する。

(もっと読む)

犠牲スペーサを利用して歪みチャネル電界効果トランジスタを製造するための構造体及び方法

【課題】 犠牲スペーサを利用して歪みチャネル電界効果トランジスタを製造するための構造体及び方法

【解決手段】 ゲート積層体(29)と、ゲート積層体(29)の側壁上に配置される1対の第1のスペーサ(32)と、ゲート積層体(29)の両側に配置され、それから第1の間隔を置かれる1対の半導体合金領域(39)とを含む電界効果トランジスタ(FET)(10)が提供される。FET(10)のソース及びドレイン領域(24)は少なくとも部分的に半導体合金領域(39)内に配置され、1対の第1のスペーサ(32)の対応するスペーサによってゲート積層体(29)から、第1の間隔とは異なり得る第2の間隔を置かれる。FET(10)はまた、第1のスペーサ(32)の上に配置される第2のスペーサ(34)と、少なくとも部分的に半導体合金領域(39)の上に重なるシリサイド領域(40)とを含むことができるが、ここでシリサイド領域(40)は第1及び第2のスペーサ(32、34)によってゲート積層体(29)から間隔を置かれる。

(もっと読む)

置換金属ゲート形成のための半導体構造の平坦化

窒化物および充填層を含む犠牲ゲート構造は、金属ゲート電極と置換される。金属ゲート電極は、充填層で被覆された窒化物層で再度被覆される。窒化物および充填層の置換によって、歪みが再導入され、エッチング停止層が提供される。  (もっと読む)

(もっと読む)

半導体デバイス製造のためのゲート材料

電子デバイスを形成する際、半導体層を予めドープして、ドーパント分布アニールをゲート画定前に行う。場合によっては、ゲートは金属から形成されている。したがって、続いて形成される浅いソースおよびドレインは、ゲートアニールステップの影響を受けない。  (もっと読む)

(もっと読む)

スピントランジスタ、プログラマブル論理回路および磁気メモリ

【課題】増幅機能を有するスピントランジスタを提供すること。

【解決手段】スピントランジスタ100は、半導体基板10と、半導体基板10上において第1方向に磁化された強磁性体で形成される第1導電層12と、半導体基板10上において第1方向とその第1方向に対して反平行の第2方向とのいずれか一方に磁化される強磁性体で形成された第2導電層14と、第1導電層12と第2導電層14の間に位置し、第1導電層12と第2導電層14との間で電子スピンを導くチャネル部と、チャネル部の上方に位置するゲート電極40と、第1導電層12および第2導電層14の少なくとも一方とチャネル部との間に位置するトンネルバリア膜11a,11bと、を備える。

(もっと読む)

MOS電界効果トランジスタ型量子ドット発光素子および受光素子、これらを利用した光電子集積チップおよびデータ処理装置

【課題】 MOS電界効果トランジスタ型量子ドット発光素子および受光素子の提供、MOS電界効果トランジスタ型量子ドット発光素子の製造方法の提供、かかる受発光素子を利用した光電子集積チップ、データ処理装置を提供することを目的とする。

【解決手段】 MOS電界効果トランジスタ型量子ドット発光素子は、半導体基板と、該半導体基板上に形成されたトンネルSiO2層と、該トンネルSiO2層上に形成されたSi殻内にGe核を内包した量子ドットと、該量子ドット上及び前記トンネルSiO2層上に形成されたコントロールSiO2層と、該コントロールSiO2層上に形成されたゲート電極層と、を有する。MOS電界効果トランジスタ型量子ドット発光素子は、半導体基板と、該半導体基板上に形成されたゲートSiO2層と、該ゲートSiO2層上に形成されたドープSi層、Ge層及びドープSi層を順次積層してなる積層ゲート電極層と、を有する。

(もっと読む)

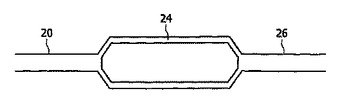

ナノスケールFET

トランジスタデバイスは、ソース領域、ドレイン領域、およびソース領域とドレイン領域の間のチャネル領域を有する連続リニアナノ構造体で形成される。ソース領域(20)とドレイン領域(26)はナノワイヤで形成され、チャネル領域(24)はナノチューブの形である。ソース領域とドレイン領域の間のチャネル領域における伝導を制御するためにチャネル領域(24)に隣接する絶縁ゲート(32)が提供される。  (もっと読む)

(もっと読む)

半導体装置及び製造方法

半導体(20)の周囲に下方のフィールド・プレート(32)及び任意選択の横のフィールド・プレート(34)を有する半導体装置が形成され、この場合、たとえば、パワーFET又は他のトランジスタ或いはダイオード・タイプなどの装置が形成される。半導体装置は、絶縁側壁を有するトレンチを形成し、つながっているトレンチの底部にキャビティ(26)をエッチングし、次いで、トレンチを導体(30)で充填することによって製造される。  (もっと読む)

(もっと読む)

粒状半導体材料を有する応力半導体構造

【課題】 チャネル移動度の向上を利用して性能を改善した半導体デバイス構造およびその製造方法を提供する。

【解決手段】 半導体デバイス構造を製造する方法であって、基板を設けるステップと、基板上に電極を設けるステップと、電極内に開口を有するくぼみを形成するステップと、くぼみ内に細粒半導体材料を配置するステップと、開口を覆ってくぼみ内に細粒半導体材料を閉じこめるステップと、上述のステップの結果として得られる構造をアニーリングするステップと、

を含む。

(もっと読む)

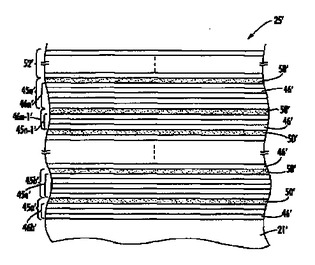

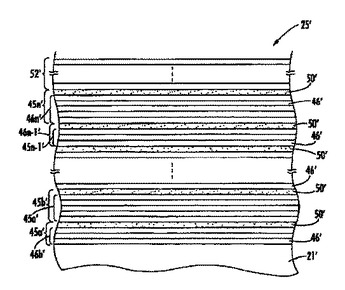

バンド設計超格子を有する半導体装置

半導体装置は、複数の積層された層群を有する超格子を有する。また装置は、電荷キャリアが積層された層群と平行な方向に超格子を通って輸送される領域を有する。超格子の各層群は、基本半導体部分を定形する複数の積層された基本半導体分子層と、該基本半導体部分上のエネルギーバンド調整層と、を有する。さらにエネルギーバンド調整層は、少なくとも一つの非半導体分子層を有し、この層は、連接する基本半導体部分の結晶格子内に閉じ込められる。従って超格子は、平行な方向において、エネルギーバンド調整層がない場合に比べて大きな電荷キャリア移動度を有する。

(もっと読む)

(もっと読む)

バンド設計超格子を有するMOSFETを有する半導体装置

半導体装置は、基板と、該基板に隣接する少なくとも一つのMOSFETとを有する。MOSFETは、超格子チャンネルを有し、該超格子チャンネルは、複数の積層された層群を有する。またMOSFETは、超格子チャンネルと水平方向に隣接するソースおよびドレイン領域と、超格子上に設置されたゲートと、を有し、超格子チャンネルを通って、積層された層群と平行な方向に電荷キャリアの輸送が生じる。超格子チャンネルの各層群は、基本半導体部分を定形する複数の積層された基本半導体分子層と、該基本半導体部分上のエネルギーバンド調整層と、を有する。エネルギーバンド調整層は、基本半導体部分に隣接する結晶格子内に取り込まれた、少なくとも一つの非半導体分子層を有し、超格子チャンネルは、平行な方向において、エネルギーバンド調整層がない場合に比べて大きな電荷キャリア移動度を有する。

(もっと読む)

(もっと読む)

バンド設計超格子を有する半導体装置

半導体装置は、複数の積層された層群を有する超格子を有する。超格子の各層群は、基本半導体部分を定形する複数の積層された基本半導体分子層と、該基本半導体部分上のエネルギーバンド調整層と、を有する。さらにエネルギーバンド調整層は、少なくとも一つの非半導体分子層を有し、この層は、連接する基本半導体部分の結晶格子内に閉じ込められる。従って超格子は、平行な方向において、エネルギーバンド調整層がない場合に比べて大きな電荷キャリア移動度を有する。  (もっと読む)

(もっと読む)

101 - 113 / 113

[ Back to top ]