Fターム[5F140BA10]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 基板材料 (9,253) | 2−6族 (113)

Fターム[5F140BA10]に分類される特許

81 - 100 / 113

半導体装置

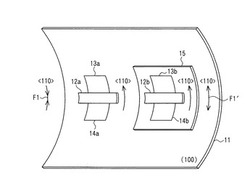

【課題】 半導体チップを折り曲げることにより、Pチャネル電界効果型トランジスタとNチャネル電界効果型トランジスタの移動度を同時に向上させる。

【解決手段】 <110>方向に沿って凹状に折り曲げられた(100)基板11には、<110>方向に沿って(100)基板11の折り曲げ方向と平行にチャネルが配置されたPチャネル電界効果型トランジスタが形成されるとともに、<110>方向に沿って(100)基板11の折り曲げ方向と平行にチャネルが配置されたNチャネル電界効果型トランジスタが形成され、Nチャネル電界効果型トランジスタ上には、(100)基板11の折り曲げによる圧縮応力よりも大きな引っ張り応力F1´を印加するゲートキャップ膜15が形成されている。

(もっと読む)

半導体装置

【課題】 曲げによる応力が加わった場合においても、トランジスタの特性の変動を抑制できるようにする。

【解決手段】 電界効果型トランジスタ上には、電界効果型トランジスタに引っ張り応力F1´を印加するゲートキャップ膜15が形成され、ゲートキャップ膜15に起因する応力は、半導体基板11の折り曲げによってトランジスタに印加される応力よりも大きくする。

(もっと読む)

半導体装置

【課題】 半導体チップを折り曲げることにより、Pチャネル電界効果型トランジスタとNチャネル電界効果型トランジスタの移動度を同時に向上させる。

【解決手段】 <110>方向に沿って凸状に折り曲げられた(100)基板11に、<110>方向に沿って(100)基板11の折り曲げ方向と直角にチャネルが配置されたPチャネル電界効果型トランジスタを形成するとともに、<110>方向に沿って(100)基板11の折り曲げ方向と平行にチャネルが配置されたNチャネル電界効果型トランジスタを形成する。

(もっと読む)

半導体装置及びその製造方法

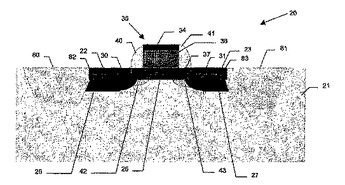

【課題】 セルフヒート効果を低減することができ、基板浮遊効果も解消できるようにした半導体装置及びその製造方法を提供する。

【解決手段】 Si基板1上のSi層10にゲート酸化膜21を介して形成されたゲート電極23と、ゲート電極23を挟んでSi層10に形成されたソース層27a及びドレイン層27bと、を含んで構成されるSDONトランジスタ100を有し、ソース層27aとSi基板1との間及び、ドレイン層27bとSi基板1との間にはそれぞれ空洞部15が存在し、且つゲート電極23下のSi層10とSi基板1との間には空洞部が存在していないことを特徴とするものである。ゲート電極23下のSi層10がSi基板1とつながっているので、SONトランジスタと比べて、セルフヒート効果を低減することが可能である。また、ボディ電位はSi基板1に固定されるので、基板浮遊効果を解消することができる。

(もっと読む)

半導体装置の製造方法及び、半導体装置

【課題】 特殊な製造装置は不要で、製造時の結晶欠陥の発生を抑えたDSOIトランジスタを有する半導体装置の製造方法及び、半導体装置を提供する。

【解決手段】 まず始めに、Si基板1上にSiGe層3を形成し、SiGe層3のうちのソース形成領域とドレイン形成領域とに挟まれた部分をエッチングして取り除き、トレンチを形成する。次に、このトレンチ内が埋め込まれ且つSiGe層3上が覆われるように、Si基板1上にSi層10を形成する。そして、トランジスタ形成領域の外側にあるSi層10と、当該外側にあるSiGe層3とを順次エッチングして取り除くことにより、トランジスタ形成領域の周囲に沿ってSiGe層3の側面を露出させる。その後、SiGe層3をその露出した側面からエッチングして取り除くことにより、トランジスタ形成領域のSi層10下に空洞部15を形成し、続いて、この空洞部15内にSiO2膜17を形成する。

(もっと読む)

代替活性エリア材料の集積回路への組み込みのための解決策

結晶半導体基板上に代替材料のエリアを形成する方法、並びにこの方法により形成された構造。このような代替材料のエリアは、MOSFET又は電子デバイス若しくは光電子デバイスにおける活性エリアとしての使用に適している。  (もっと読む)

(もっと読む)

少なくとも一対の空間的に隔てられた応力領域間に歪み超格子を含む半導体デバイス、及びその製造方法

半導体デバイスは、少なくとも一対の空間的に隔てられた応力領域(227、228)と、この少なくとも一対の空間的に隔てられた応力領域間の、積層された複数の層群を有する歪み超格子層(225)とを含んでいる。歪み超格子層の各層群は、ベース半導体部分を画成する積層された複数のベース半導体モノレイヤーと、隣接し合うベース半導体部分の結晶格子内に拘束された少なくとも1つの非半導体モノレイヤーとを含んでいる。  (もっと読む)

(もっと読む)

歪み超格子とその上の応力層とを含む半導体デバイス、及びその製造方法

半導体デバイスは、積層された複数の層群を有する歪み超格子層(325)、及び歪み超格子層の上方の応力層を含んでいる。歪み超格子層の各層群は、ベース半導体部分を画成する積層された複数のベース半導体モノレイヤーと、隣接し合うベース半導体部分の結晶格子内に拘束された少なくとも1つの非半導体モノレイヤーとを含んでいる。  (もっと読む)

(もっと読む)

超格子を間に有するシャロー・トレンチ・アイソレーション(STI)領域を含む半導体デバイス、及びその製造方法

半導体デバイスは、半導体基板と、基板内の複数のシャロー・トレンチ・アイソレーション(STI)領域とを含んでいる。より具体的には、STI領域の少なくとも一部はディボットを含んでいる。半導体デバイスは更に、隣接し合うSTI領域間それぞれの超格子と、ディボット内それぞれの非単結晶の梁部とを含んでいる。

(もっと読む)

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 チャネルポテンシャルの支配力の低下を抑制しつつ、ゲート長を短縮できるようにする。

【解決手段】 ゲート電極15の一端からオフセット長XSだけ隔ててソース層18aを形成するとともに、ゲート電極15の他端からオフセット長XDだけ隔ててドレイン層18bを形成し、ソース層18a側のオフセット長XSは、ドレイン層18b側のオフセット長XDよりも短くするとともに、サイドウォール16a、16bの長さは、オフセット長XS、XDにそれぞれ対応するように設定する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 接合リークを抑制しつつ、ソース/ドレイン層の低抵抗化を図るとともに、ショートチャネル効果を抑制する。

【解決手段】 ゲート電極15の一方の側に絶縁層12に底面が接する合金層からなるソース層18aを配置し、単結晶半導体層13の結晶方位面20aに沿ってチャネル領域17に対する接合面を形成し、ゲート電極15の他方の側に絶縁層12に底面が接する合金層からなるドレイン層18bを配置し、単結晶半導体層13の結晶方位面20bに沿ってチャネル領域17に対する接合面を形成し、ソース層18aを構成する合金層と単結晶半導体層13との界面には、結晶方位面20aに沿うようにして自己整合的に形成された不純物導入層19aを設け、ドレイン層18bを構成する合金層と単結晶半導体層13との界面には、結晶方位面20bに沿うようにして自己整合的に形成された不純物導入層19bを設ける。

(もっと読む)

実質的にドーピングされていない層からなる少なくとも1の群を有する超格子を含む半導体素子

半導体素子は超格子を有する。つまりその超格子は、複数の層からなる複数の積層された群を有する。その超格子の各群は、基本となる半導体部分を画定する複数の積層された基本となる半導体分子層、及びその上にエネルギーバンド修正層を有して良い。しかもエネルギーバンド修正層は、隣接する基本となる半導体部分の結晶格子内部に束縛された少なくとも1層の非半導体分子層を有して良い。超格子に含まれる複数の層からなる群のうちの少なくとも1は、実質的にドーピングされなくて良い。

(もっと読む)

(もっと読む)

高性能CMOS用途のためのHfドープされた極薄の酸窒化シリコン膜及び製造方法

【課題】 高性能CMOS用途のためのHfドープされた極薄酸窒化シリコン膜及びその製造方法を提供すること。

【解決手段】 半導体構造体と、これを形成する方法であって、この方法は、ベース・ゲート誘電体層(53)の上部に安定した拡散制御材料の均一なバッファ層を形成するステップと、次いで、遷移金属原子のソースを含有する均一な層を形成するステップと、次いで、この構造体をアニールして、ソースから遷移金属原子を、拡散制御材料を通してベース・ゲート誘電体層(53)に拡散させるステップと、を含む。

(もっと読む)

半導体接合を画定する領域を有する超格子を有する半導体素子

半導体素子は、各々が複数の層からなる複数の群を積層された状態で有する超格子を有して良い。その超格子の複数の層からなる群の各々は、基礎となる半導体部分を画定する、複数の積層された基礎となる半導体分子層、及びその上にエネルギーバンド修正層を有して良い。そのエネルギーバンド修正層は、隣接する基礎となる半導体部分の結晶格子の内部に束縛された少なくとも1の非半導体分子層を有して良い。その超格子は、その内部に、少なくとも1の半導体接合を画定する少なくとも1対の相反する符号の電荷がドーピングされた領域をさらに有して良い。

(もっと読む)

(もっと読む)

半導体装置、および半導体装置の作製方法

【課題】フッ素原子を分子中に含むガスでは、SiN膜のエッチングが等方的に進行するため、サイドウォールの幅が小さくなり、LDD領域の幅を大きくすることが困難であった。

【解決手段】ゲート電極上に窒化珪素膜を形成し、エッチングガスとして臭化水素ガスを主に用い、ICP(誘導結合型プラズマ)法などのエッチング方法により、窒化珪素膜のうちゲート電極上の部分と基板表面部のみを除去し、同時にゲート電極の側面部のみに窒化珪素膜を残す。

(もっと読む)

シャロートレンチアイソレーションプロセス

トランジスタとトレンチ構造とを含む構造に関し、トレンチ構造は、トランジスタのチャネル領域内に歪みの一部のみを導入する。  (もっと読む)

(もっと読む)

高性能FETデバイス及び方法

【課題】半導体FETデバイスの機能及び高周波性能を改善するために用いることができる、ゲート電圧バイアス供給回路素子を備えたエピタキシャル積層構造を提供する。

【解決手段】半導体電界効果トランジスタ(FET)デバイスの性能を改善するためのゲート電圧バイアス供給回路素子を備えたエピタキシャル積層構造は、基板と、該基板上にエピタキシャルに成長したn型またはp型の第1の層の半導体膜であって、基板と第1の層膜との間にバッファ層が存在する可能性がある第1の層の半導体膜と、第1の半導体層上にエピタキシャルに成長した活性半導体層であって、活性層の導電型が第1の半導体層の導電型と反対であり、またFETを形成するのに十分なゲート、ドレイン、ソースへの電気コンタクトを備えたゲート領域及びドレイン領域及びソース領域を有する活性半導体層と、基板または第1の半導体層上の電気コンタクトと、デバイス性能を向上させるのに十分な電圧極性及び大きさで、ゲートコンタクト及び基板または第1の半導体層に電気的に接続されたゲート電圧バイアス供給回路素子と、からなる構造を利用する。  (もっと読む)

(もっと読む)

高い誘電率のSiO2ゲート積層体上に熱的に安定したp型金属炭化物としてTiCを製造する方法

【課題】

高誘電率のSiO2ゲート積層体上に熱的に安定したp型金属炭化物としてTiCを製造する方法を提供する。

【解決手段】

本発明の金属化合物は、TiCを含み、約4.75乃至約5.3eV、望ましくは、約5eVの仕事関数を有し且つ高誘電率の誘電体および界面層を含むゲート積層体上で熱的に安定する。更に、そのTiC金属化合物は、非常に意欲的な等価酸化膜厚(EOT)およびp型金属酸化物半導体(pMOS)装置における14Åよりも小さい反転層厚へのスケーリングを可能にする1000℃においても非常に効率的な酸素拡散バリアである。

(もっと読む)

n−FET用途のためのHfSiN金属を形成する方法

【課題】 高k誘電体及び界面層を含むゲート・スタック上に、熱的に安定した新しい金属化合物を提供すること。

【解決手段】 高k誘電体及び界面層を含むゲート・スタック上に、約4.0eVから約4.5eVまで、好ましくは約4.3eVの仕事関数を有する、熱的に安定したn型金属であるHfSiNを含む金属化合物である。さらに、(約1000℃のオーダーの)高温でHfSiN/高k誘電体/界面層のスタックをアニールした後、界面層が減少され、よって、ゲート・スタックは、TaSiNを用いて達成することができない、非常に薄い等価酸化物厚(伝統的には、12Å)をもたらす。

(もっと読む)

半導体装置の作製方法

【課題】材料の利用効率を向上させ、作製工程を簡略化した半導体装置の作製技術を提供することを目的とする。また、それらの半導体装置を構成する配線等のパターンを、所望の形状で密着性よく形成できる技術を提供することも目的とする。

【解決手段】第1の導電層上に第1の絶縁層を形成し、第1の絶縁層上に第2の絶縁層を形成し、第2の絶縁層上に第1の開口を有する第1のマスク層を形成し、第1の絶縁層及び第2の絶縁層をエッチングすることにより、第1の導電層に達する第1の開口部を形成し、第1のマスク層除去後、第1の開口よりも開口面積が広い第2の開口を有し、且つ、導電性材料を含む組成物に対してぬれ性の低い第2のマスク層を第2の絶縁層上に形成し、第1の絶縁層上面の一部が露出するように第2の絶縁層をエッチングし、第2の開口部を形成し、第1の開口部及び第2の開口部に導電性材料を含む組成物を充填し、第2の導電層を形成する。

(もっと読む)

81 - 100 / 113

[ Back to top ]